题目:

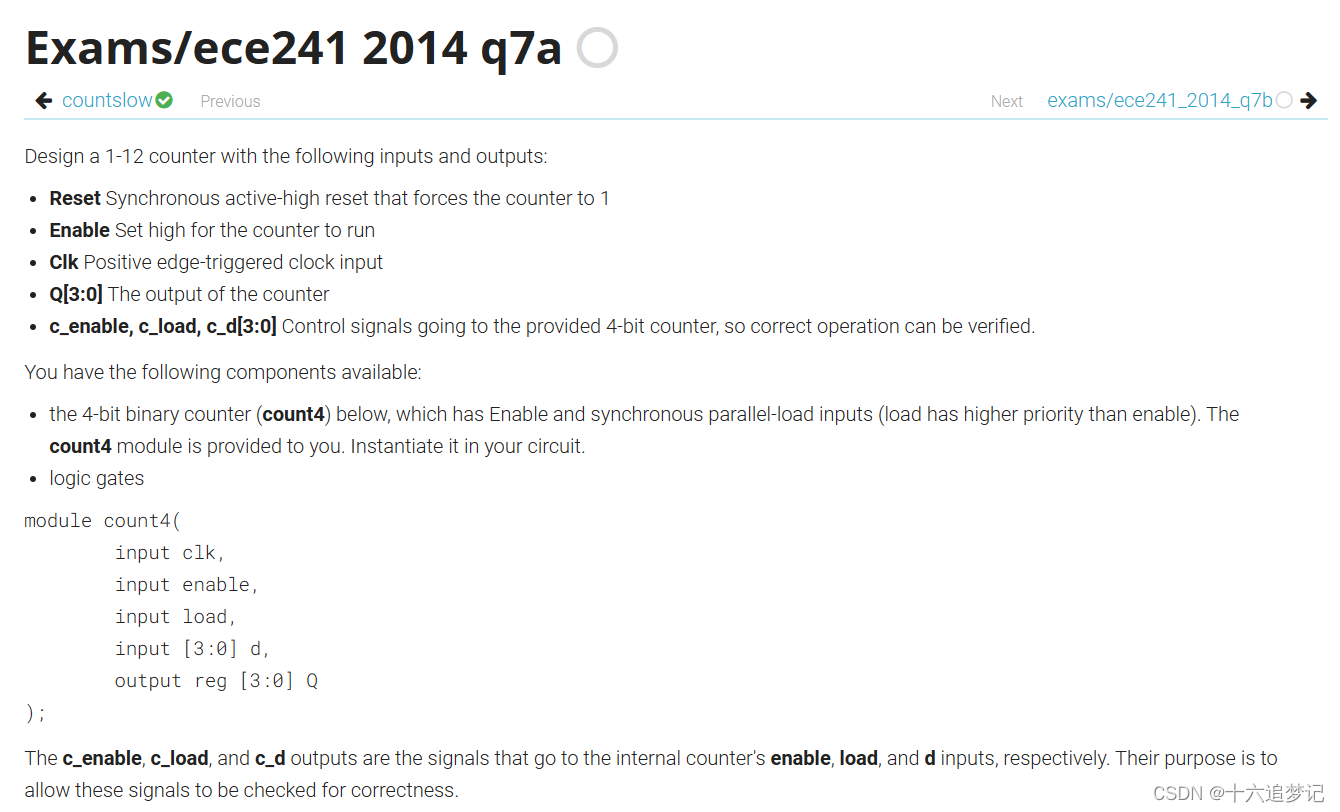

Design a 1-12 counter with the following inputs and outputs:

Reset Synchronous active-high reset that forces the counter to 1

Enable Set high for the counter to run

Clk Positive edge-triggered clock input

Q[3:0] The output of the counter

c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

logic gates

解题:

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

); //

assign c_enable=enable;

assign c_load=reset || ((Q==12)&enable);

assign c_d=1;

count4 the_counter (

.clk(clk),

.enable(c_enable),

.load(c_load),

.d(c_d),

.Q(Q)

);

endmodule

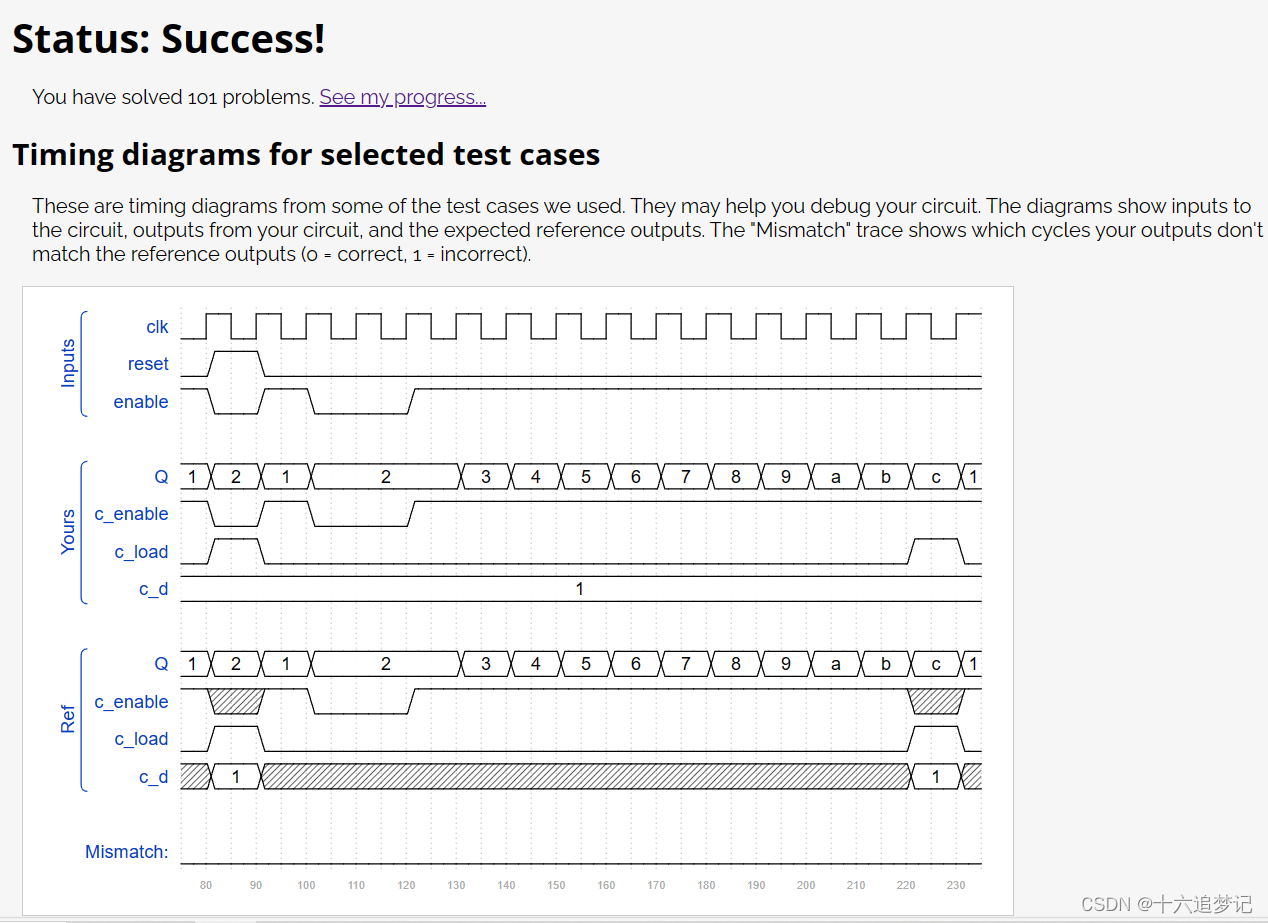

结果正确

本题为1-12计数器,考察函数例化结合计数器的编程。

2916

2916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?