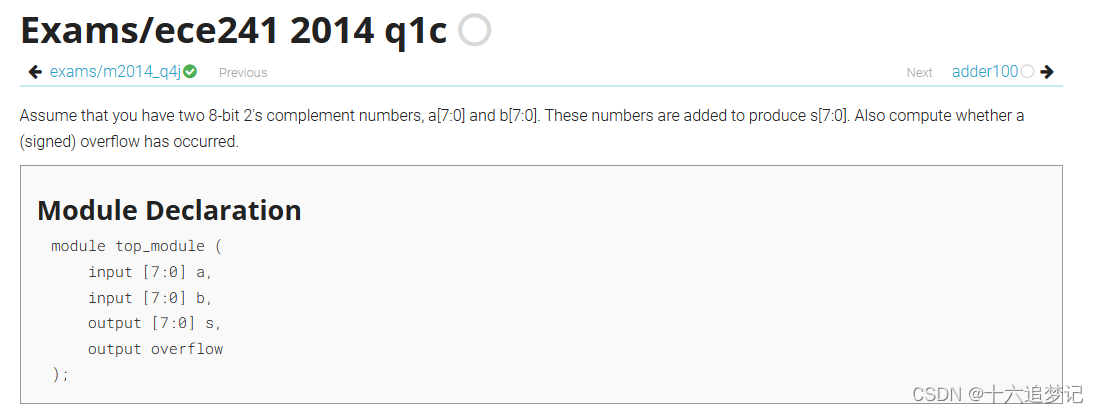

题目:Assume that you have two 8-bit 2’s complement numbers, a[7:0] and b[7:0]. These numbers are added to produce s[7:0]. Also compute whether a (signed) overflow has occurred.

解题:

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s=a+b;

assign overflow=(~a[7]&~b[7]&s[7])|(a[7]&b[7]&~s[7]);

// assign s = ...

// assign overflow = ...

endmodule

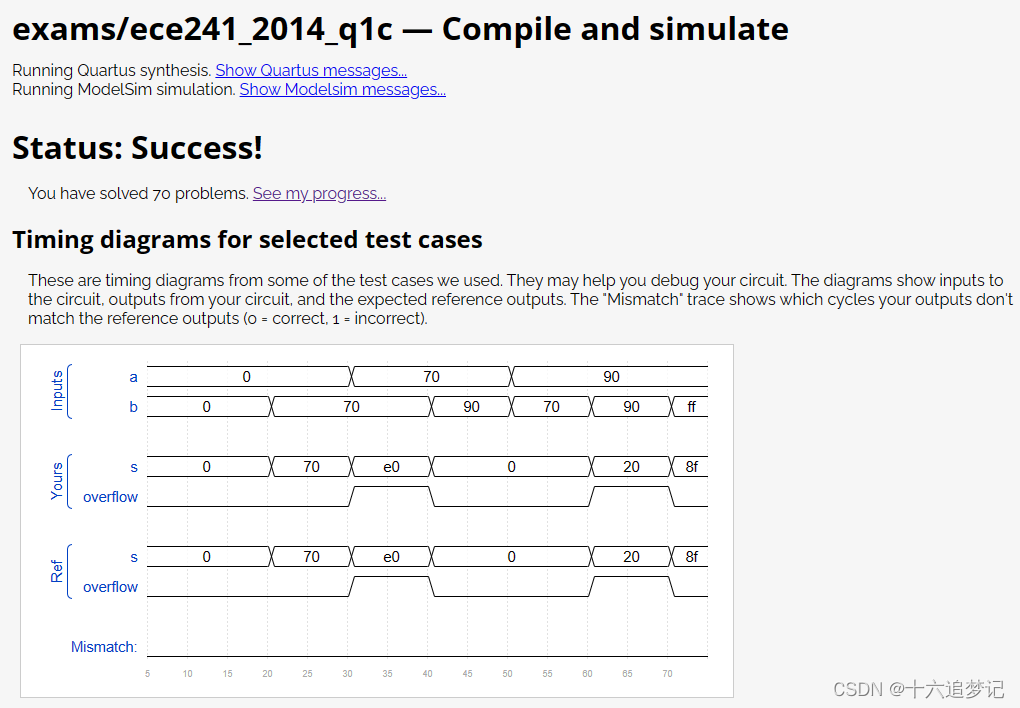

结果正确:

知识点补充:

~a[7] && ~b[7] && s[7]:这表示在进行加法运算时,如果两个操作数 a 和 b 的最高位(即第7位)都为0(表示正数),而结果 s 的最高位为1(表示负数),那么就发生了正正相加的符号溢出。这种情况下,因为加法的两个正数相加却得到了负数的结果,说明结果超出了能够用这样的位表示的范围,即发生了溢出。

a[7] && b[7] && ~s[7]:这表示在进行加法运算时,如果两个操作数 a 和 b 的最高位(即第7位)都为1(表示负数),而结果 s 的最高位为0(表示正数),那么就发生了负负相加的符号溢出。这种情况下,因为加法的两个负数相加却得到了正数的结果,说明结果超出了能够用这样的位表示的范围,即发生了溢出。

1980

1980

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?