目录

介绍

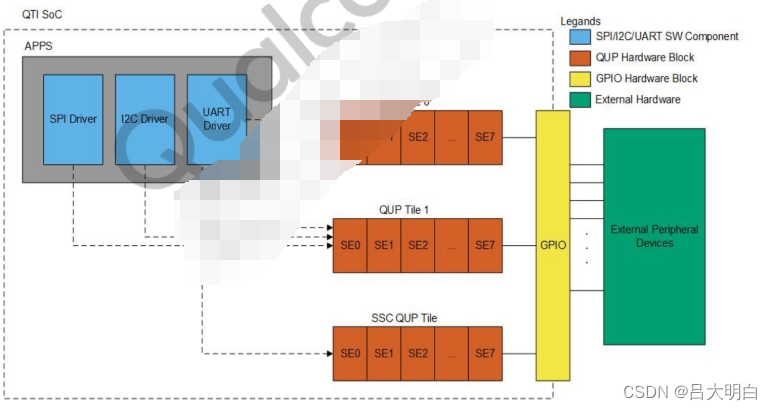

高通统一的外设(Qualcomm Universal Peripheral,QUP)QUP v3是一个可编程模块,支持多种串行接口,如UART、SPI、I2C和I3C。它支持从系统中的多个硬件实体进行访问。每个实体都有自己的执行环境(EE)、一个单独的地址空间和一条中断线。

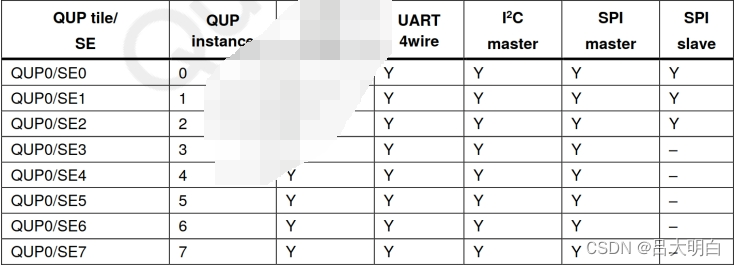

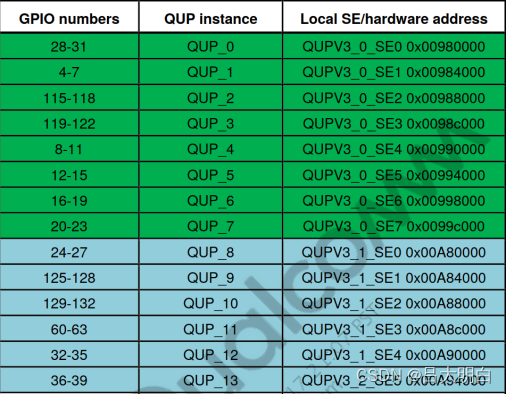

单个QUP v3模块使用其内部串行引擎(SE)/QUP提供多达八个串行接口。每个接口支持的协议由加载到SE的固件确定。这是通过修改TZ中的QUPAC_Access文件以加载所需协议(I2C或SPI或UART)来执行的。下表提供了SA8155 QUP Tile 0 SE可用协议的示例:

QUP v3的主要特性如下:

- 用于串行协议的单核心

- 取代了 BAM 低速外设 (BLSP) 传统核心

- 可编程的核心

QUP分为nouth、south等module。共有20个QUP

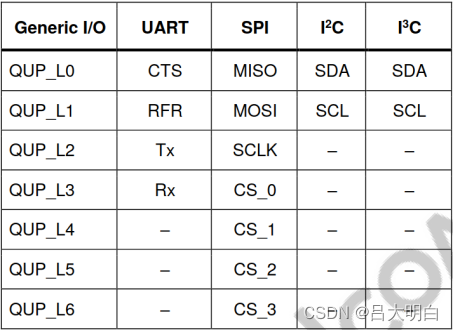

每个QUP有七个I/O通道,编号从0到6,支持下图列出的任务。一次只能在一个QUP引擎中选择一个协议。例如,不支持同时使用UART和I2C功能。

Configuration files

1. GPI configuration:

\trustzone_images\core\settings\hwengines\gpi\v2\config\SDM855\gpi_tz_855.c

2. TZ QUP configuration:

\trustzone_images\core\settings\buses\qup_accesscontrol\qupv3\config\855\QUPAC_Access.c

3. SPI configuration:

\trustzone_images\core\settings\buses\spi\qupv3\config\sdm855\tz\spi_devcfg.c

例如,SA8155 QUP访问表位于:

\trustzone_images\core\settings\buses\qup_accesscontrol\qupv3\config\855\QUPAC_Access.c

GPIO pads (管脚)

*一块电路板上面的芯片,都是有很多引脚和板子相连的,这些引脚就是接到了pad上,pad又接到了芯片内部的逻辑上

GPIO pads 根据协议为每个QUP SE分配功能。每个QUP SE最多可拥有7个GPIO pads。下表说明了pad的枚举如何与基于协议的功能相关:

根据GPIO pads 的功能,需配置以下参数:

- 功率强度表示允许流动的最大电流

- 2 mA

- 4 mA

- 8 mA

- 16 mA

- Pin方向

- 输入–接收信号

- 输出–发送输出信号

- Pad布线定义了电阻器如何连接到GPIO pad

- Pull up

- Pull down

- NO pull

- 函数值定义GPIO pad 所有权

- 0–代表HLOS软件的所有权

- 非零值表示所有其他外围设备,如QUP、eMAC等,并且特定于每个GPIO。

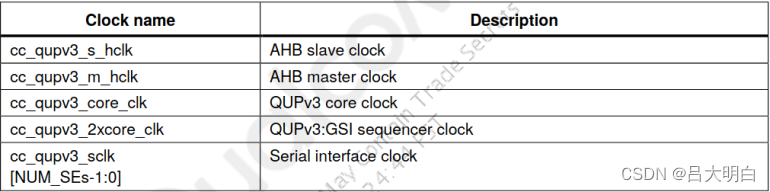

QUP SE clocks

QUP SE操作取决于以下时钟

时钟命名基于QUP索引和SE索引:

- AHB主时钟(AHB master clock)驱动SE的主部分,需要在所有协议中启用。主时钟对于每个QUP内的所有SE是通用的。时钟的命名格式为:

- gcc_qupv3_wrap_<QUP Tile index>_m_ahb_clk for top level QUP

- scc_qupv3_m_hclk_clk for SSC QUP (there is only one tile)

- AHB从属时(AHB slave clock)钟驱动SE的从属部分,仅需要为UART协议启用。每个QUP Tile内的所有SE共用从时钟。时钟的命名格式为:

- gcc_qupv3_wrap_<QUP Tile index>_s_ahb_clk for top level QUP

- scc_qupv3_s_hclk_clk for SSC QUP for SSC QUP (there is only one tile)

- QUP核心引擎需要AHB核心时钟(AHB core clock),并且需要在所有协议中启用。每个QUP瓦片内的所有SE共用核心时钟。时钟的命名格式如下:

- gcc_qupv3_wrap<QUP Tile index>_core_clk for top level QUP

- scc_qupv3_core_clk for SSC QUP (there is only one tile)

- QUP核心引擎需要AHB GSI时钟(AHB GSI clock),并且需要在所有协议中启用该时钟。GSI时钟对每个QUP tile内的所有SE通用。时钟的命名格式为:

- gcc_qupv3_wrap<QUP Tile index>_core_2x_clk for top level QUP

- scc_qupv3_2xcore_clk for SSC QUP (there is only one tile)

- 串行接口时钟(Serial interface clock)指定给每个SE,需要在所有协议中启用。时钟的命名格式为:

- gcc_qupv3_wrap<QUP Tile index>_s<Serial Engine Index>_clk for top level

- QUP Serial Engine scc_qupv3_ se<Serial Engine Index>_clk for SSC QUP (there is only one tile)

The following example shows the parameters to be enabled:

- QUP tile 1, SE 2 for SPI:

- gcc_qupv3_wrap_1_m_ahb_clk

- gcc_qupv3_wrap1_core_clk

- gcc_qupv3_wrap1_core_2x_clk

- gcc_qupv3_wrap1_se2_cl

Configure HLOS for I2C

HLOS I2C配置为驱动程序和服务提供外围设备支持和软件配置。I2C配置文件是SOC特定的,位于QNX HLOS build:

<repo.location>\qnx_ap\boards\core\dalconfig\adp_star_sda<soc_ID>\config\i2c_props_....xml

I2C属性文件的内容格式如下:

<global_def>

/* dev name */

<var_seq name="i2c_dev_1_name" type=DALPROP_DATA_TYPE_STRING>/dev/i2c1</var_seq>

<var_seq name="i2c_dev_2_name" type=DALPROP_DATA_TYPE_STRING>/dev/i2c2</var_seq>

/* bam/dma name */

<var_seq name="dev_bam_0_name" type=DALPROP_DATA_TYPE_STRING>/dev/bam0</var_seq>

/* res name */

<var_seq name="i2c_res_1_name" type=DALPROP_DATA_TYPE_STRING>/devcfg/i2c/1</var_seq>

<var_seq name="i2c_res_2_name" type=DALPROP_DATA_TYPE_STRING>/devcfg/i2c/2</var_seq>

/* core name */

<var_seq name="i2c_core_1_name" type=DALPROP_DATA_TYPE_STRING>I2C_CORE_1</var_seq>

<var_seq name="i2c_core_2_name" type=DALPROP_DATA_TYPE_STRING>I2C_CORE_2</var_seq>

/* i2c1 clocks */

<var_seq name="gcc_qupv3_wrap0_master_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap_0_m_ahb_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_core_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_core_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_gsi_sequencer_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_core_2x_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_s_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap_0_s_ahb_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_4_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s4_clk</var_seq>

</global_def>

<device id=DALDEVICEID_I2C_DEVICE_1>

<props name="I2C_ENABLED" type=DALPROP_ATTR_TYPE_UINT32> 1 </props>

<props name="INTR_BASED" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="PM_DISABLE" type=DALPROP_ATTR_TYPE_UINT32> 1 </props>

<props name="QUP_QGIC_IRQ" type=DALPROP_ATTR_TYPE_UINT32> 637 </props>

<props name="IRQ_TRIG_CFG" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="CLK_RATE_KHZ" type=DALPROP_ATTR_TYPE_UINT32> 19200 </props>

<props name="DEV_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> i2c_dev_1_name </props>

<props name="BAM_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> dev_bam_0_name </props>

<props name="RES_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> i2c_res_1_name </props>

<props name="CORE_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> i2c_core_1_name </props>

<props name="BLK_PHY_ADDR" type=DALPROP_ATTR_TYPE_UINT32> 0x890000 </props>

<props name="BLK_SIZE" type=DALPROP_ATTR_TYPE_UINT32> 0x1000 </props>

<props name="BAM_ENABLED" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="BAM_BLK_ADDR" type=DALPROP_ATTR_TYPE_UINT32> 0x7544000 </props>

<props name="BAM_IRQ_NUM" type=DALPROP_ATTR_TYPE_UINT32> 270 </props>

<props name="BAM_THRESHOLD" type=DALPROP_ATTR_TYPE_UINT32> 1024 </props>

<props name="BAM_IN_PIPE" type=DALPROP_ATTR_TYPE_UINT32> 13 </props>

<props name="BAM_OUT_PIPE" type=DALPROP_ATTR_TYPE_UINT32> 12 </props>

<props name="CLOCK_MASTER_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> gcc_qupv3_wrap0_master_clock_name </props>

<props name="CLOCK_SEC_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> gcc_qupv3_wrap0_s_clock_name </props>

<props name="CLOCK_SE_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> gcc_qupv3_wrap0_serial_engine_4_clock_name </props>

<props name="CLOCK_CORE_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> gcc_qupv3_wrap0_core_clock_name </props>

<props name="CLOCK_GSI_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR> gcc_qupv3_wrap0_gsi_sequencer_clock_name </props>

</device>配置XML文件由两部分组成:

- 标记为Global_def的全局定义,包含QUP SE名称和QUP配置中使用的时钟的全局名称。讨论了时钟名称及其与QUP SE的关系。该示例显示,需要在globa定义部分中列出所有相关时钟.

- 标记为device的设备数据,包含使用SPI协议启用和初始化QUP SE所需的所有详细信息。每个设备都需要以下财产:

- ID--确定I2C外围设备的DAL标识。ID枚举为:DALDEVICEID_I2C_DEV_1~12,最多可配置12个I2C外围设备。一旦QUP初始化,HLOS将创建应用程序使用的节点。例如,如果DALDEVICEID_I2C_DEV_3外设已启用,则将创建相应的/DEV/i2c3-DEV节点以与该外设通信。

- I2C_ENABLED--将外围设备设置为启用(设置属性值1)或禁用(将属性值设置为0)

- INTR_BASED--默认值为0

- PM_DISABLE--定义LPM模式是禁用(设置属性值为1)还是启用(设置值为0)(一般为1)

- CLK_RATE_KHZ--以KHZ为单位定义时钟基准频率。默认值为19200

- DEV_NAME--全局部分中定义的I2C外围设备名称

- BLK_PHY_ADDR--定义QUP SE基地址

- BLK_SIZE--定义始终设置为0x1000的QUIP寄存器区域的映射大小

- BAM_ENABLED--定义I2 C外围设备是在FIFO模式(设置为0)还是DMA模式(设置属性值为1)下工作

- CLOCK_MASTER_NAME--全局部分中定义的主时钟名称

- CLOCK_CORE_NAME--全局部分中定义的核心时钟名称

- CLOCK_GSI_NAME--全局部分中定义的核心时钟名称

- CLOCK_SE_NAME--全局部分中定义的SE时钟名称

- HIP_BLOCK_OFFSET--始终默认值为0

- QUP_BLOCK_SIZE--定义QUP SE注册表区域大小,并始终设置为0x4000

- CHIP_PERIPH_SS_BASE--定义QUP SE基地址

- CHIP_QGIC_IRQ--定义服务协议事件的QUP SE中断号

- QUP_BASE_FREQ_KHZ--定义QUP SE基本时钟频率,单位为KHZ

Configure HLOS for SPI

HLOS SPI配置为驱动程序和服务提供外围设备启用和软件配置。SPI配置文件是SOC特定的,位于QNX HLOS版本下:

<repo.location>\qnx_ap\boards\core\dalconfig\adp_star_sda<soc_ID>\config\spi_props_....xml

SPI属性文件的内容格式如下:

<global_def>

<var_seq name="spiqup0_master1_name" type=DALPROP_DATA_TYPE_STRING>MCU SPI1 (SOC Master)</var_seq>

<var_seq name="spiqup8_master2_name" type=DALPROP_DATA_TYPE_STRING>DSP SPI3 (SOC Master)</var_seq>

<var_seq name="spiqup9_master3_name" type=DALPROP_DATA_TYPE_STRING>DSP SPI2 (SOC Master)</var_seq>

<var_seq name="spiqup11_master4_name" type=DALPROP_DATA_TYPE_STRING>ETH SPI (SOC Master)</var_seq>

/* QUPV3 master clocks */

<var_seq name="gcc_qupv3_wrap0_master_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap_0_m_ahb_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_master_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap_1_m_ahb_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_master_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap_2_m_ahb_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_master_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_m_hclk_clk</var_seq>

/* QUPV3 core clocks */

<var_seq name="gcc_qupv3_wrap0_core_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_core_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_core_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_core_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_core_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_core_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_core_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_core_clk</var_seq>

/* QUPV3 GSI clocks */

<var_seq name="gcc_qupv3_wrap0_gsi_sequencer_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_core_2x_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_gsi_sequencer_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_core_2x_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_gsi_sequencer_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_core_2x_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_gsi_sequencer_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_2xcore_clk</var_seq>

/* QUPV3 SE WRAP 0 clocks */

<var_seq name="gcc_qupv3_wrap0_serial_engine_0_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s0_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_1_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s1_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_2_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s2_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_3_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s3_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_4_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s4_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_5_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s5_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_6_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s6_clk</var_seq>

<var_seq name="gcc_qupv3_wrap0_serial_engine_7_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap0_s7_clk</var_seq>

/* QUPV3 SE WRAP 1 clocks */

<var_seq name="gcc_qupv3_wrap1_serial_engine_0_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s0_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_serial_engine_1_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s1_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_serial_engine_2_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s2_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_serial_engine_3_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s3_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_serial_engine_4_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s4_clk</var_seq>

<var_seq name="gcc_qupv3_wrap1_serial_engine_5_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap1_s5_clk</var_seq>

/* QUPV3 SE WRAP 2 clocks */

<var_seq name="gcc_qupv3_wrap2_serial_engine_0_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s0_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_serial_engine_1_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s1_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_serial_engine_2_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s2_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_serial_engine_3_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s3_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_serial_engine_4_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s4_clk</var_seq>

<var_seq name="gcc_qupv3_wrap2_serial_engine_5_clock_name" type=DALPROP_DATA_TYPE_STRING>gcc_qupv3_wrap2_s5_clk</var_seq>

/* QUPV3 SE WRAP SSC clocks */

<var_seq name="scc_qupv3_wrap0_serial_engine_0_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se0_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_serial_engine_1_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se1_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_serial_engine_2_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se2_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_serial_engine_3_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se3_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_serial_engine_4_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se4_clk</var_seq>

<var_seq name="scc_qupv3_wrap0_serial_engine_5_clock_name" type=DALPROP_DATA_TYPE_STRING>scc_qupv3_se5_clk</var_seq>

</global_def>

<device id=DALDEVICEID_SPI_DEV_1>

<props name="SPI_ENABLED" type=DALPROP_ATTR_TYPE_UINT32> 1 </props>

<props name="SW_ENABLE_BAM" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="SW_USE_POLLING_MODE" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="SLAVE_MODE_ENABLE" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="SLAVE_DIRECT_WIRED" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="slave1 name" type=DALPROP_ATTR_TYPE_STRING_PTR>spiqup0_master1_name</props>

<props name="slave1 mode" type=DALPROP_ATTR_TYPE_UINT32>0x2408</props>

<props name="slave1 clock" type=DALPROP_ATTR_TYPE_UINT32>4800000</props>

<props name="CLOCK_MASTER_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR>gcc_qupv3_wrap0_master_clock_name</props>

<props name="CLOCK_CORE_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR>gcc_qupv3_wrap0_core_clock_name</props>

<props name="CLOCK_GSI_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR>gcc_qupv3_wrap0_gsi_sequencer_clock_name</props>

<props name="CLOCK_SE_NAME" type=DALPROP_ATTR_TYPE_STRING_PTR>gcc_qupv3_wrap0_serial_engine_0_clock_name</props>

<props name="CHIP_BLOCK_OFFSET" type=DALPROP_ATTR_TYPE_UINT32> 0 </props>

<props name="QUP_BLOCK_SIZE" type=DALPROP_ATTR_TYPE_UINT32> 0x4000 </props>

<props name="CHIP_PERIPH_SS_BASE" type=DALPROP_ATTR_TYPE_UINT32> 0x880000 </props>

<props name="QUP_QGIC_IRQ" type=DALPROP_ATTR_TYPE_UINT32> 633 </props>

<props name="QUP_BASE_FREQ_KHZ" type=DALPROP_ATTR_TYPE_UINT32> 16000 </props>

</device>配置XML文件由两部分组成:

- 标记为Global_def的全局定义,包含QUP SE名称和QUP配置中使用的时钟的全局名称。上一节讨论了时钟名称及其与QUP SE的相关性。时钟示例显示,需要在全局定义部分列出所有相关时钟。

- 标记为device的设备数据,包含使用SPI协议启用和初始化QUP SE所需的所有详细信息。每个设备都需要以下属性:

- ID--确定SPI外围设备的DAL标识。ID枚举如下:DALDEVICEID_SPI_DEV_1~12,最多可配置12个SPI外设。一旦QUP初始化,HLOS将创建一个应用程序使用的节点。例如,如果DALDEVICEID_SPI_DEV_3外设已启用,则将创建相应的/DEV/spi3 DEV节点以与该外设通信。

- SPI_ENABLED--将外围设备设置为已启用(设置属性值1)或已禁用(将属性值设置为0)

- SW_ENABLE_BAM--编程QUP SE工作模式。当设置为1时,QUP引擎将设置为DMA模式。否则,如果设置为0,工作模式将为FIFO。

- SW_USE_POLLING_MODE--已过时,其属性值始终设置为0

- SLAVE_MODE_ENABLE--确定QUP SPI引擎是作为SPI主机(属性值设置为0)还是作为SPI从机(属性值设为1)运行。该模式需要基于硬件配置部分中说明的QUP协议分配。

- slave1name--于在运行时提供SPI外围设备信息

- slave1mode--用于设置QUP SPI引擎的默认SPI模式。

- slave1clock--在运行时提供SPI外围时钟信息

- CLOCK_MASTER_NAME--全局部分中定义的主时钟名称

- CLOCK_CORE_NAME--全局部分中定义的核心时钟名称

- CLOCK_GSI_NAME--全局部分中定义的核心时钟名称

- CLOCK_SE_NAME--全局部分中定义的SE时钟名称

- CHIP_BLOCK_OFFSET--始终默认为值0

- QUP_BLOCK_SIZE--定义QUP SE注册表区域大小,并始终设置为0x4000

- CHIP_PERIPH_SS_BASE--定义QUP SE基地址。

- CHIP_QGIC_IRQ–定义服务协议事件的QUP SE中断号

- QUP_BASE_FREQ_KHZ--定义QUP SE基本时钟频率,单位为KHZ

2218

2218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?