高阻态

高阻态是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,和没接一样。

电路分析时可以把高阻态看成开路,即输出(输入)电阻非常大,极限可以认为是悬空。但是理论上高阻态不是悬空,而是对地或者对电源的电阻非常大的状态,实际应用上与引脚悬空是一样的。

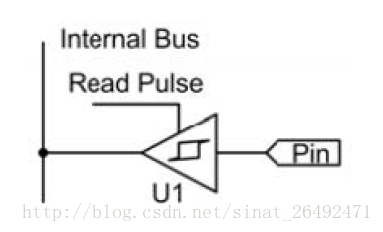

上图所示为GPIO管脚在高阻态输入模式下的等效结构模式图。Pin表示GPIO管脚,这是一个管脚的情况,其他管脚的结构也是同样的输入模式的结构比较简单,就是一个带有施密特触发输入(Schmitt-triggered input)的三态缓冲器(U1),并具有很高的阻抗。施密特触发输入的作用是能将缓慢变换的或者畸变的输入脉冲信号整形成比较理想的矩形脉冲信号。执行GPIO管脚读操作时,在读脉冲(Read Pulse)的作用下会把管脚(Pin)的当前电平状态读到内部总线上(Internal Bus)。

不执行读操作时,它可以变成高阻态的状态,使得外部管脚和内部总线之间是隔离的。

为什么会有这种高阻抗的管脚设计呢?因为很多管脚是连在同一根线上,为了不干扰其他管脚,当一个管脚在传输数据的时候,其他管脚配置成高阻抗,就不会干扰正在传输的管脚了,这样可以很多管脚同时共用一根总线,分时复用。

为了减少信息传输线的数目,大多数计算机中的信息传输采用总线模式,即凡要传输的同类信息都在同一组传输线,而且信息是分时传送的,在计算机中一般有三组总线,即数据总线,地址总线和控制总线。为防止信息相互干扰,要求凡是挂到总线上的寄存器或者存储器,它的输入输出不仅能呈现0、1两个信息状态,还能产生一种高阻态的状态,即它在这种状态下与总线隔离,对总线状态不起作用,此时总线可以由其他器件占用。三态缓冲器即可实现上述功能,它除了具有输入输出功端之外,还有一个控制端,就像一个开关一样,可以控制使其变成高阻态状态。

推挽输出

推挽输出可以提高输出功率,能更好地驱动外部设备。

推挽输出的原理:功率放大电路中大量采用推完放大器电路,这种电路中用两只三极管的分别放大输入信号的正半周和负半周,即一直三极管放大信号的正半周,用另一只三极管放大信号的负半周,两只三极管输出的半周信号在放大器敷在后合并得到一个完整周期的输出信号。

推挽放大器电路中,一只三极管工作在导通、放大时,另一只三极管处于截止状态,当输入信号变化到另一个半周期之后,原先导通、放大的状态转变为截止状态,而原先截止的三极管进入导通、放大状态,两只三极管在不断地交替导通放大和截止,所以称为推完放大器。

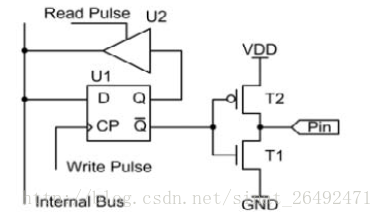

上图所示为GPIO管脚在推挽输出模式下的等效结构示意图。U1是输出锁存器,执行GPIO管脚写操作的时候,在写脉冲(WritePulse)的作用下,数据被锁存到Q和/Q。T1和T2构成CMOS反相器,T1或T2导通的时候都表现出较低的阻抗,但是T1和T2不会同时导通或同时关闭,最后形成的是推挽输出。在推挽输出模式下,GPIO还具有回读功能,独到的是管脚的输出锁存状态,而不是外部管脚Pin的状态。

推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小、效率高。输出既可以向负载灌电流,也可以从负载抽取电流。所以推挽式输出既提高电路的负载能力,又提高开关速度。

推完放大器的输出级又两个“臂”(两组放大原件),一个“臂”的电流增加时,另一个“臂”的电流则减小,二者的状态轮流转换。对负载而言,一个“臂”在推,另一个“臂”在拉,共同完成电流输出任务。

开漏输出

开漏输出就是不输出电压, 低电平时接地,高电平时不接地。如果外接上拉电阻,则在输出高电平时电压会拉到上拉电阻的电源电压,如果开漏输出的管脚被上拉了,那么这个管脚将一直默认是输出高电平的。

一般来说,开漏是用来连接不同电平的器件,匹配电平用的,因为开漏引脚不连接外部的上拉电阻时,只能输出低电平,如果需要同时具备输出高电平的功能,则需要接上拉电阻。这就是很好的一个优点,因为通过改变上拉电源的电压,便可以改变传输电平,比如上拉电阻就可以提供TTL/CMOS电平输出等。

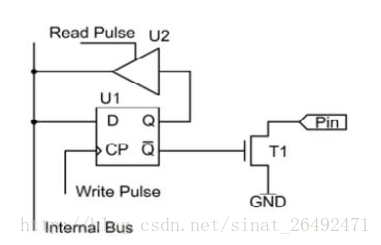

上图所示为GPIO管脚在开楼输出模式下的等效结构示意图。开漏输出和推挽输出相比结构基本相同,但是开漏输出只有下拉晶体管T1而没有上拉晶体管。同样,T1实际上也是多组可编程选择的晶体管。开漏输出的实际作用就是一个开关,输出“1”时断开,输出“0”时连接到GND(有一定内阻)。回读功能:读到的仍然是输出锁存器的状态,而不是外部管脚Pin的状态。因此开漏输出模式是不能用来输入的。

开漏输出的优点是IC内部仅需要很小的驱动电流就可以了,因为它主要是利用外部电路的驱动能力,这样可以减少IC内部的驱动,并且外部需要什么样的电压,就上拉到相应的电压,需要多大的电流,也可以通过改变上拉电阻来调节电流,所以开漏输出是一种非常灵活的一种输出。

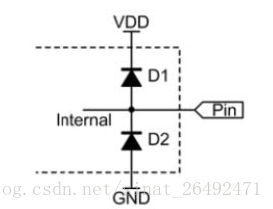

钳位二极管(用于保护GPIO引脚)

GPIO内部具有钳位保护二极管,如下图所示。其作用是防止 外部管脚Pin输入的电压过高或过低。VDD正常供电是3.3V,如果从Pin输入的信号(假设任何输入信号都有一定的内阻)电压超过VDD(假设为3.6V)+D1的导通压降(假设为0.6V)=3.9V,此时二极管D1导通,这样就会把多余的电流引到VDD,而真正输入到内部的信号电压不会超过3.9V。同理,乳沟才能够Pin输入的信号电压比GND还低,则由于二极管D2的作用,会把是技术如内部的信号电压钳制在-0.6V左右。

假设VDD=3.3V,GPIO设置在开漏模式下,外接10千欧上拉电阻连接到5V电源,在输出“1”时我们测量发现:GPIO管脚上的电压并不会达到5V,而是4V(3.3+0.6=3.9V)上下但是对于实际的数字逻辑通常3.5V以上就算是高电平了.

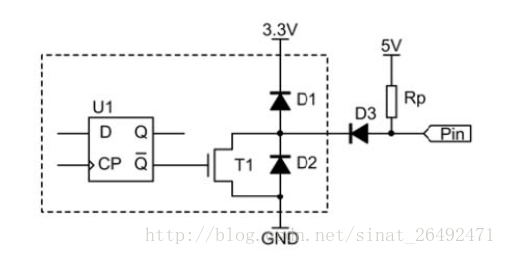

如果想进一步提高输出电压,一种简单的做法是先在GPIO管脚上串联一只二极管,然后再接上上拉电阻。参见下图,框内是芯片内部电路。向管脚写“1”时,T1关闭,在Pin处得到的电压是3.3+VD1+VD3=4.5V,电压提升效果明显;向管脚写“0”时,T1导通,在Pin处得到的电压是VD3=0.6V,为低电平。

5776

5776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?