锁相环(PLL)低杂散方案设想

[锁相环(PLL)低杂散方案设想_锁相环杂散_雪江南的博客-CSDN博客](https://blog.csdn.net/sinat_28083087/article/details/129531579)

这一版的初步设想方案经过官方双demo的任意随机频点验证和在版实验目前已经确定为可行方案,小数杂散可以通过相关方法进行平滑展现出较为光滑的相噪曲线。

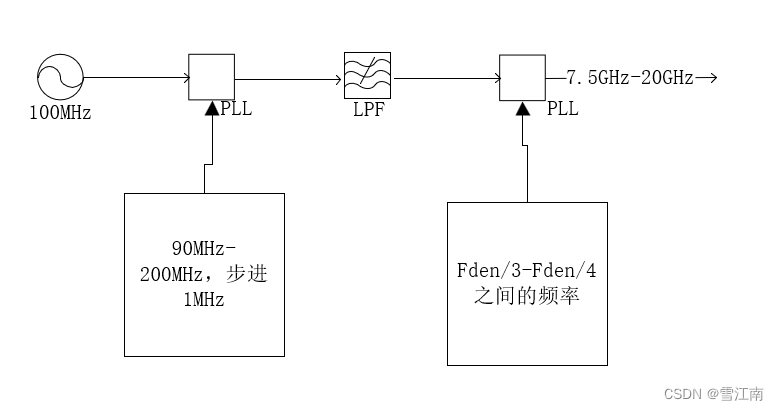

1. 初级版本性能分析值优缺点。

针对以上方案进行了缺点和优点的评估,如下所述。

优点:1. 双环直接串连,物理上体积最小。2. 在软件配置上第一个环进行1M步进,第二个环按照频率进行分频等配置,计算量不大。 3.在前级锁相环锁定时后级配置范围内锁定较快。4.

缺点:1.前级带内杂散都会经过后级锁相环并展现出来。2.前级和后级都会有自身的小数杂散,前级还有其整数边界杂散。3.前级VCO范围有1G宽度,跳频时间较长,导致整体锁定时间较长。

2. 优化方案设计

在不改动硬件方案设计,只是优化配置方式的方法下,思考如下新配置方案。

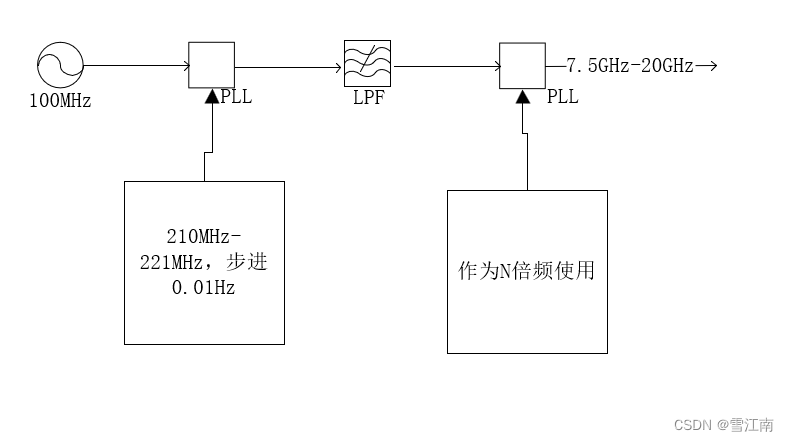

该方案我称为钱锁相环扰动方案,前级锁相环进行窄频段范围内重复配置,后级锁相环配置成整数模式N倍频。这样前级VCO缩短成为600M,按此原理可以继续缩短以提高前级锁相时间。这样在这个歌方案窄频段跳动时,前级基本是扰动后级VCO范围很窄情况下基本能达到快速锁定。为此我们需要计算前级锁相环的频率范围和后级需要的倍频级数如下。

该方案我称为钱锁相环扰动方案,前级锁相环进行窄频段范围内重复配置,后级锁相环配置成整数模式N倍频。这样前级VCO缩短成为600M,按此原理可以继续缩短以提高前级锁相时间。这样在这个歌方案窄频段跳动时,前级基本是扰动后级VCO范围很窄情况下基本能达到快速锁定。为此我们需要计算前级锁相环的频率范围和后级需要的倍频级数如下。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

991

991

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?