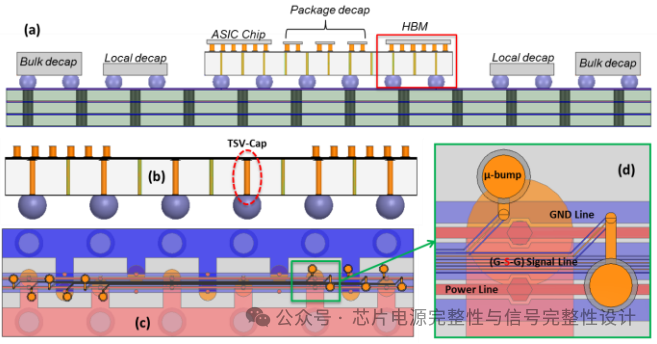

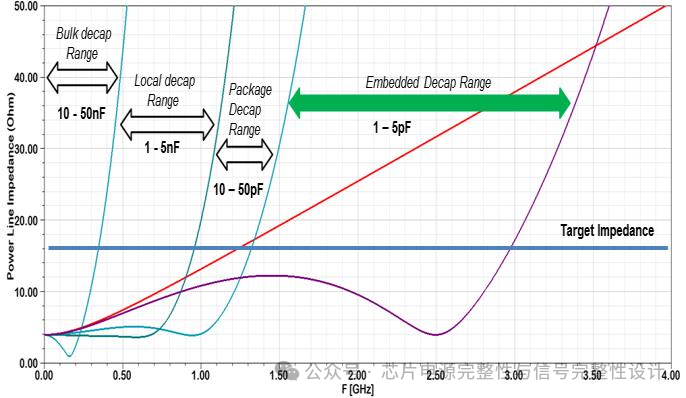

在ASIC-HBM系统中,电源完整性性能至关重要。由于ASIC与HBM互连的布局邻近性,电源线与信号线之间的串扰可能非常显著。为最小化串扰,需在宽带频率范围(0-5 GHz)内将电源线的阻抗保持在阈值以下。图1展示了ASIC-HBM封装模型及其用于电源分配网络(PDN)阻抗调优的各类组件(体去耦电容、局部去耦电容、封装去耦电容、嵌入式去耦电容、片上电容)。图2显示了各去耦电容的调谐范围。目前,硅interposer上主要采用沟槽电容和金属-绝缘体-金属(MIM)电容作为嵌入式去耦电容。然而,MIM或沟槽电容需占用额外的硅面积,并需增加工艺层或掩膜。本文提出利用TSV-Cap在1-5 GHz范围内调谐PDN阻抗。如图1(b)所示,TSV电容器围绕TSV结构构建于相邻TSV的间距之间,从而提高了硅利用率。

图1. (a) ASIC-HBM封装示意图;(b) interposer垂直视图;(c) interposer簇互连;(d) 电源/信号/地线布局。

图2. 宽带频率范围内需各类组件(体去耦、局部去耦、封装去耦、嵌入式去耦、片上电容)进行阻抗调优。

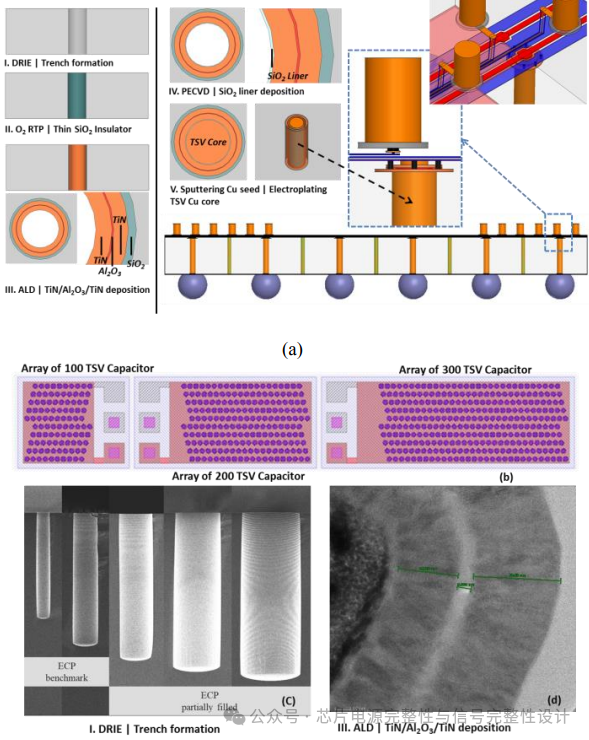

TSV电容的制造

图3展示了ASIC-HBM interposer中TSV-Cap的制造流程。首先,在硅衬底上涂覆光刻胶(PR)并进行图案化,通过深反应离子刻蚀(DRIE)形成沟槽。随后采用氧气快速热退火(RTP)工艺生成薄SiO₂绝缘层。接着,通过原子层沉积(ALD)依次沉积TiN/Al₂O₃/TiN层。通过重复沉积电极和介质层可形成多层MIM结构。常规TSV工艺步骤包括等离子体增强化学气相沉积(PECVD)SiO₂衬层、溅射TiN作为扩散阻挡层、溅射铜种子层以及电镀铜TSV核心。随后通过化学机械抛光(CMP)对表面进行平坦化处理并光刻图案化。通过刻蚀步骤依次去除SiO₂/TiN/Al₂O₃层以定义顶部电极尺寸。最后,通过背面减薄和CMP工艺暴露TSV底部以进行背面处理。

图3. (a) TSV电容制造流程;(b) TSV电容阵列;(c) DRIE后的沟槽SEM图;(d) 添加TSV核心前的TiN/Al₂O₃/TiN层。

电源完整性阻抗调优

图1(c)展示了interposer上ASIC-HBM的簇互连模型。该簇包含用于信号传输的多层低延迟G-S-G互连、屏蔽互连的地总线以及电源总线。微凸块用于芯片与interposer的垂直互连,而可控塌陷芯片连接(C4)凸块则用于将interposer连接至PCB板。

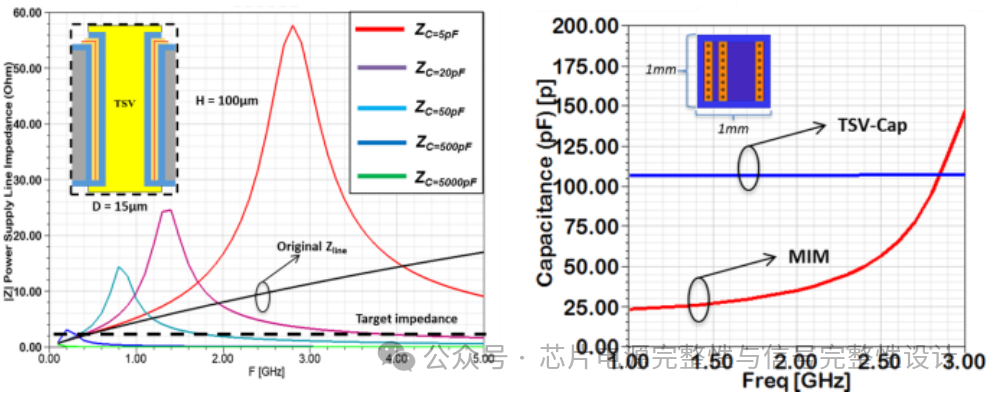

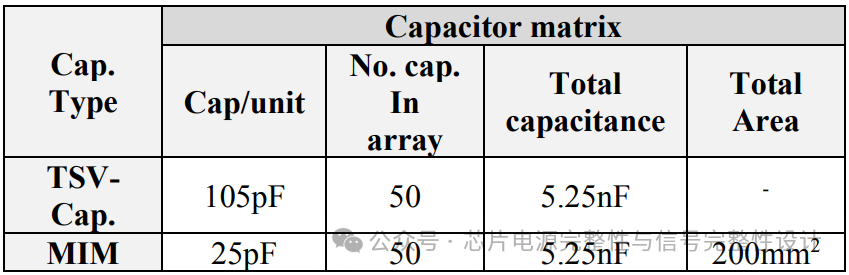

图4显示了利用TSV-Cap在DC-5 GHz范围内调谐电源线阻抗的效果。表1表明,使用105pF/单元的TSV-Cap阵列(共50个单元)可将PDN阻抗调至20mΩ(低于目标阻抗50mΩ)。若采用MIM电容实现相同总电容(5.25nF),需额外占用200mm²的硅面积。因此,TSV电容显著提升了硅面积利用率。

图4. 使用TSV电容或MIM电容调谐电源线阻抗。

表1. TSV与MIM电容的阻抗调优对比

串扰可能影响电源完整性和信号完整性。数字信号可通过同步开关噪声(SSN)电流耦合至电源线,导致电源线电压大幅波动。另一方面,电源线噪声可通过电容器耦合至信号线,从而降低可达到的数据速率。

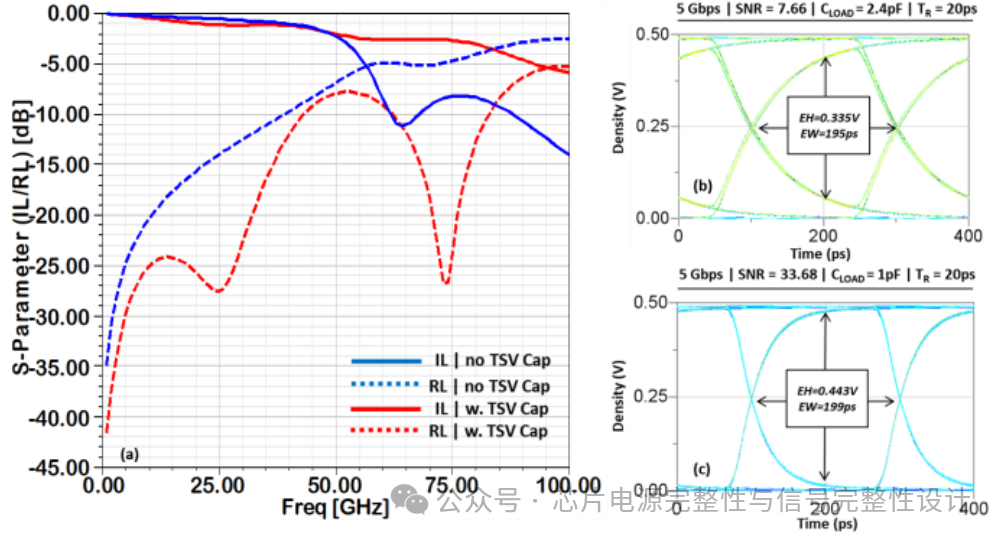

为探究TSV-Cap对信号完整性的影响,图5对比了含与不含TSV-Cap的线路射频性能(插入损耗IL与回波损耗RL)。加入TSV后,频率高于5 GHz时插入损耗下降0.5dB,但在频率高于50 GHz时插入损耗有所改善。整体回波损耗特性在DC-100 GHz范围内均得到提升。

图5. ASIC-HBM互连的插入损耗与隔离性能。

在采用TSV-Cap进行PDN调优的3D封装设计在考虑TSV-Cap阵列串扰后,可实现5Gbps的数据速率。当HBM负载电容分别为2.4pF和1pF时,获得的信噪比(SNR)分别为7.66和33.68。

1757

1757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?