随着电源的电压裕量继续降低,端到端电源完整性仿真已经很困难,作为电源完整性设计工程师,通常假设所有的供应商模型都是正确的。那么,如果电源完整性仿真所需的ASIC芯片模型之一不正确,工程师该怎么办?怎么确认电源需要多少Cdie量呢?本文将针对这些问题进行分析。

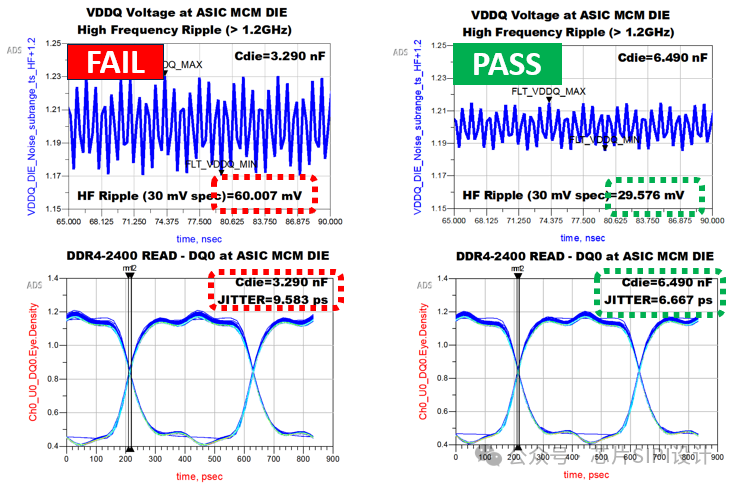

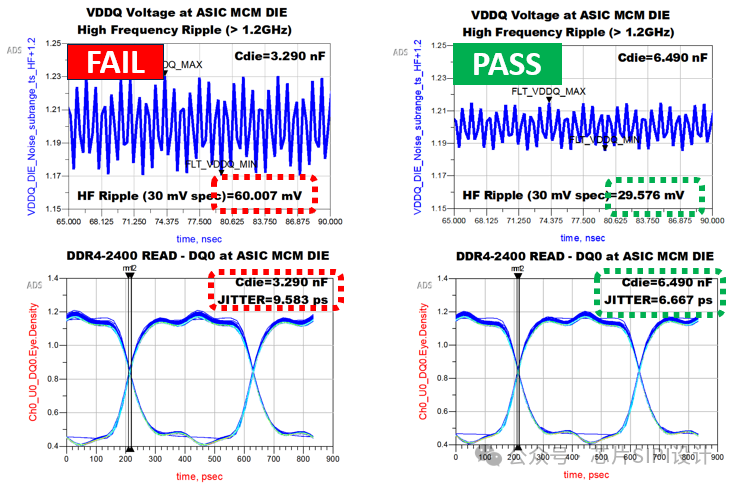

当芯片Cdie模型不正确时,会影响定时抖动和电压纹波。在下图所示的示例中,通过将Cdie从3.29 nF增加到6.49 nF,电压纹波减少51%,抖动减少30%。图也显示,在3.29nF时,电压纹波未能达到该电源域的规格。

随着电源的电压裕量继续降低,端到端电源完整性仿真已经很困难,作为电源完整性设计工程师,通常假设所有的供应商模型都是正确的。那么,如果电源完整性仿真所需的ASIC芯片模型之一不正确,工程师该怎么办?怎么确认电源需要多少Cdie量呢?本文将针对这些问题进行分析。

当芯片Cdie模型不正确时,会影响定时抖动和电压纹波。在下图所示的示例中,通过将Cdie从3.29 nF增加到6.49 nF,电压纹波减少51%,抖动减少30%。图也显示,在3.29nF时,电压纹波未能达到该电源域的规格。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?