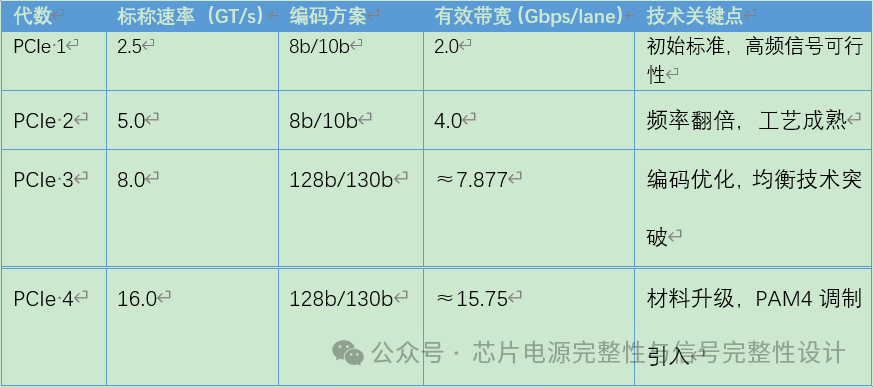

最近在研究PCIE的协议,发现一个有意思的问题,前两代PCIE演进速率是2.5Gbps到5Gbps,看上去是2.5X的速率上升的,而到PCIE3.0往后,变成了8Gbps到16Gbps,变成了8x的速率演进,这是为什么呢?然后就将4.0以前的基本情况对比了一下,如下:

1. PCIe 1.0(2.5 GT/s)

o 技术起点:早期采用8b/10b编码(20%开销),有效带宽为2.5Gbps × 0.8 = 2Gbps/lane。

o 物理限制:受制于当时硅工艺和信号完整性技术,高频信号传输难度大。

2. PCIe 2.0(5 GT/s)

o 直接翻倍:在成熟工艺下提升频率,保持8b/10b编码,带宽翻倍至4Gbps/lane。

3. PCIe 3.0(8 GT/s)

o 编码优化:改用128b/130b编码(开销降至1.5%),有效带宽提升至8 × (128/130) ≈ 7.877Gbps/lane,接近翻倍。

o 技术突破:预加重、均衡技术成熟,支持更高频率信号传输。

4. PCIe 4.0(16 GT/s)与后续版本

o 频率再翻倍:通过先进工艺(如PAM4调制)和低损耗材料(如Low-Dk PCB)实现速率跃升,同时保持向后兼容

可以看到速率从8到16是直接翻倍,而之前的2.5到5也是翻倍,但5到8是增加了3 Gbps,这就是因为编码效率的提升,如PCIe 3.0使用的128b/130b编码相较于之前的8b/10b,有效数据率更高。因此,虽然标称速率从5到8增加了60%,但实际有效带宽可能接近翻倍。例如,PCIe 2.0的5 GT/s使用8b/10b编码,有效带宽是5 * 0.8 = 4 Gbps per lane,而PCIe 3.0的8 GT/s使用128b/130b编码,有效带宽是8 * (128/130) ≈ 7.877 Gbps per lane,接近翻倍。所以,虽然标称速率增长不是整数倍,但有效带宽的提升可能更接近翻倍,这也是为什么后续的版本又回到翻倍的原因,比如PCIe 4.0的16 GT/s,使用同样的编码,有效带宽再次翻倍。

PCIe速率演进的主要因素包括:技术可行性、编码效率的提升、市场需求推动、向后兼容性需求,以及工程实现上的挑战。每一代的提升都是在现有技术基础上最大化带宽,同时确保稳定性和兼容性。

3594

3594

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?