1、系统时钟模块介绍

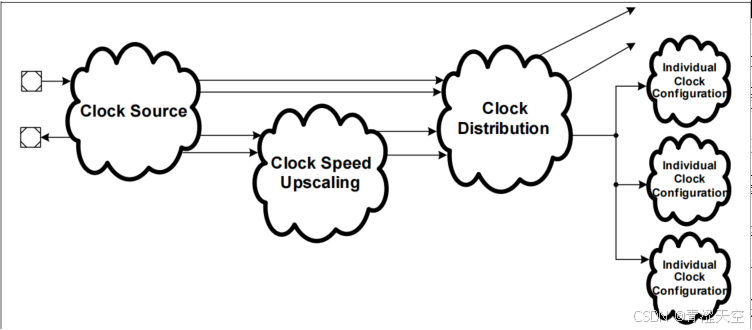

Aurix2G TC3XX系列的主频最高支持300MHz。该系列时钟系统主要包括时钟源、锁相环、时钟分配器组成。

系统时钟主要由以下几个时钟功能模块组成:

1、Basic clock generation(Clock Source)时钟源(一般由晶振提供)

2、Clock Speed up-scaling(PLLs)时钟倍频(锁相环)

3、Clock distribution(CCU)时钟分配单元

4、Individual clock configuration(Peripherals) 独立时钟配置(外设)

2、功能介绍

2.1、时钟源

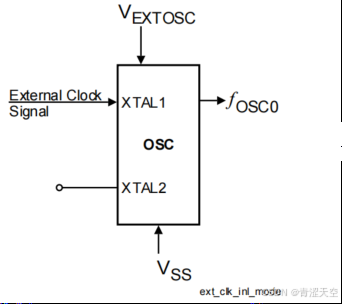

TC3XX系列有两种外部时钟源可供选择。

1、外部直接接入时钟源,也就是通过其它芯片或者电路直接进行时钟Tick输入。硬件连接如下图:

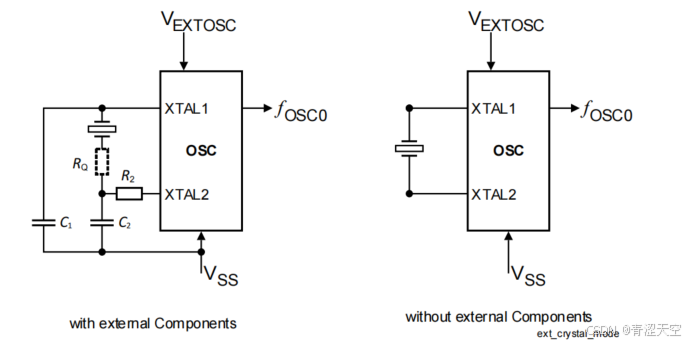

2、第二种是采用晶振(石英或者陶瓷),外部电路连接如下图:

作为软件,一般只需关注外部的时钟频率,也就是图中的FOSC0。一般为20MHz。

2.2、时钟倍频(PLL)

TC3xx系列一共有两个锁相环,系统锁相环其产生的时钟主要供CPU、存储模块使用。外设锁相环,其产生

时钟主要供外设模块使用。

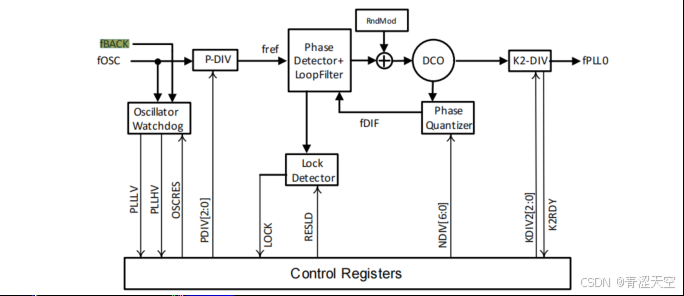

1、系统锁相环(System PLL)

系统锁相环可以将低频的外部输入时钟源进行倍频,提供给CPU等模块稳定高效的时钟源,同时提供安全

监控功能,当外部时钟源超出范围时执行紧急动作。系统锁相环模块示意图如下:

由图可知外部输入时钟源fOSC首先经过一个P-DIV进行预分频,在经过锁相环模块倍频得到fDCO,最后通过

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2538

2538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?