目录

Externa Crystal/Ceramic Resonator Mode

Configuration of the Oscilator

2. Clock Speed up-Scaling(PLLs)

一、版本控制

| 版本 | 撰写日期 | 撰写记录 | 字体颜色 |

| V1.0 | 2024.04.16 | 以当前时间点对Clock System(时钟系统)的认识,撰写了此文档,旨在阐述AURIX 2G系列MCU关于Clock System的实现原理。 | 黑色(有部分红色字体仅为辨识突出) |

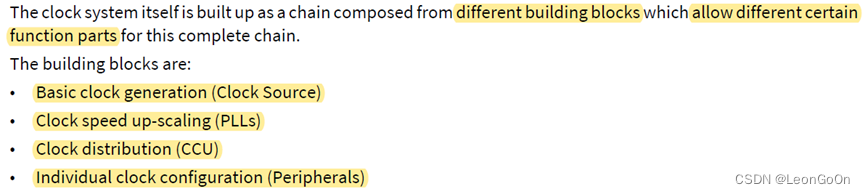

二、功能概述

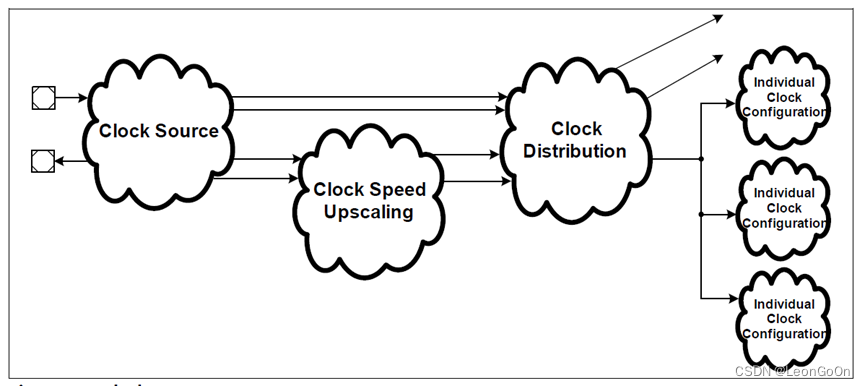

时钟是数字芯片工作的“脉搏”,可分为如下模块:

三、主要模块

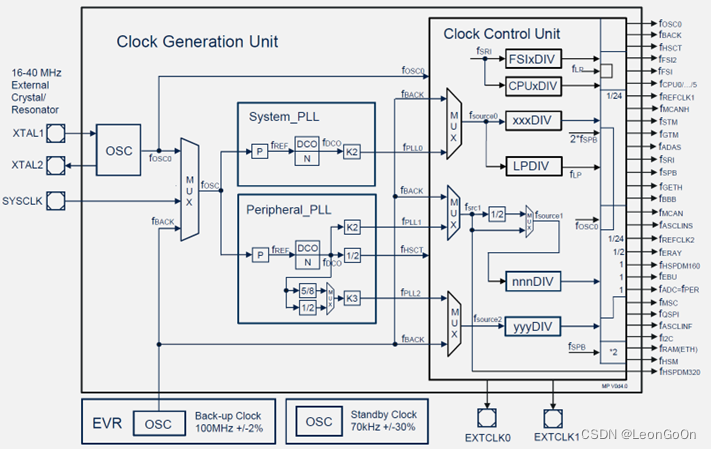

1. Clock Sources

a. Externa Input Clock Mode

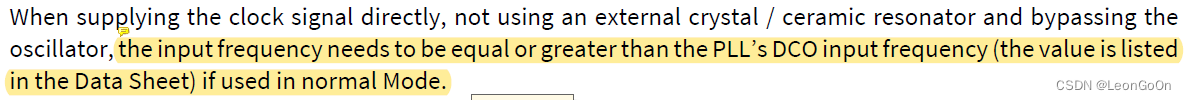

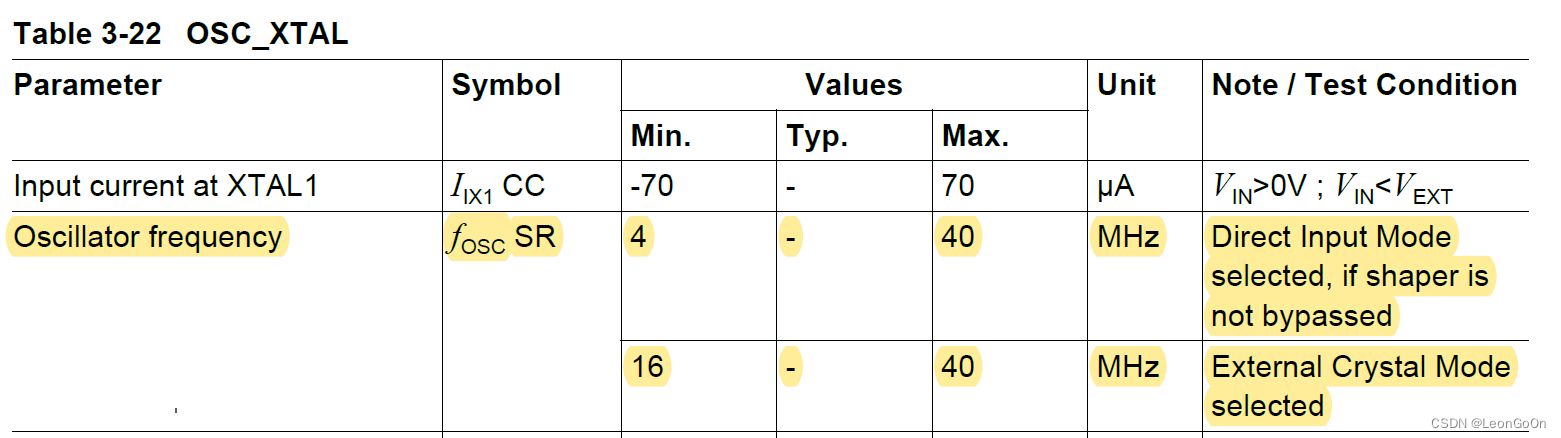

外界直接输入数字时钟信号给MCU,由XTAL1引脚进入,此数字时钟频率要大于或等于DCO Input Frequency。

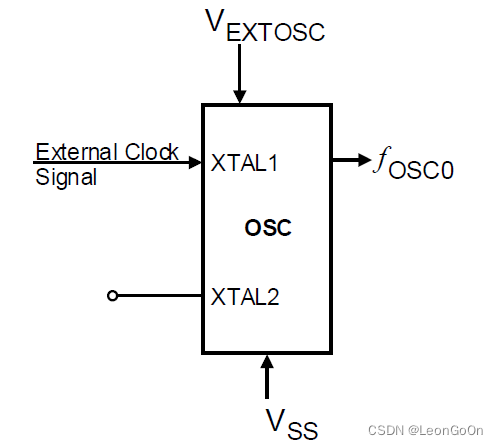

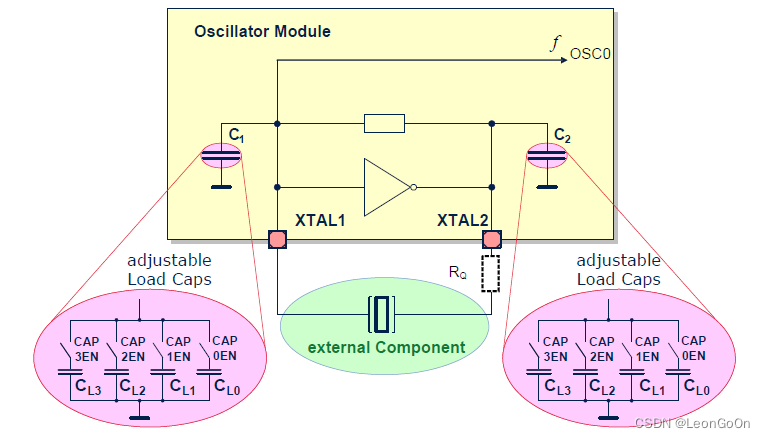

b. Externa Crystal/Ceramic Resonator Mode

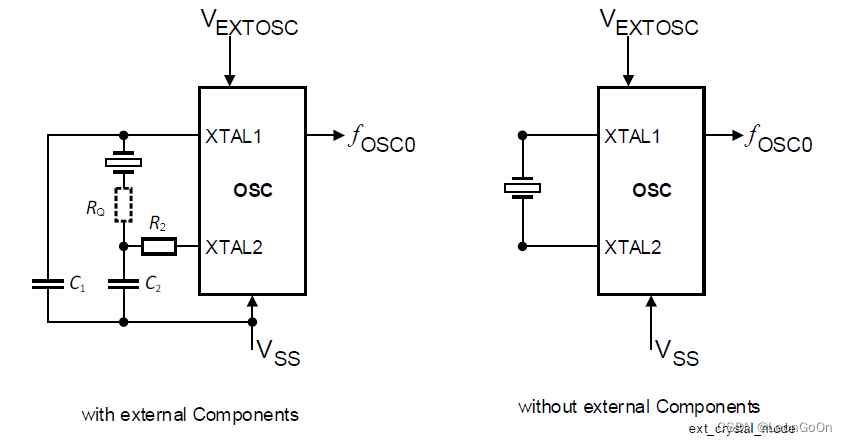

有外部振荡器的电路如上图所示,由两种模式,一种是外围电路自带一些电容电阻元器件,一种是不带,不带的可以选择是否使能芯片内部的电容。

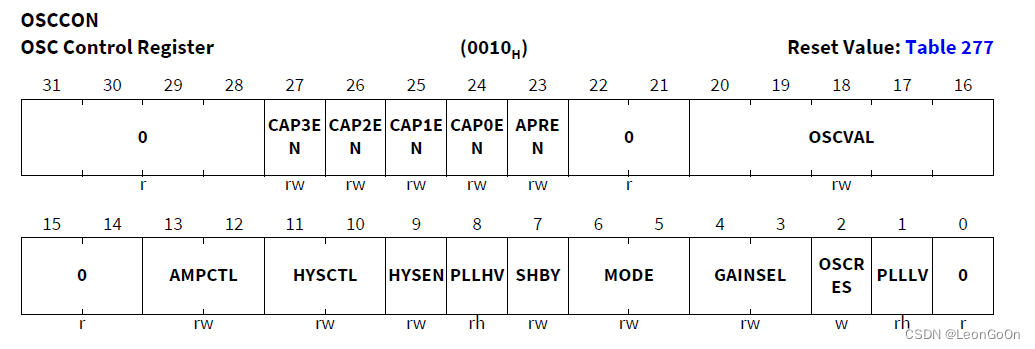

OSC有个控制寄存器OSCCON,完成一些属性及功能配置,如:

- 四个电容的使能CAPxEN

- 幅度调节模式的使能ARPEN

- Fosc的频率配置OSCAL(OSC 看门狗监控的就是这个频率)

- AMPCTL 幅度调节的不同模式

- Hysteresis的功能使能及模式选择 HYSCTL HYSEN

- Shaper是否旁路

- Clock Source的选择(外部振荡器或者直接外部时钟输入,或者OSC屏蔽,低功耗模式是否开启)

- 看门狗监控是否有频率过高或过低状态标志 PLLLLV和PLLLLH

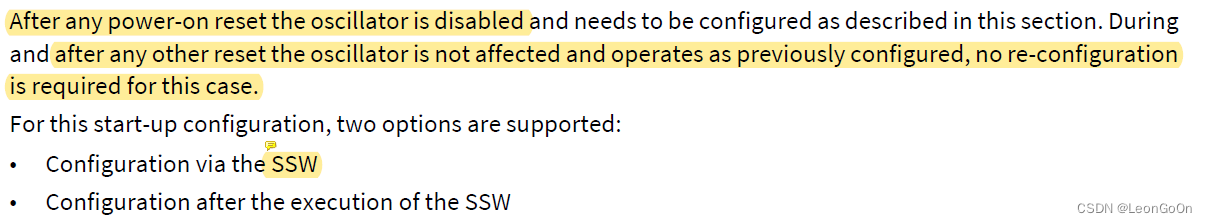

c. Configuration of the Oscilator

SSW是指芯片的Boot Firmware

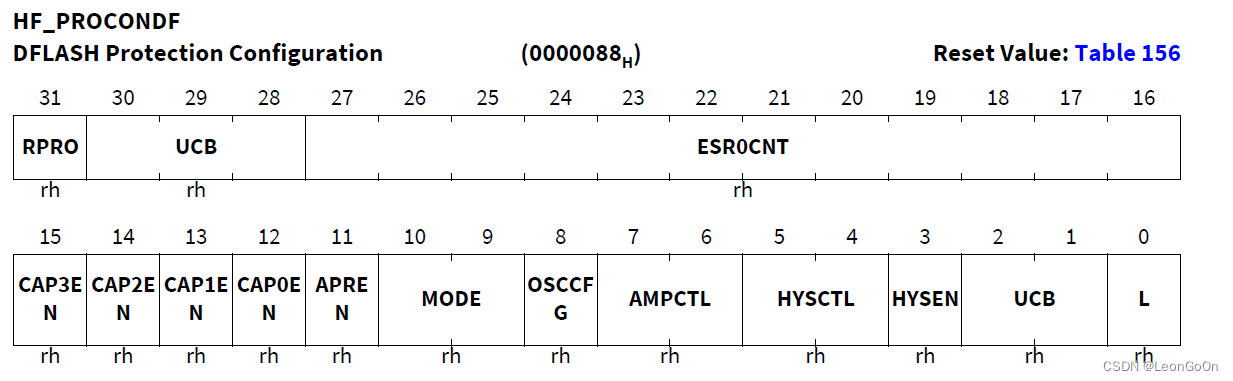

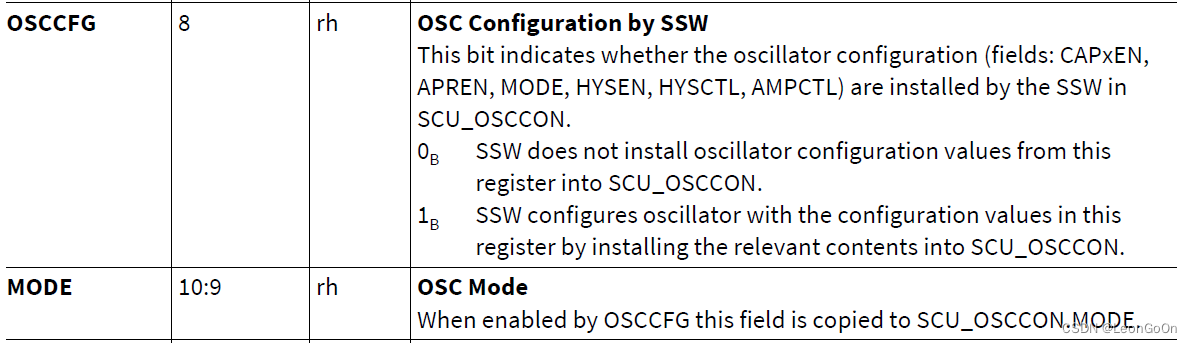

有两种方式来初始化OSC,一种是在SSW阶段做,通过下图寄存器的OSCCFG来使能,一些控制信息在SSW阶段通过下图寄存器导入到SCU_OSCCON中。

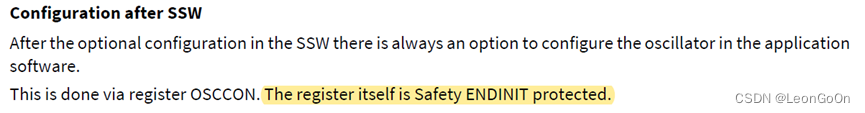

还有一种是SSW之后在Application初始化:

d. Back-up Clock

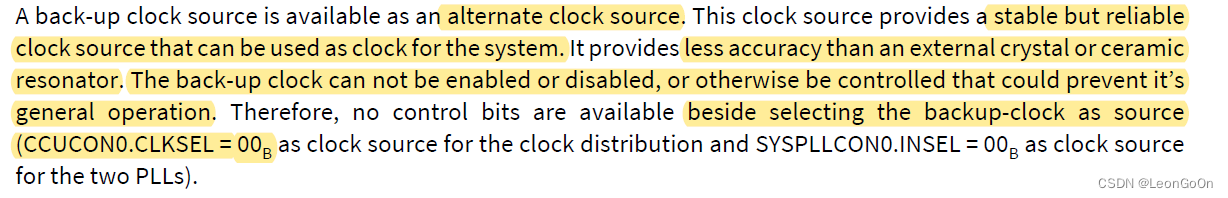

Back up Clock是芯片上电就会有的,不过精度相对外部晶振会差些,其不能被用户控制有无,但可以控制其是否作为后面PLL时钟和fsource的源头。

2. Clock Speed up-Scaling(PLLs)

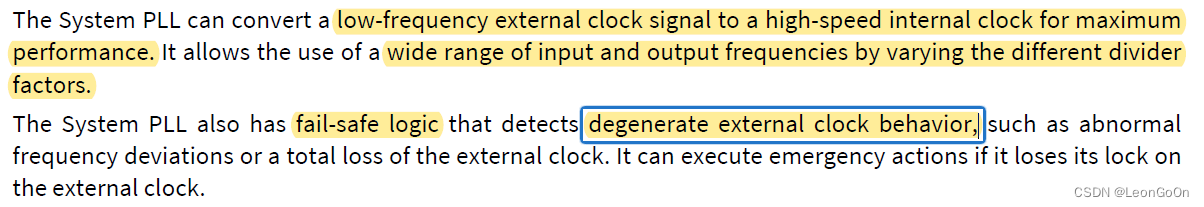

a. System PLL Module

锁相环倍频,并且有安全机制。

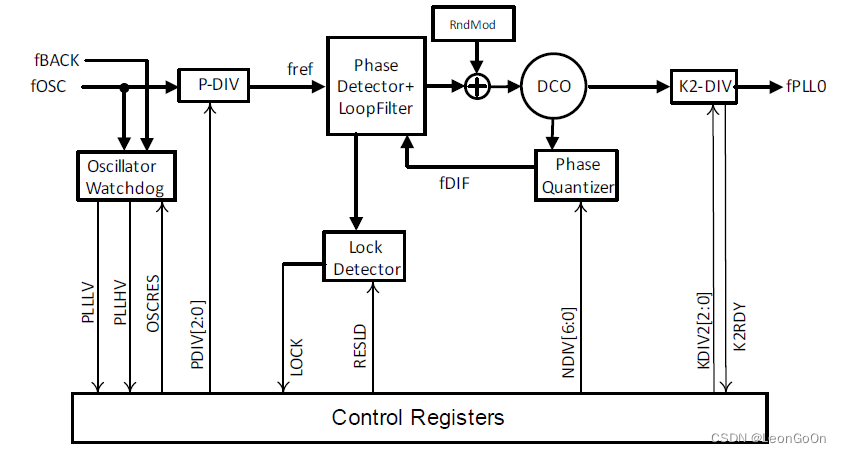

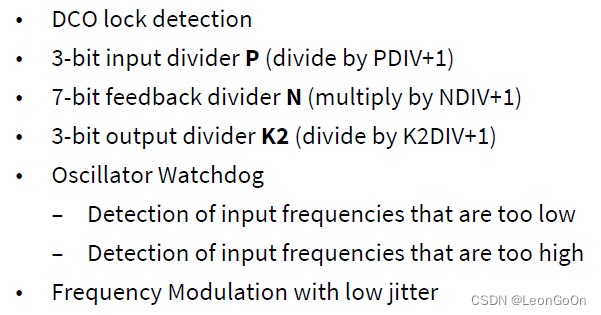

System PLL的总体框图:

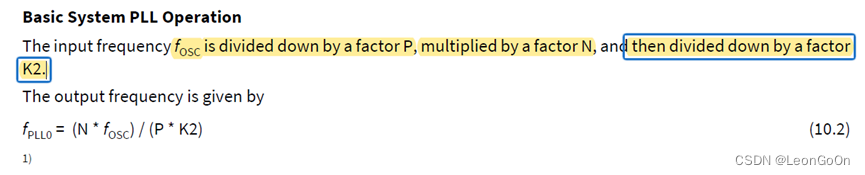

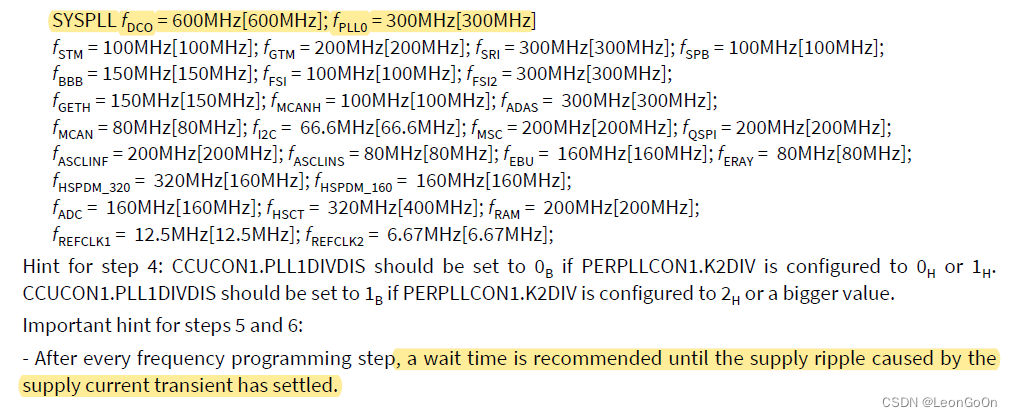

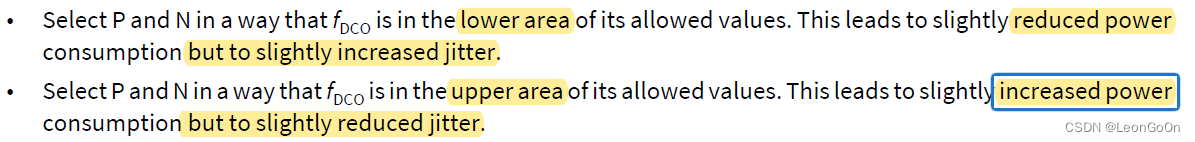

倍频后的时钟计算公式:一般300MHZ的PLL0时钟设定N为30、P为1、K2为2,输入晶振频率20MHZ。

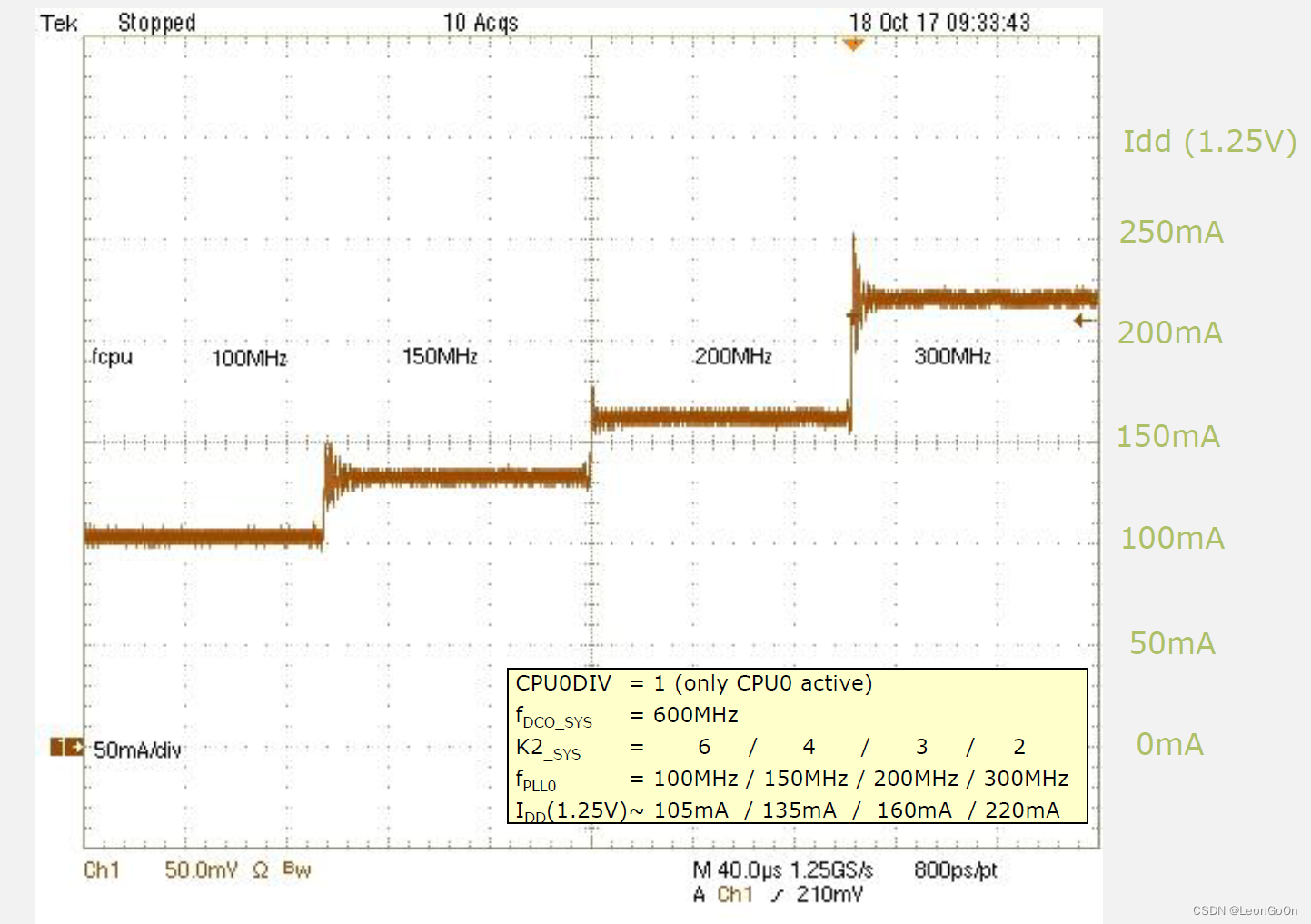

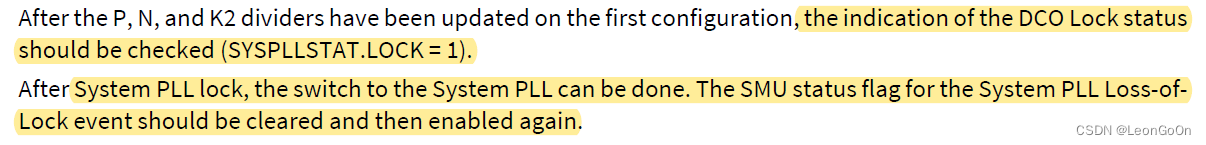

在运行过程中要更改系统PLL输出的时钟频率,应按照如下流程执行:

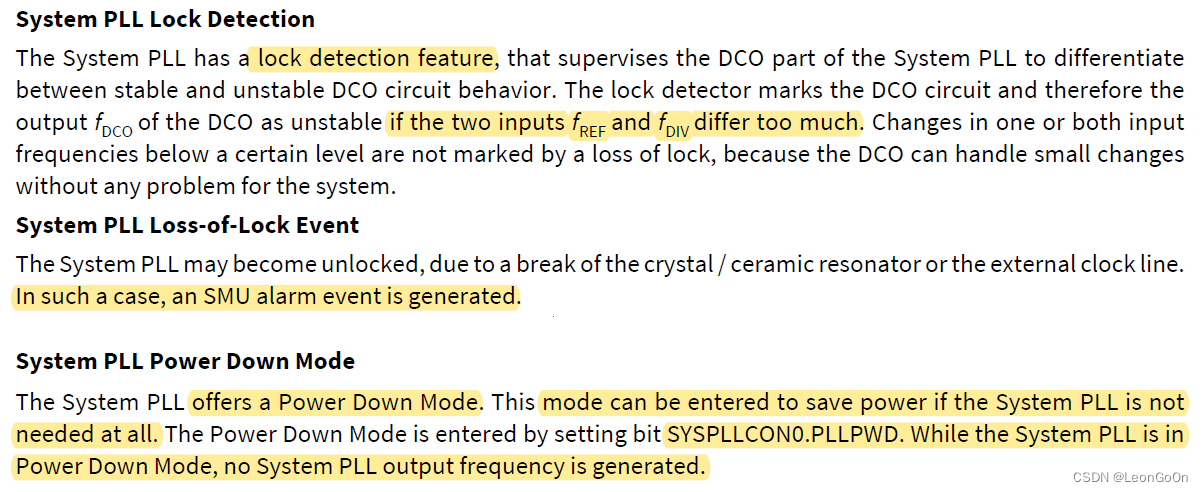

系统PLL有上锁检测功能,来验证fdco产出时钟频率的稳定性,在锁丢失时,会对SMU产生alarm event;系统 PLL在不需要使用时可以开启Power Down模式以节省能耗。

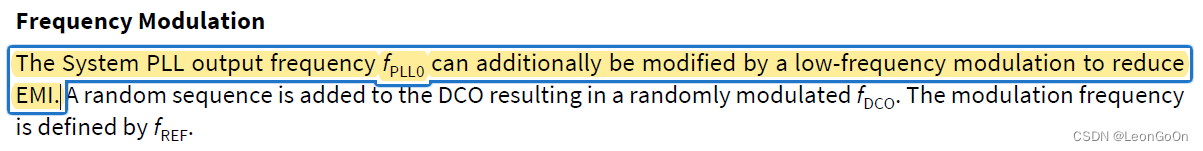

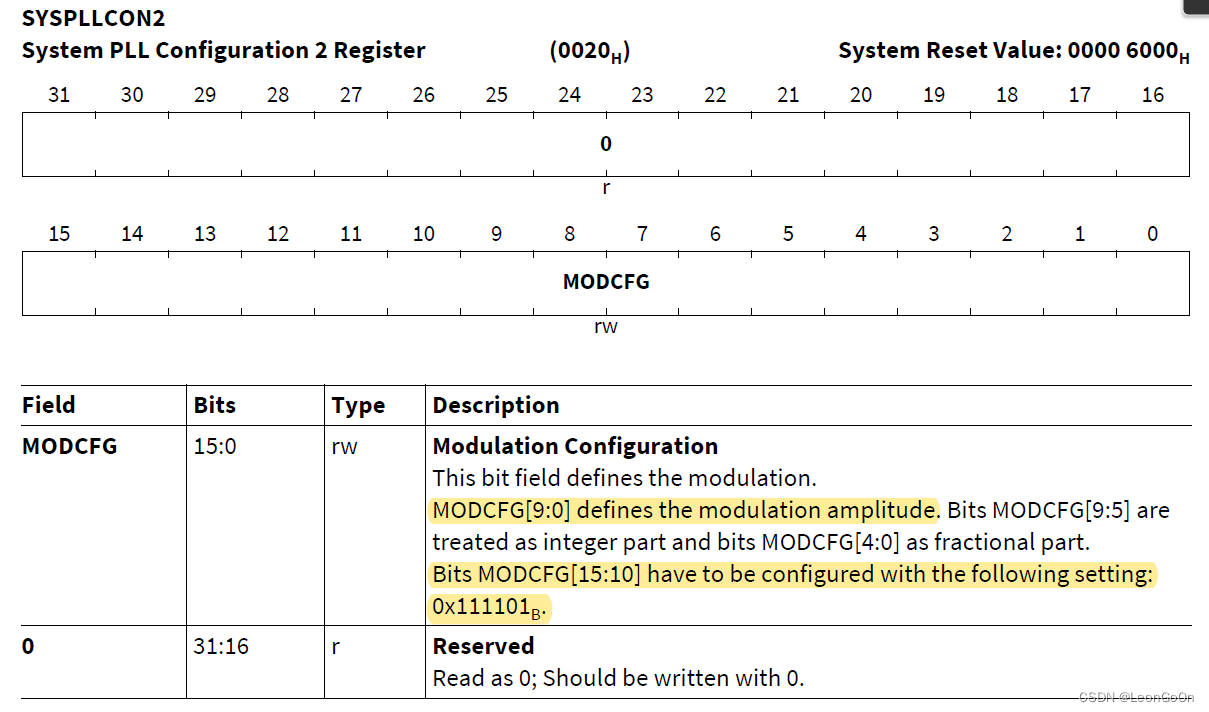

System PLL有频率解调器用来降低EMI

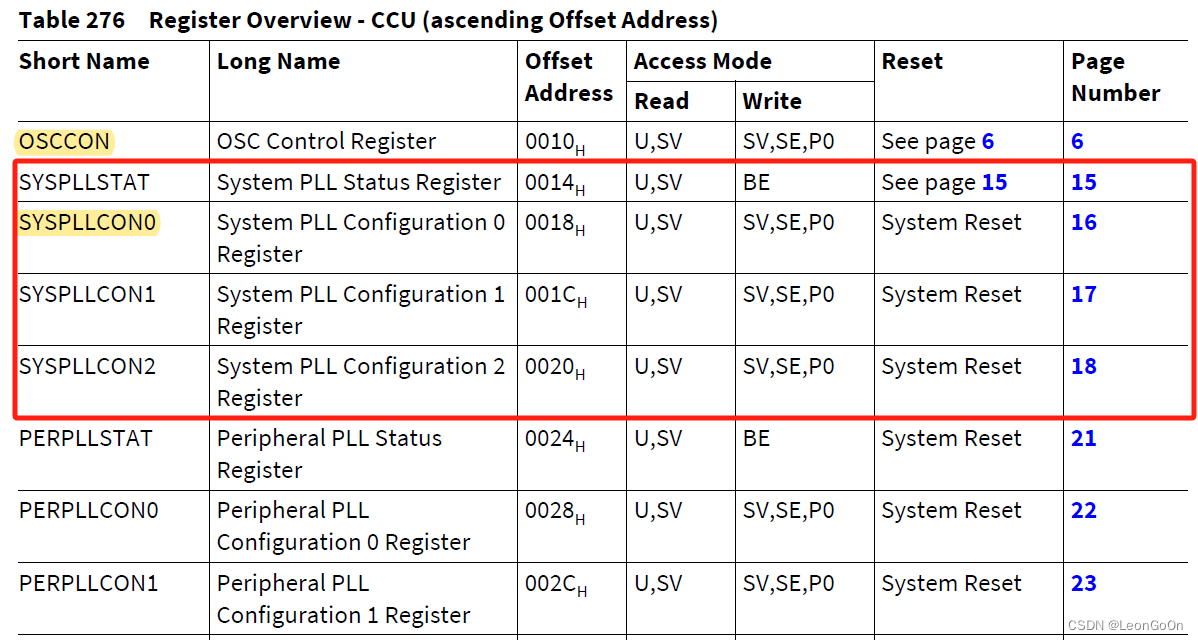

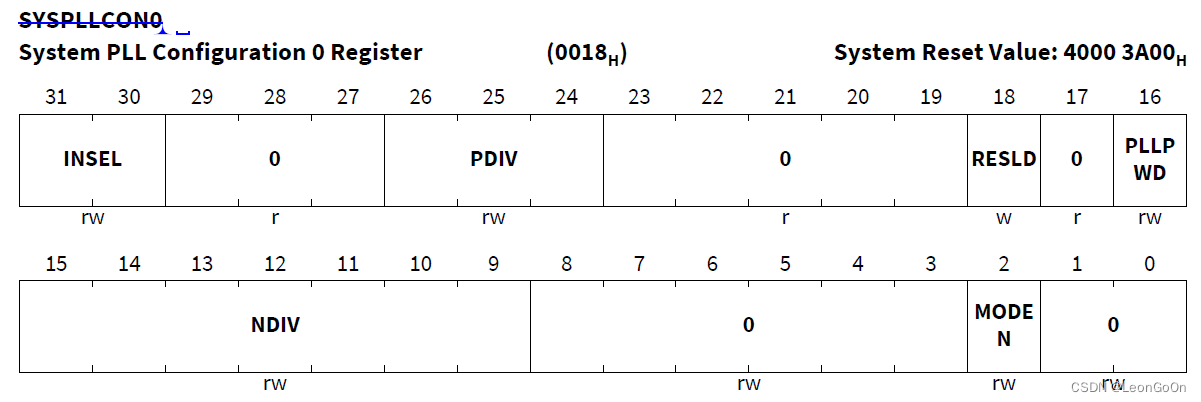

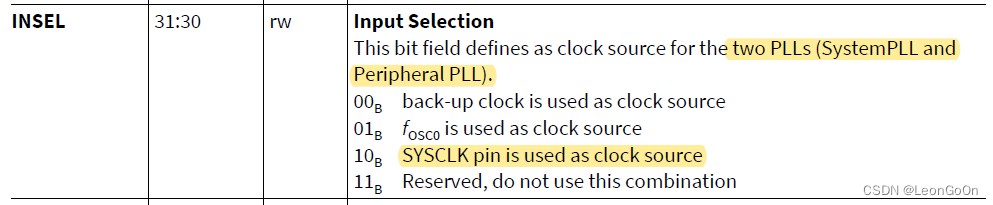

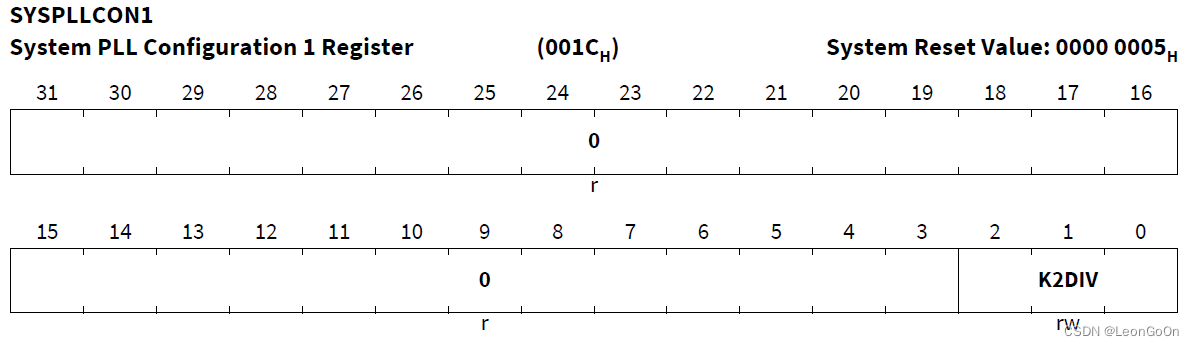

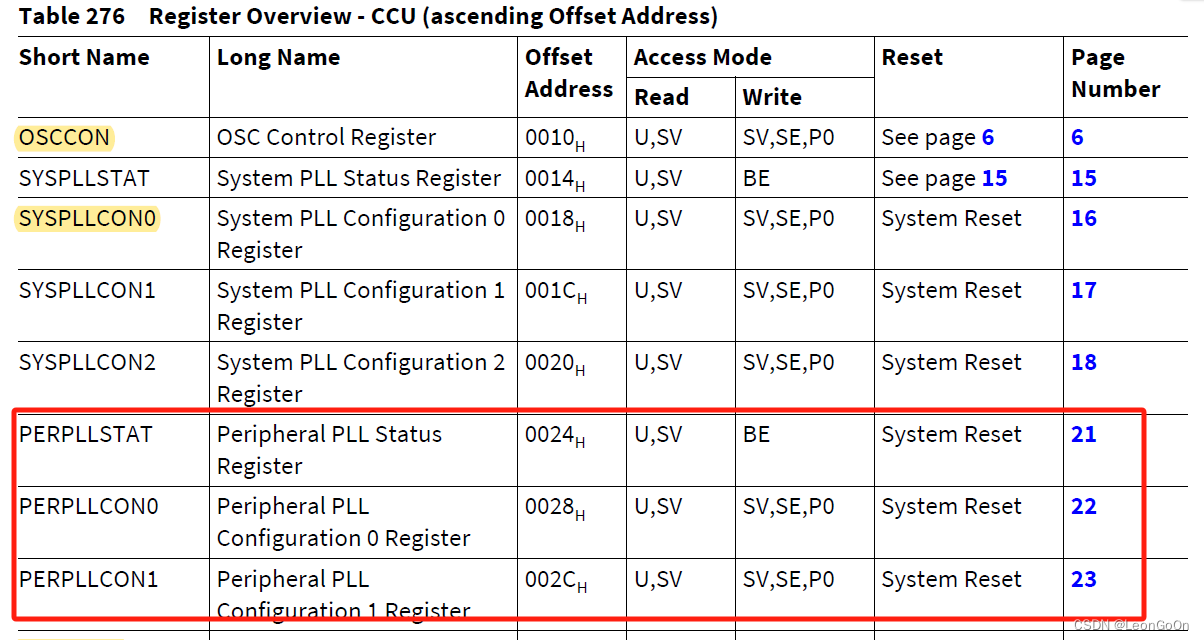

System PLL的相关寄存器:

SYSPLLSTAT用来表征System PLL的一些状态(是否Lock,Power-Saving模式是否开启,频率解调器是否使能等);

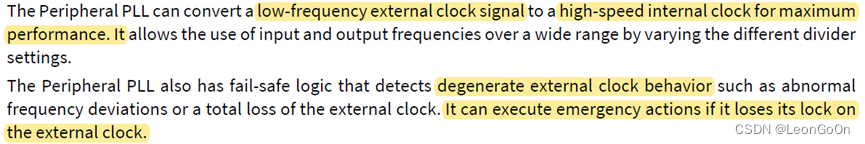

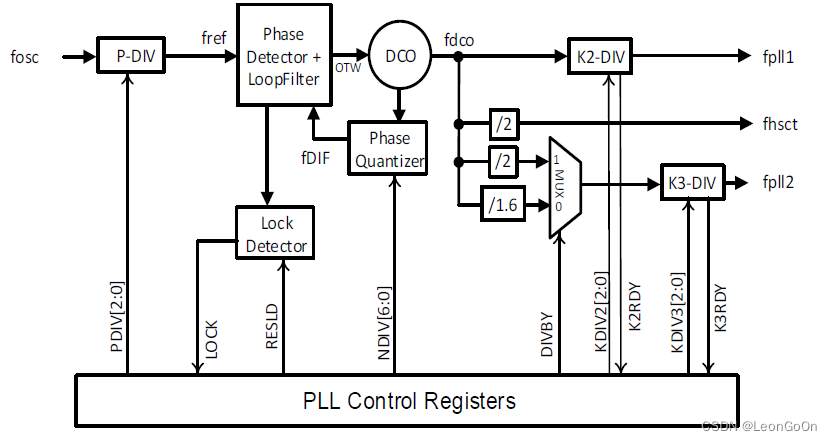

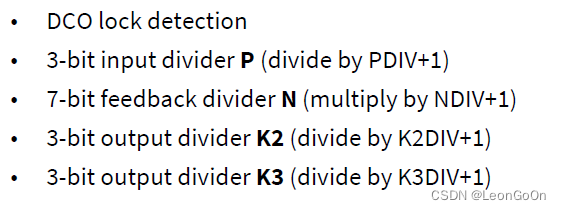

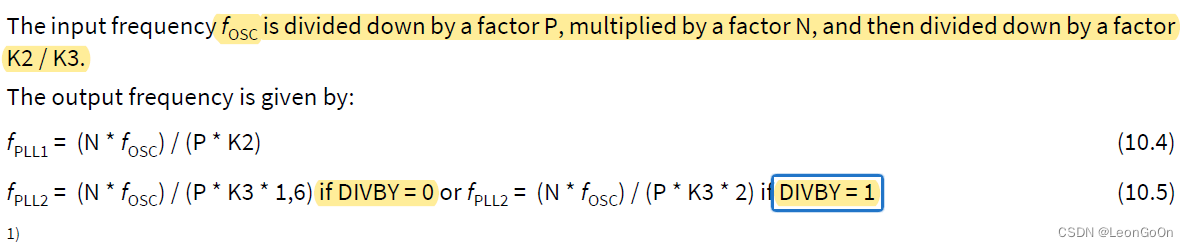

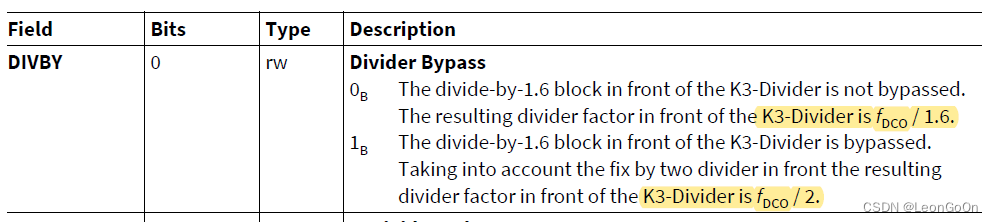

b. Periphera PLL Module

锁相环倍频,并且有安全机制。

peripheral PLL的总体框图:

在运行过程中要更改外设PLL输出的时钟频率,应按照如下流程执行:

在运行过程中要更改外设PLL输出的时钟频率,应按照如下流程执行:

外设PLL有上锁检测功能,来验证fdco产出时钟频率的稳定性,在锁丢失时,会对SMU产生alarm event;外设 PLL在不需要使用时可以开启Power Down模式以节省能耗。

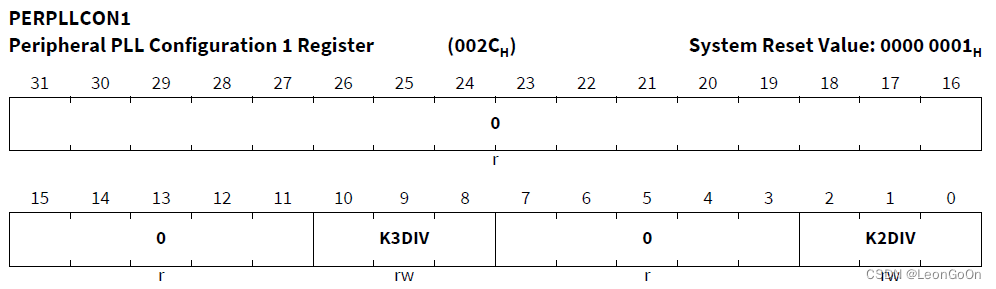

Peripheral PLL的相关寄存器:

PERPLLSTAT用来表征Peripheral PLL的一些状态(是否Lock,Power-Saving模式是否开启,K2/K3是否有新值的改动);

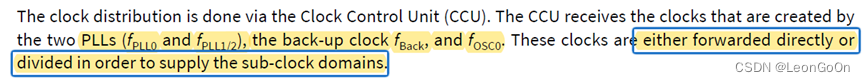

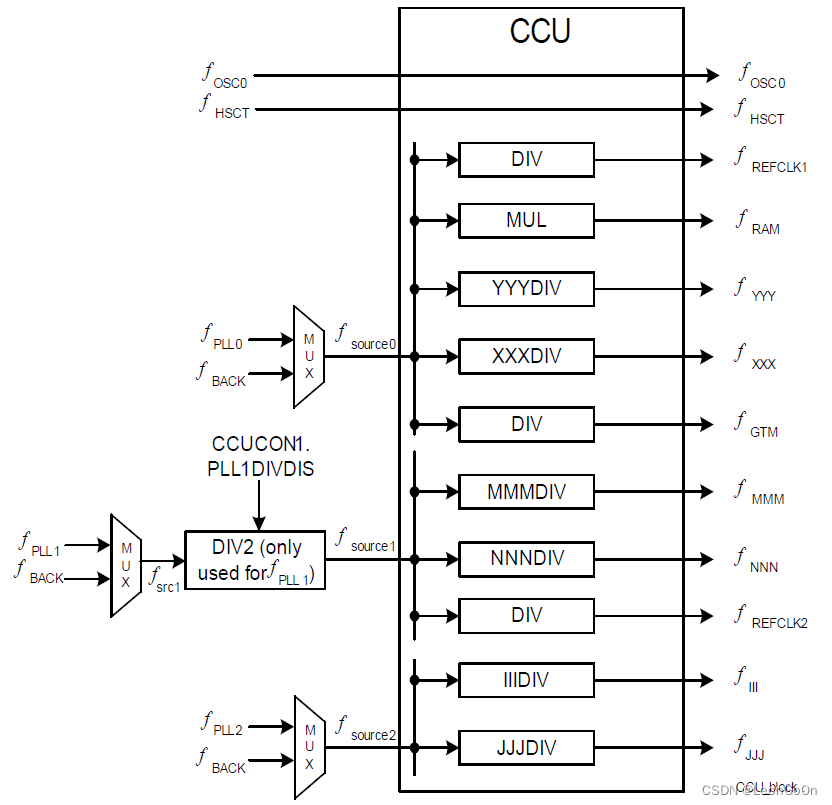

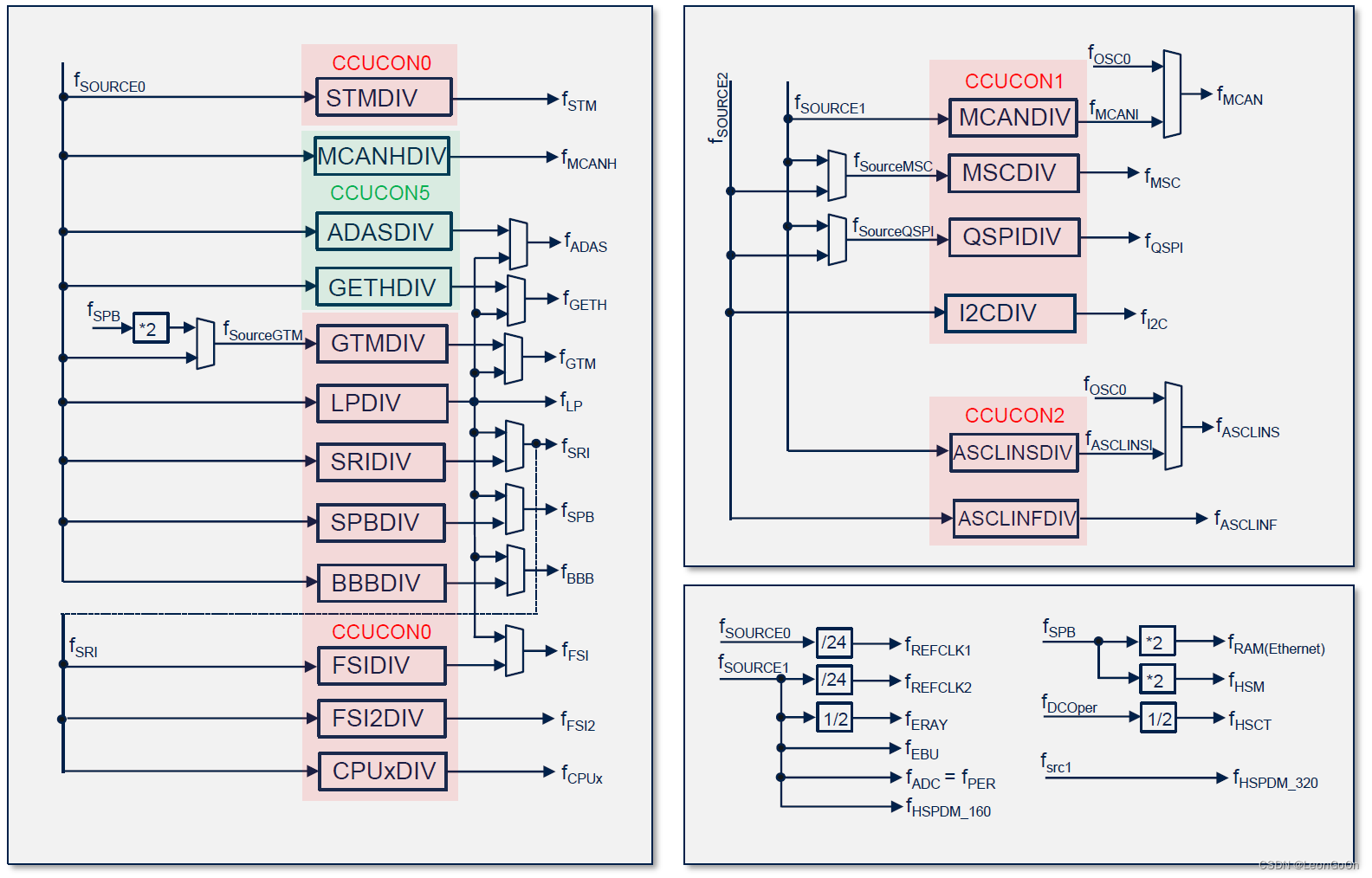

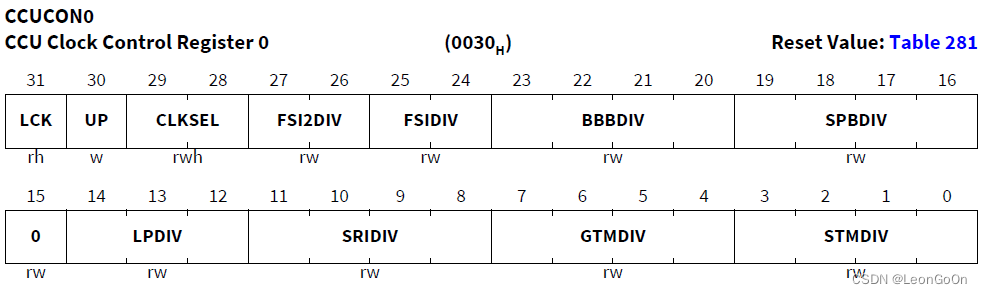

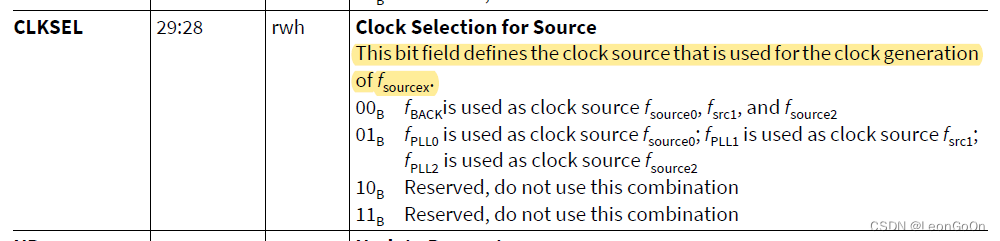

3. Clock distribution(CCU)

CCU模块在接收PLL产生的三个时钟,Back Up Clock,OSC时钟,HSCT时钟后,以完成后面芯片模块的时钟分频:

![]()

![]()

![]()

![]()

![]()

![]()

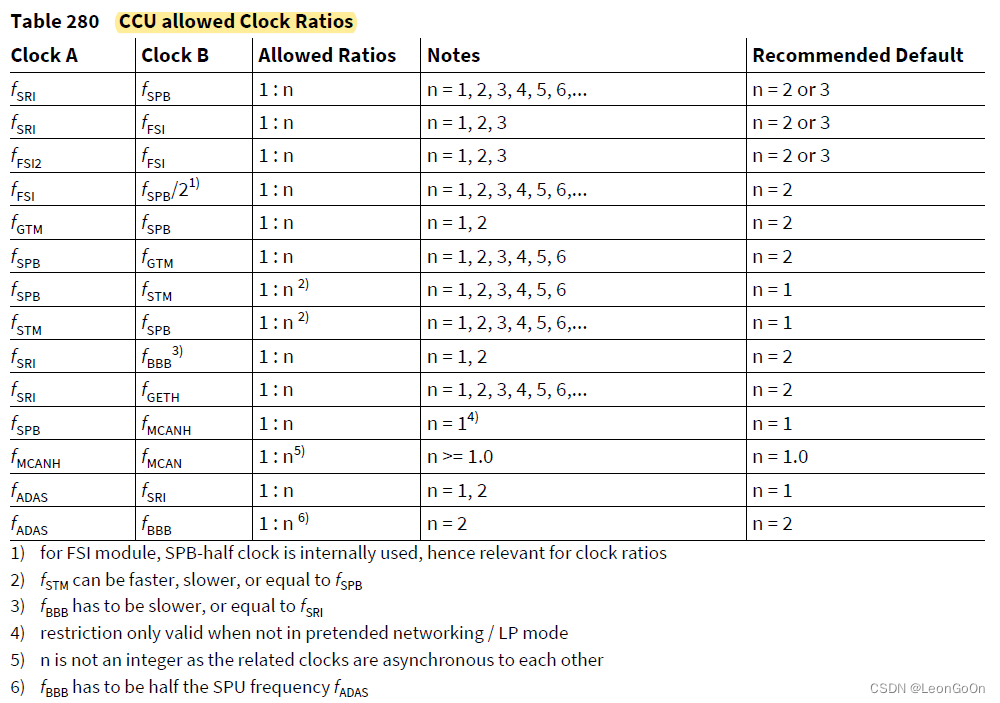

一些时钟之间一定要满足一定的比例关系:

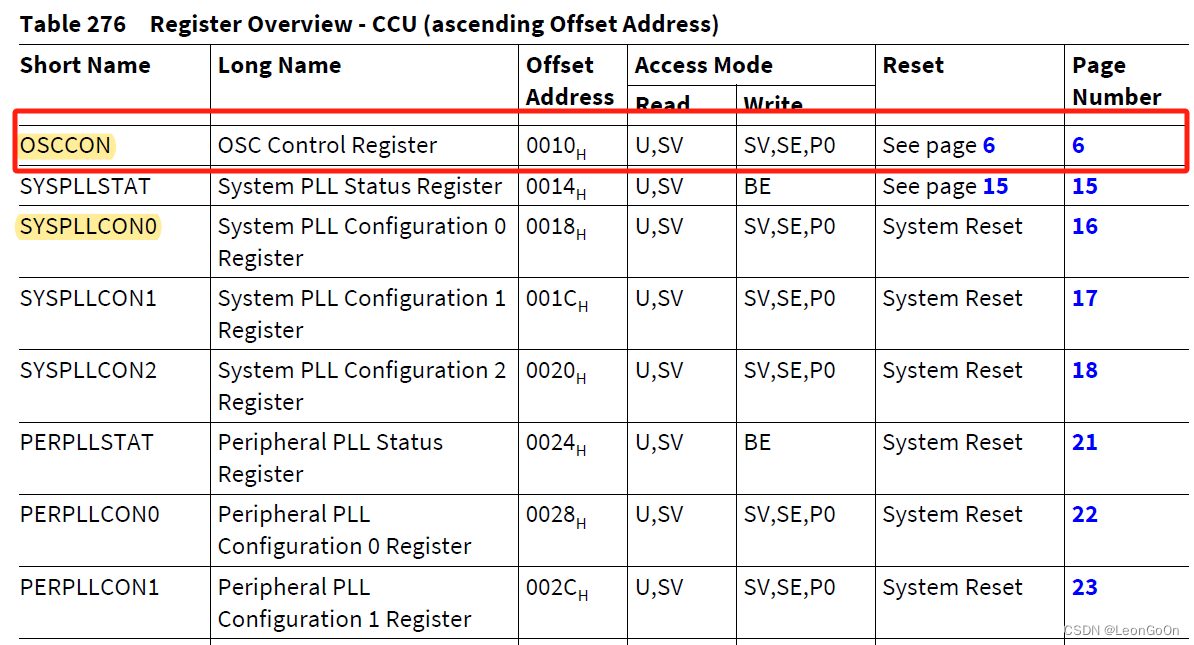

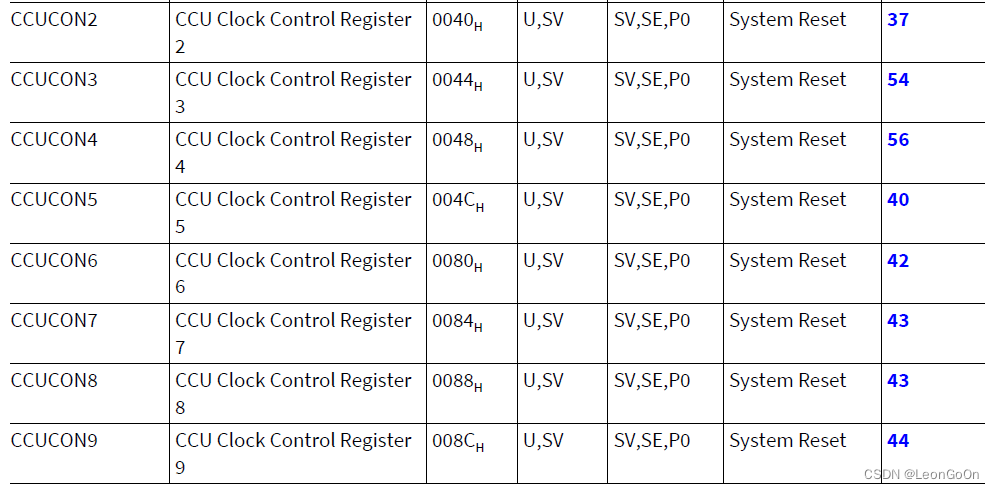

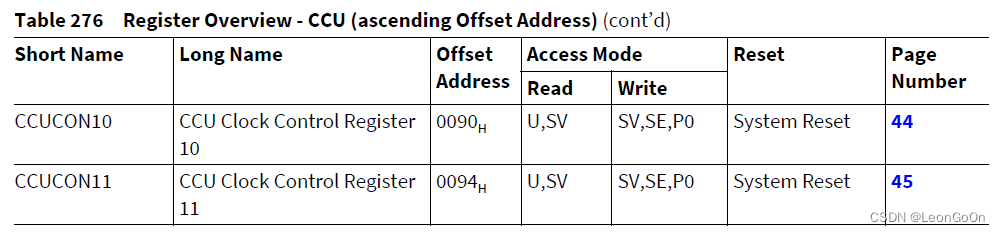

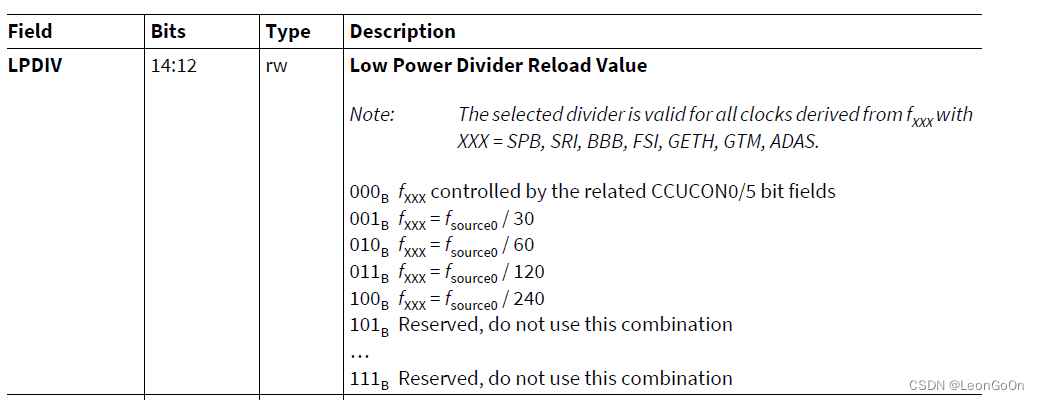

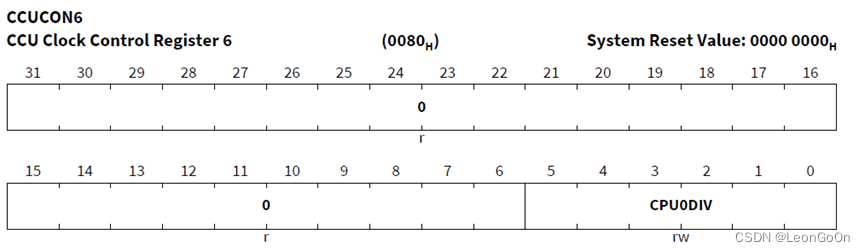

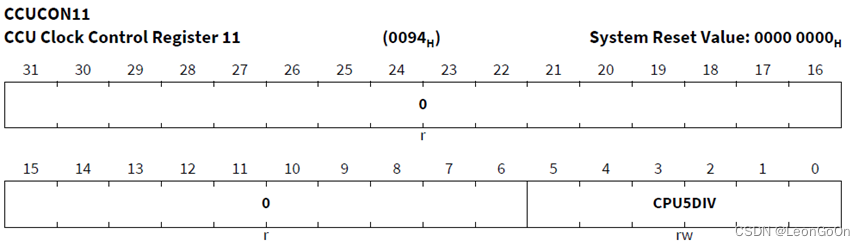

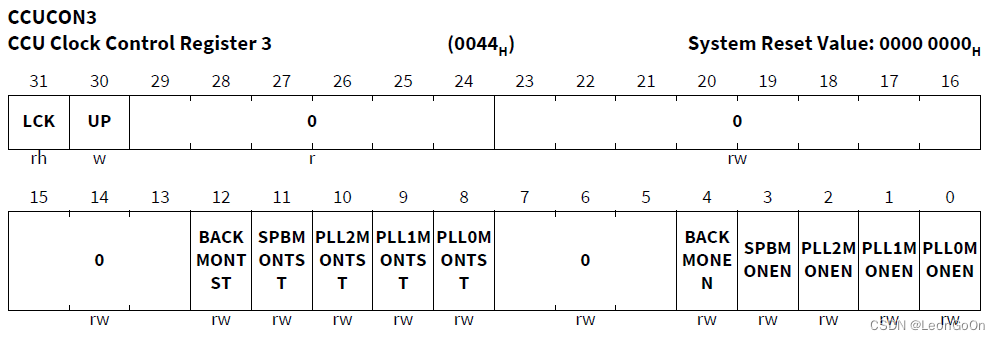

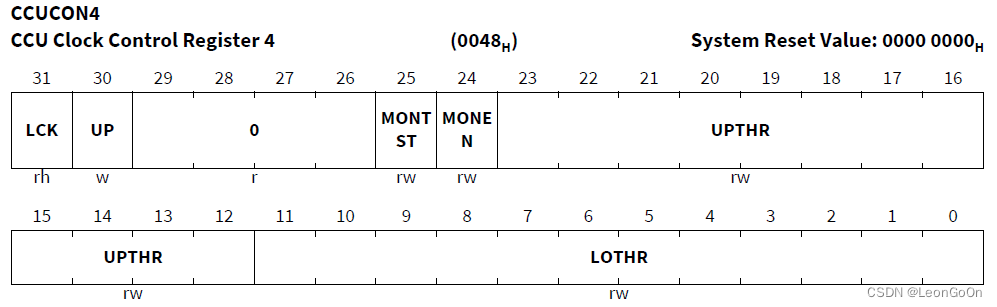

CCU模块相关的寄存器:

LPDIV寄存器控制了在Lower Power模式下一下XXX模块的时钟频率统一分配控制。

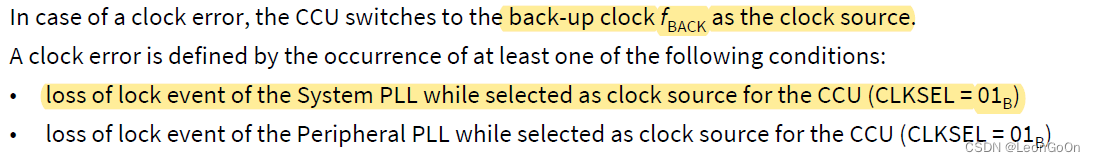

4. Clock Emergency Behavior

在发生一些Clock Emergency情况时,CCU会讲时钟源切换到fback。

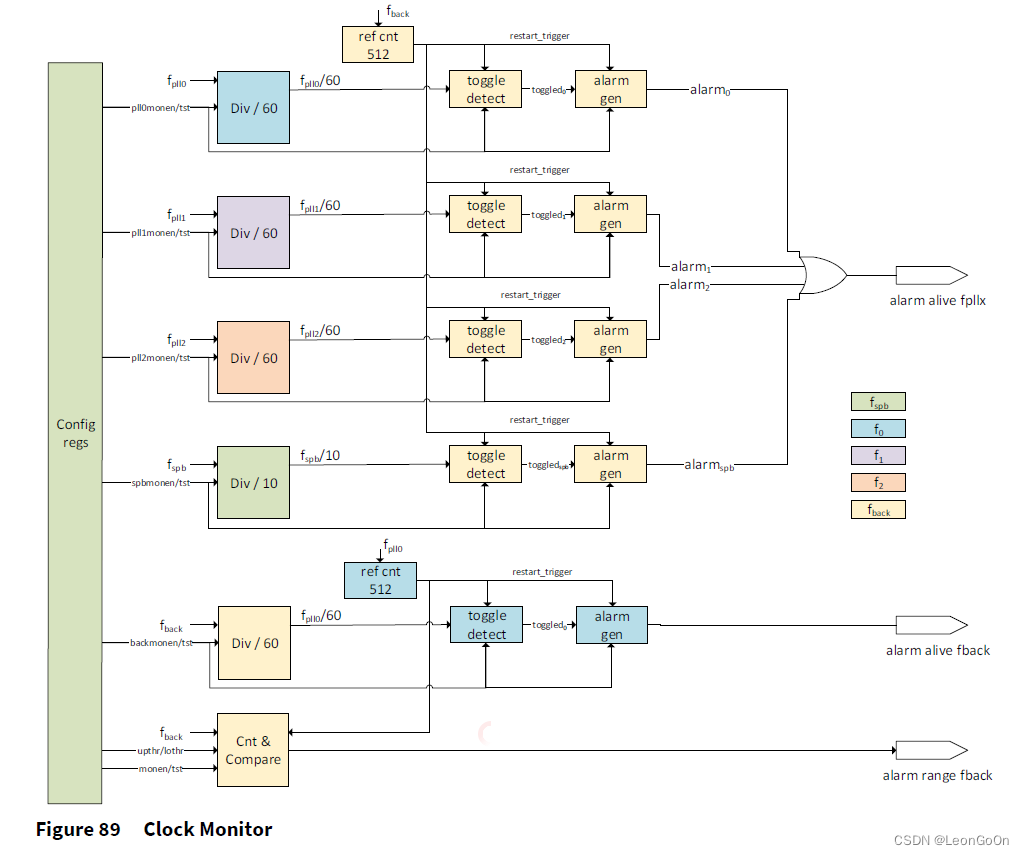

5. Clock Monitoring

![]()

为了安全起见,对一些重要的时钟源进行监控,监控的机理是在每一次监控脉冲过程中,监控器以监控时钟频率来观察输入时钟是否有电平切换,如果有则认为其是有效的,所以这就需要监控时钟的频率要大于监控的频率。

Back-Up Clock的监控用的监控时钟是fpll0,因为Back-Up Clock作为了一些重要功能监控的时钟,对其时钟的监控会要求的更严格,不仅仅是检查其有或无,还得检查其频率是否合理。

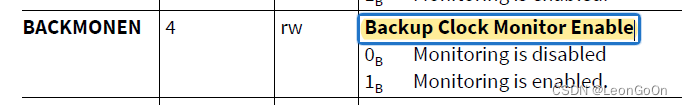

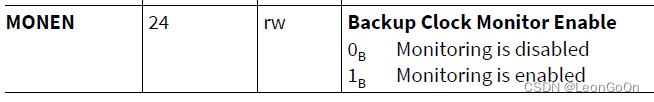

相关寄存器:

BACKMONEN寄存器是检测Back-Up Clock的有无,MONEN寄存器是检测Back-Up Clock的频率范围是否合理。

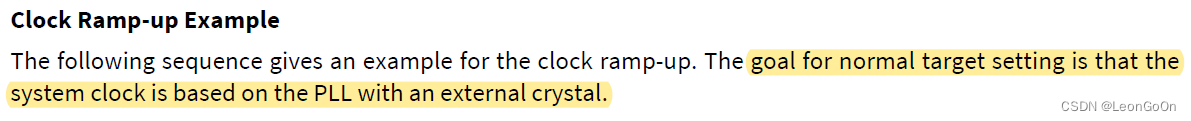

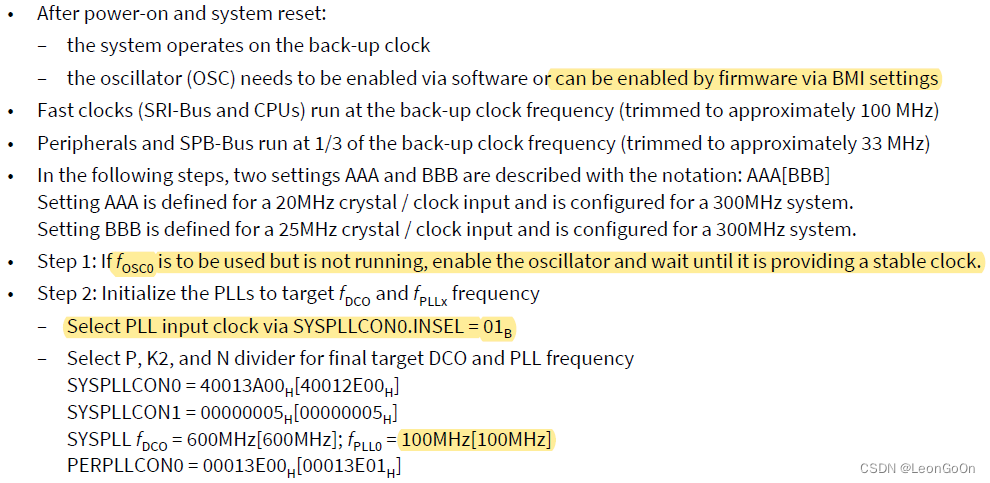

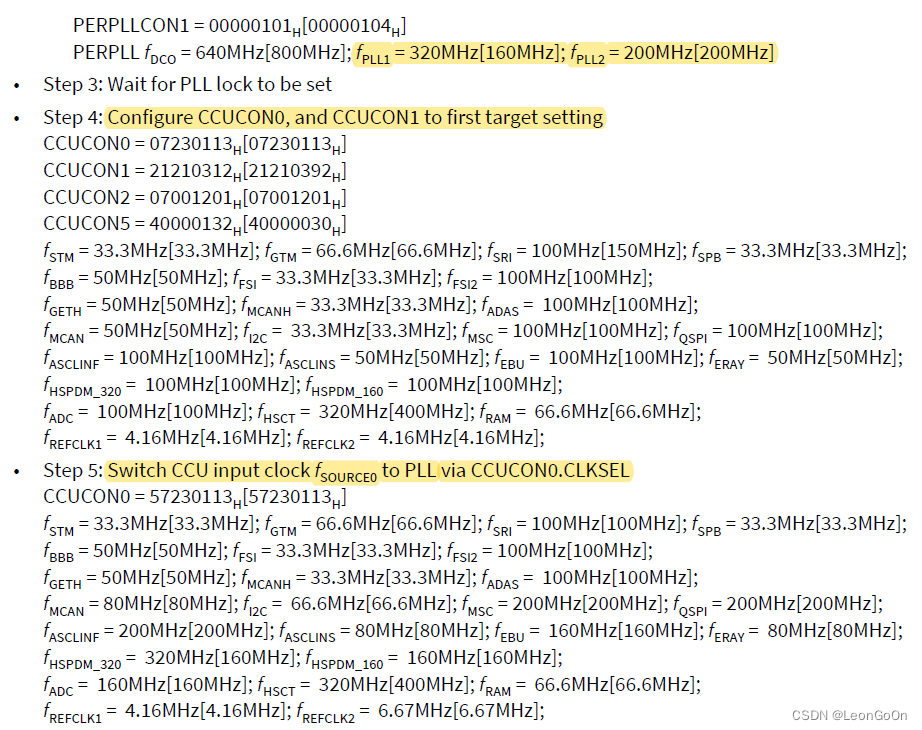

6. Clock Ramp-up Example

四、参考文档

1. 《TC3xx User Manual Partpdf》

本文详细介绍了AURIX2G系列MCU中的时钟系统,包括版本控制、主要模块(如外部输入时钟源、PLL倍频、时钟分布和紧急行为)、功能概述以及监控方法,以TC3xxUserManualPartpdf为主要参考文档。

本文详细介绍了AURIX2G系列MCU中的时钟系统,包括版本控制、主要模块(如外部输入时钟源、PLL倍频、时钟分布和紧急行为)、功能概述以及监控方法,以TC3xxUserManualPartpdf为主要参考文档。

1286

1286

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?