DL_Feature的引入

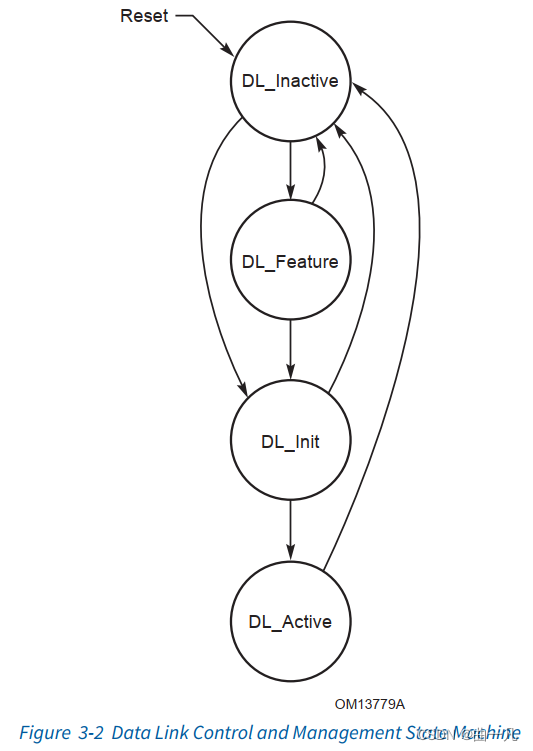

Data Link Control and Management State Machine在PCIe Gen4引入了DL_Feature这个状态,该状态主要用来协商PCIe link 两端是否支持新的DL Feature,目前为止DL Feature只引入了Scaled Flow Control 来提高Gen4及以上的效率。

DL_Feature 这个状态是可选的,当 Data Link Feature Extended Capability中Data Link Feature Exchange Enable field为0时状态机就会跳过DL_Feature子状态。

DL Link Feature Protocol 介绍

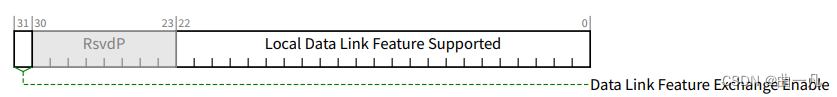

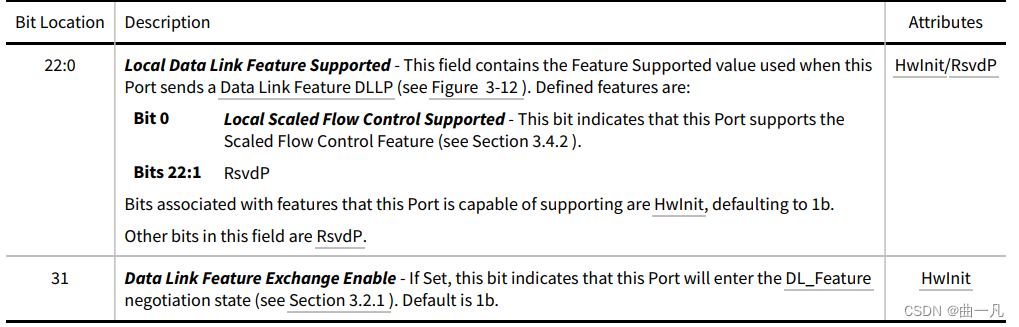

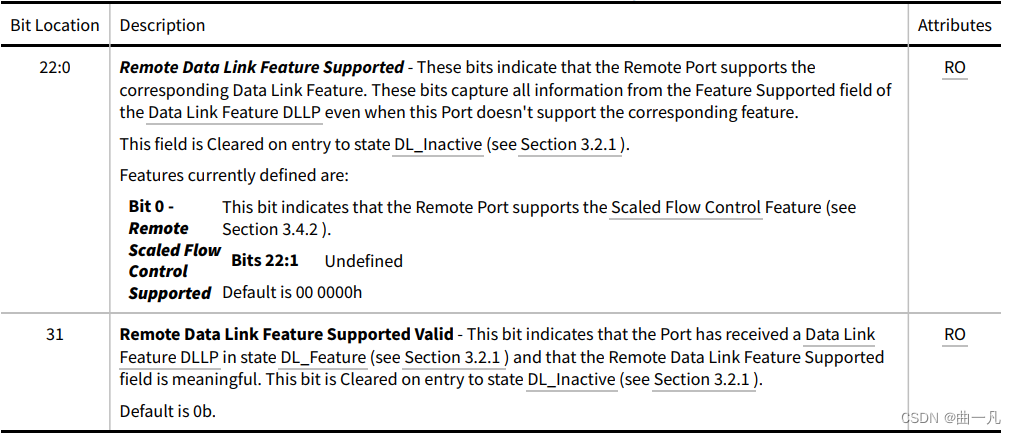

链路两端port在DL_Feature子状态通过DL Link Feature Protocol进行协商,判断两端port是否都支持DL_Feature, 为了支持DL_Link Feature,Data Link Feature Extended Capability中包含Data Link Feature Capabilities 和Data Link Feature Status寄存器:

Data Link Feature Capabilities Register:

Data Link Feature Status Register:

DL_Feature sub-status行为

- 进入DL_Feature:

- Remote Feature Supported valid 和Remote Feature Supported 都要设置都应该为0.

- 在DL_Feature子状态:

- PCIe Link 两端发送DL_Feature DLLP 进行协商,发送的Feature Supported 域要与Data Link Feature Capabilities Register中Local Feature Supported Field 一致,Feature Ack要与Data Link Feature Status Register中Remote_Data_Link_Feature_Supported_Valid保持一致, Remote_Data_Link_Feature_Supported 表示收到的DL_feature 中的Feature_Support 信息有效。

- 退出DL_Feature:

- 收到InitFc1 DLLP

- 收到Feature Ack

- 收到MR_IOV Init DLLP

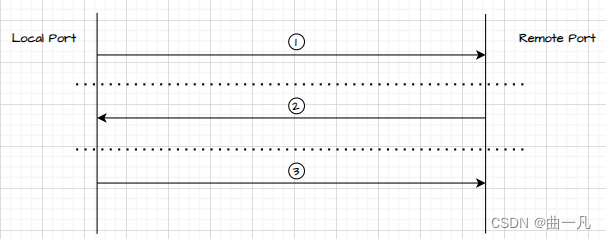

下面以一个例子来具体说明DL_Feature Protocol:

Example: Local Port Initial DL Link Feature Protocol

Step 1.

- Local Port transmit DL Link Feature DLL with DL Feature Supported bit equal to Data Link Feature Field in Data Link Control Capability Register

- DL_Feature ACK = 0

Step 2.

- Local Port record Remote Feature Supported bit, if Remote Data Link Feature Supported Valid is zero.

- Check Remote Feature Ack from remote Port.

Step 3.

- Local Port transmit Remote Feature Ack equal to the Remote_Data_Link_Feature_Supported_Valid recorded from Step 2 to Remote Port.

Note: 只有当为Remote_Data_Link_Feature_Supported_Valid零的时候port才会去采样对端发来的DL_feature中feature support信息.

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?