一.理论

Mearly型:输出由当前状态和输入共同决定

Moore型:输出只与当前状态有关

ps:状态跳转均与输入和当前状态有关

二.代码区别

2.1Mearly型输出:

always@(posedge sclk or negedge rst_n)

if(!rst_n)

c_out <= 1'b0;

else if(state == S4 && c_in == 1'b0)

c_out <= 1'b1;

else

c_out <= 1'b0;

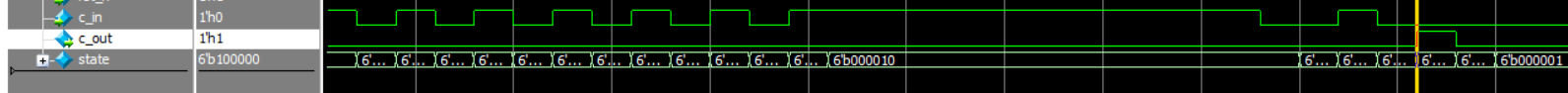

Modelsim仿真结果:检测到10010序列立刻输出检测信号c_out

2.2Moore型输出:

always@(posedge sclk or negedge rst_n)

if(!rst_n)

c_out <= 1'b0;

else if(state == S5)

c_out <= 1'b1;

else

c_out <= 1'b0;

Modelsim仿真结果:检测到10010序列输出检测信号c_out比Mealy型晚一拍

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4537

4537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?