一、安装vivado与ise14.7

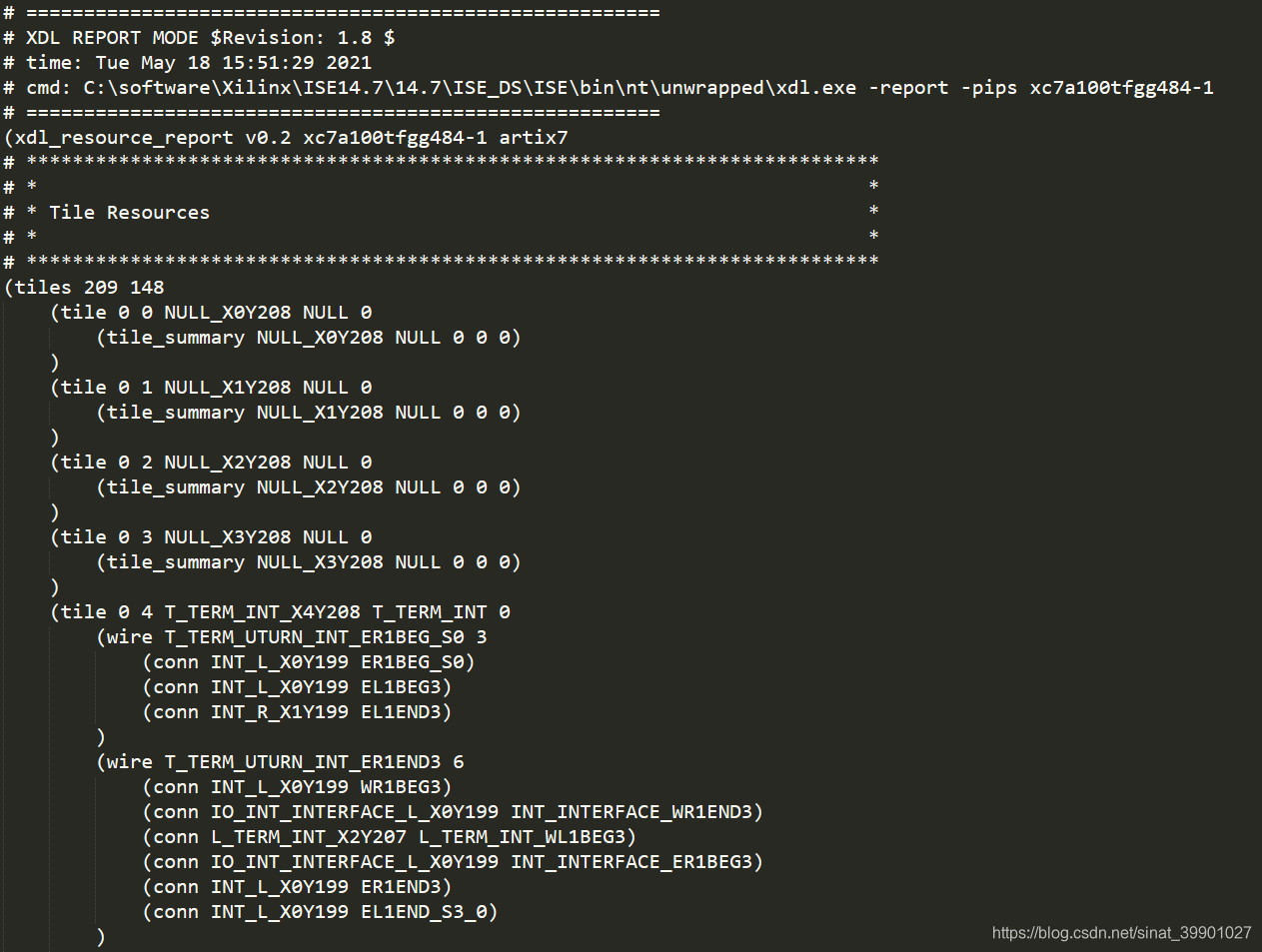

二、打开ise命令行模式,执行下面的命令获得xdlrc文件,生成的文件位于ise安装路径,内容如下图所示。(生成的文件较大,执行一两秒后手动终止,先不要生成完整的文件)

xdl -report -pips <part> // part为具体芯片型号,例如xc7a100tfgg484

三、从生成的文件中提取SM中的连接关系,将描述单个SM片段复制出来,用下面的程序提取连接关系

import numpy as np

import re

class SwitchBox():

def __init__(self, file: str):

self.node_name: dict = {}

self.edge_index: array[2, E] = np.empty([2, 0], dtype=int)

self.node_attr: array[n] = np.empty([0, ], dtype=int)

self.edge_attr: array[E] = np.empty([0, ], dtype=int)

self.pip_type: dict = {"->": 0, "=-": 1}

self.node_type: dict = {"other": 0, "1": 1, "2": 2, "4": 3, "6": 4, "LH": 5, "LV": 6}

self._extra_attr(file)

def _extra_attr(self, file: str):

pip_pat = "\(pip .* (.*) (.*) (.*)\)"

with open(file, 'r') as fp:

for line in fp:

ret = re.search(pip_pat, line)

if (ret):

source = ret.group(1) # 一个pip连接的起点

source_id = self._node_identify(source)

target = ret.group(3)

target_id = self._node_identify(target) # 一个pip连接的终点

pip = ret.group(2)

self._pip_identify(pip)

self.edge_index = np.append(self.edge_index, [[source_id], [target_id]], axis=1)

# 将节点变为数字序号

def _node_identify(self, node_name: str):

type_pat = "^([A-Z]{2})(.).*"

ret = re.search(type_pat, node_name)

direct = ret.group(1)

n_type = ret.group(2)

if direct in self.node_type:

node_type = self.node_type[direct]

elif n_type in self.node_type:

assert direct in ["EE", "SS", "WW", "NN", "NE", "SE", "NW", "SW",

"ER", "SR", "WR", "NR", "EL", "SL", "WL", "NL"]

node_type = self.node_type[n_type]

else:

node_type = self.node_type["other"]

if node_name in self.node_name:

node_id = self.node_name[node_name]

else:

node_id = len(self.node_name)

self.node_name[node_name] = node_id

self.node_attr = np.append(self.node_attr, [node_type], axis=0)

assert self.node_attr[node_id] == node_type

return node_id

def _pip_identify(self, pip_name: str):

assert pip_name in self.pip_type

pip_type = self.pip_type[pip_name]

self.edge_attr = np.append(self.edge_attr, [pip_type], axis=0)

return 1

# 找到终点为某个节点的pip的起点

def find_source(edge_index, target) -> np.ndarray:

idx = np.zeros(shape=(edge_index.shape[1], ), dtype=bool)

for t in target:

temp = (edge_index[1] == t)

idx = (idx | temp)

return edge_index[0][idx]

def find_key(dict_, value):

value_idx = list(dict_.values()).index(value)

keys = list(dict_.keys())[value_idx]

return keys

SM = SwitchBox("./test.xdlrc") //

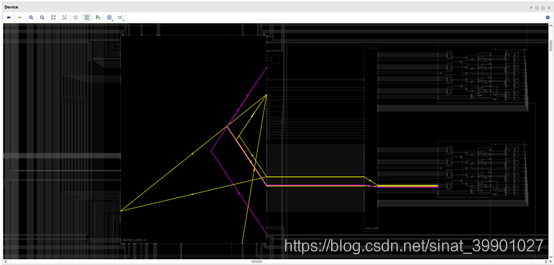

四、在vivado中标记选择的路径,通过下面的命令打开器件

link_design -part xc7a100tfgg484-1

点击下面的按钮显示布线资源,然后高亮选的路径

6663

6663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?