1 协议介绍

本文主要基于最新的AMBA 5 AHB协议规范做解析并根据真实使用经历列举仿真介绍。

AMBA AHB是一个适用于高性能综合设计的总线接口。它定义了组件之间的接口,如主组件、互连组件和从组件。

AMBA AHB实现高性能、高时钟频率系统所需的功能,包括:

- Burst 传输

- 单时钟沿操作

- Non-tistate 实验

- 数据位宽支持64、128、256、512和1024。

最常见的AHB从设备是内部memory设备、外部memory接口和高带宽外设。尽管低带宽外设可以作为AHB从设备,但出于系统性能的原因,它们通常驻留在AMBA高级外设总线(APB)上。高性能AHB和APB之间的桥接使用AHB从机完成,称为APB桥接。

图1展示了一个AHB Master 外挂3个AHB Slave,总线互联逻辑包括一个地址译码模块和slave-to-master的多路选择器,地址译码模块将master发送的地址转换为合适的SEL信号选择一个从设备,多路选择器将各个slave的输出数据合理的选择给master,注意,AHB总线可以有多个master。

1.1 Master

以典型的master为例介绍接口信号。

INPUT信号:

- HREADY:Slave给的,表示这次传输完成了。可以进行下次传输。

- HRESP:Slave给的一些额外的状态信息,比如成功,失败等等。

- HRESETn:全局复位信号,低有效,该复位可以直接和系统总线复位连接。

- HCLK, :全局时钟信号。

- HRDATA[31:0]:Slave端口送来的读数据。

OUTPUT信号:

- HADDR[31:0] :AHB总线地址。

- HWRITE:读写指示信号,1是写,0是读。

- HSIZE[2:0]:用于指示每次传输的数据大小。

- HBURST[2:0]:用于规定burst传输次数和地址递增方式。

- HPROT[3:0]:保护控制信号,用于指示本次传输类型。

- HTRANS[1:0]:用于指示传输类型,一共有四种:IDLE/BUSY/NONSEQUENTIAL/SEQUENTIAL,分别为空闲、忙、非连续、连续传输。

- HMASTERLOCK:锁定master传输,锁定期间master无法被打断。

- HWDATA[31:0]:写数据,最大支持1024bits,建议在32~256bits之间。

- HNONSEC:指示当前传输是否安全。

- HEXCL:用于指示该传输是否为独占传输(Exclusive Access)。

- HWSTRB:写数据字节使能,位宽为HWDATA的位宽除以8,最大128.

1.2 Slave

slave端使用从地址译码器送来的HSELx选择信号来响应bus传输。

slave端输出信号:

- HRDATA:读数据,最大位宽为1024bits,建议在32~256bits之间。

- HREADYOUT: Slave端设备准备就绪信号,用法和APB的PREADY类似。

- HRESP: Slave端设备的应答信号,表明当前传输是否成功,“1”错误。

- HEXOKAY:表示独占传输是否成功。

译码器信号:

- HSELx :Slave设备选择信号,用法和APB的PSEL类似。当Slave被选中且为非IDLE传输时,HSELx必须和地址、控制信号同一拍有效。

多路选择器信号:

- HREADY:该信号由总线内部产生,用于通知Master和Slave上次传输已经结束,总线已经准备就绪开始下一次传输。

2 Transfer传输

2.1 基本传输

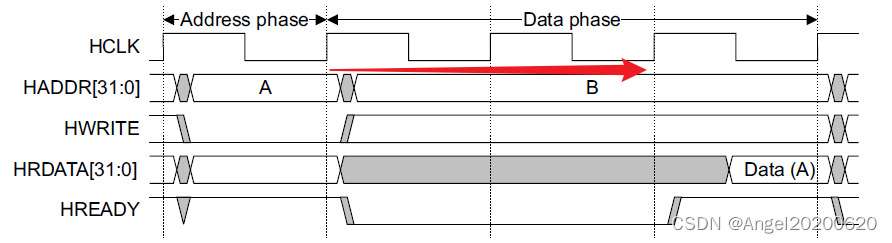

AHB传输分两个阶段:地址阶段和数据阶段:

- 地址阶段:HWRITE、HADDR等控制信号同一拍有效,随后HREADY拉高表示当前地址已生效。

- 数据阶段:HWDATA、HRDATA等和数据相关的信号有效,表示数据读写的开始,数据阶段可能会跨多个HCLK时钟周期,根据传输数据量大小而定。

HWRITE信号控制数据传输方向:

- HWRITE=1, 表示一次写传输,master将数据打到HWDATA[31:0]总线上。

- HWRITE=0, 表示一次读传输,slave将数据打到HRDATA[31:0]总线上。

- 下图是AHB总线单次读写传输,包括立即读立即写。

读传输:

写传输:

在没有等待状态的简单传输中:

- 在HCLK的上升沿之后,master将地址和控制信号驱动到总线上。

- 然后slave在HCLK的下一个上升沿上采样地址和控制信息。

- 在slave对地址和控制信号进行采样之后,它可以驱动READYOUT响应。这个响应是在HCLK的第三个上升沿采样。

这个简单的示例演示了在不同的时钟期间传输的地址和数据阶段是如何发生的。针对任何一次传输,地址阶段都发生数据阶段之前。这种重叠地址和数据是总线流水线化的基础,能够实现高性能的操作,并且可以为slave提供足够的时间对传输做出响应。

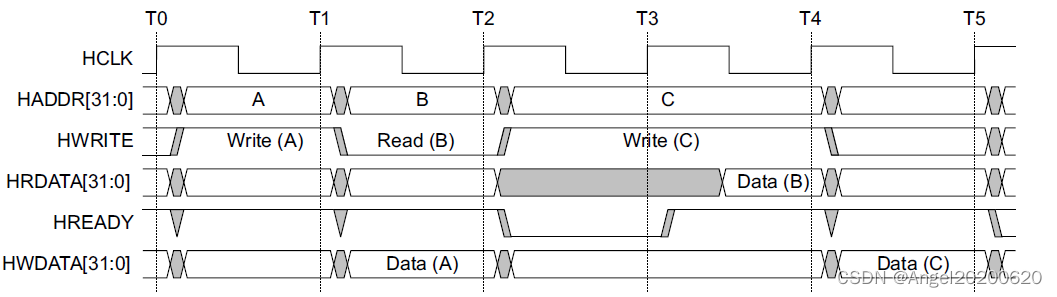

从机可以在任何传输中插入等待状态,以获得额外的完成时间。每个slave都有一个在传输的数据阶段驱动的HREADYOUT信号。连接器结合来自所有slave的HREADYOUT信号,生成一个用于控制的HREADY信号, 从而控制整个传输过程。

下图是插入等待的读写传输:

插入两个等待的读传输:

插入1个等待的写传输:

注意:地址阶段和数据阶段是可以pipeline的,如果多次连续传输,但是地址不同,可以采用如下图时序完成操作,在A的数据数据可以启动B的地址阶段。

2.2 传输类型

HTRANS[1:0]:

下图是表示NONSEQ, BUSY 和SEQ传输类型。

- T0-T1,从NONSEQ传输开始做4-beat读。

- T1-T2, master无法执行第二次突发并插入一个BUSY传输来延迟第二次突发,slave端返回第一次突发读数据。

- T2-T3, master准备发起第二次突发操作,所以SEQ传输被发起,master端会忽略slave端返回的任何读数据。

- T3-T4, master端执行第三次突发,slave端返回第二次突发的数据。

- T4-T5, master执行最后一次突发,slave端无法完成传输所以使用HREADYOUT来插入一个周期等待。

- T5-T6, slave端返回第三次突发的读数据。

- T6-T7, slave端返回最后一次突发的读数据。

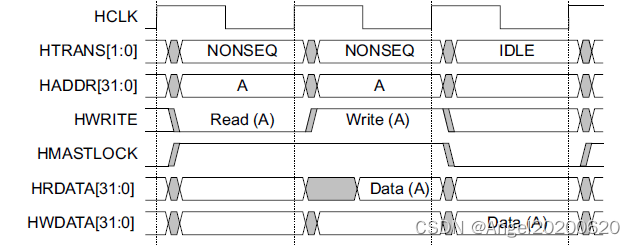

3.3 Locked transfers

如果master需要锁定访问,那么它还必须使用HMASTLOCK信号。这个信号向任何slave端表明当前的传输序列是不可分割的,因此必须在处理其他传输之前处理。

典型的锁定传输被用于保持信号的完整性,确保slave端设备在读写之间没有任何的其他操作。如下图所示 HMASTLOCK 信号

注意:一次锁定传输后,推荐master端插入一次IDLE传输。

多数的slave端不需要实现HMASTLOCK功能,只需要执行按顺序接收的指令即可,slave端可以被多个master访问,例如,一个Multi-Port Memory Controller(MPMC) 就必须实现HMASTLOCK信号。

并且在最开始IDLE数据传输时,也允许master拉高HMASTERLOCK ,在非IDLE状态下拉低HMASTLOCK信号。

3.4 Transfer size

HSIZE[2:0] 代表数据传输的大小,下表列出了传输大小

| HSIZE[2:0] | size bits | Description |

|---|---|---|

| 000 | 8 | Byte |

| 001 | 16 | Halfword |

| 010 | 32 | Word |

| 011 | 64 | Doubleworld |

| 100 | 128 | 4-word line |

| 101 | 256 | 8-word line |

| 110 | 512 | - |

| 111 | 1024 | - |

注意:

传输大小由HSIZE决定,必须小于等于总线数据位宽,例如,一个32bit的数据位宽,HSIZE必须使用0b000, 0b001, or 0b010.

使用HSIZE结合HBURST,来决定地址边界。

3.5 Burst Opteration

busrt 传输支持两种,递增和wrapping busrt.

- 递增的突发访问顺序位置,突发中每个传输的地址都是递增的地址。

- wrapping busrts 突发的个数由HBURST和HSIZE控制,比如一个4-beat突发,传输起始地址为0x34, 那么传输地址为0x34,0x38,0x3c, and 0x30。

- 突发信号编码如下:

| HbURST[2:0] | TYPE | Description |

|---|---|---|

| 000 | SINGLE | single transfer burst |

| 001 | INCR | Incrementing burst of undefined length |

| 010 | WRAP4 | 4-beat wrapping burst |

| 011 | INCR4 | 4-beat increenting burst |

| 100 | WRAP8 | 8-beat wrapping burst |

| 101 | INCR8 | 8-beat incrementing burst |

| 110 | WRAP16 | 16-beat wrapping burst |

| 111 | INCR16 | 16-beat incrementing burst |

注意:所有的burst传输必须是地址边沿对齐传输,例如,word 传输必须对齐word地址边沿HADDR[1:0] == 0b00.

598

598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?