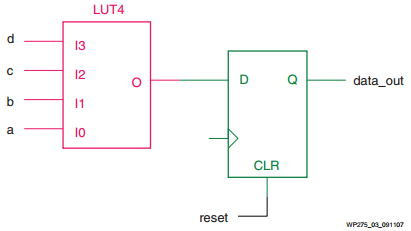

wp275 主要内容讲的是flip-flop怎么合理的应用。

1、常用的代码写法

process (clk, reset)

begin

if reset=‘1’ then

data_out <= ‘0’;

elsif clk’event and clk=’1’ then

data_out <= a and b and c and d;

end if;

end process;

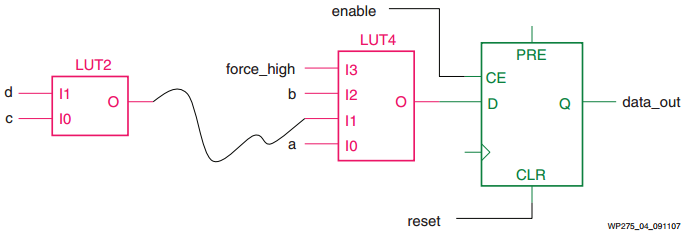

2、添加一些控制信号的情况

process (clk,reset)

begin

if reset=’1’ then

data_out <= ’0’;

elsif clk’event and clk=’1’ then

if enable=’1’ then

if force_high=’1’ then

data_out <= ’1’;

else

data_out <= a and b and c and d;

end if;

end if;

end if;

end process;

3、对于2的一些讨论

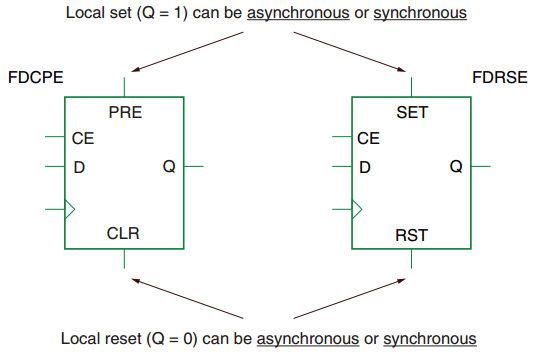

其实xilinx的Flip-Flop有以下特性:

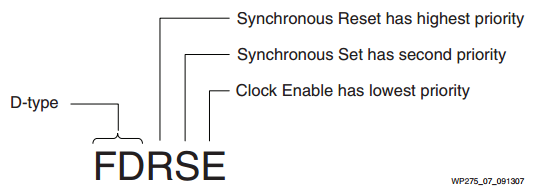

这里说一下FDRSE(FDCPE类似,FDRSE懂了,FDCPE也懂了)

Xilinx的Flip-Flop就是这种FDRSE。对于在做综合时,reset优先级最高,set优先级中间,时钟时能优先级最低。

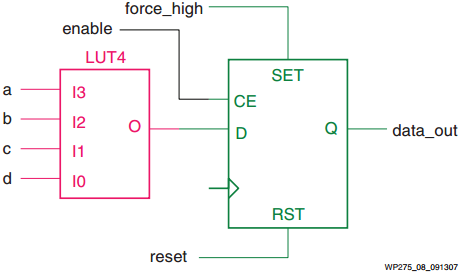

对于2的情况,可以将代码做如下修改:

process (clk)

begin

if clk’event and clk=’1’ then

if reset=’1’ then

data_out <= ’0’;

else

if force_high=’1’ then

data_out <= ’1’;

else

if enable=’1’ then

data_out <= a and b and c and d;

end if;

end if;

end if;

end if;

end process;

1、异步复位改成了同步,减少亚稳态。

2、reset等级最高,放在了第一个if的判断条件里。

3、set等级第二,foce_high放在第二层嵌套的if else里。

4、时钟时能等级最低,因此enable放在第三层嵌套的if else里。

综合后的结果如下:

相比2的代码写法,节省了一个LUT。

2196

2196

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?