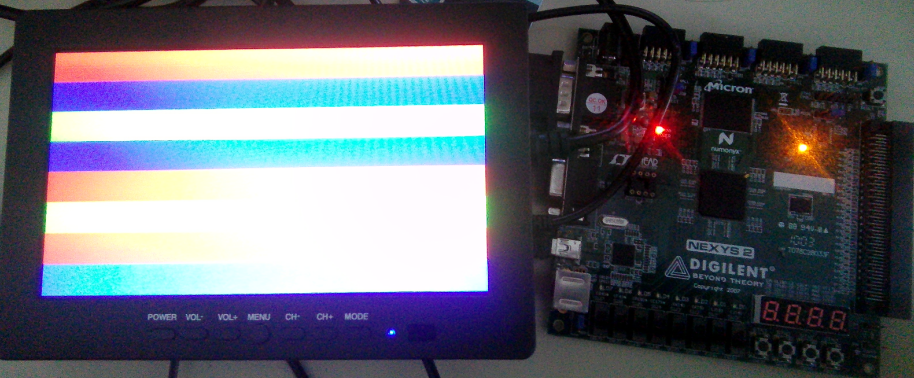

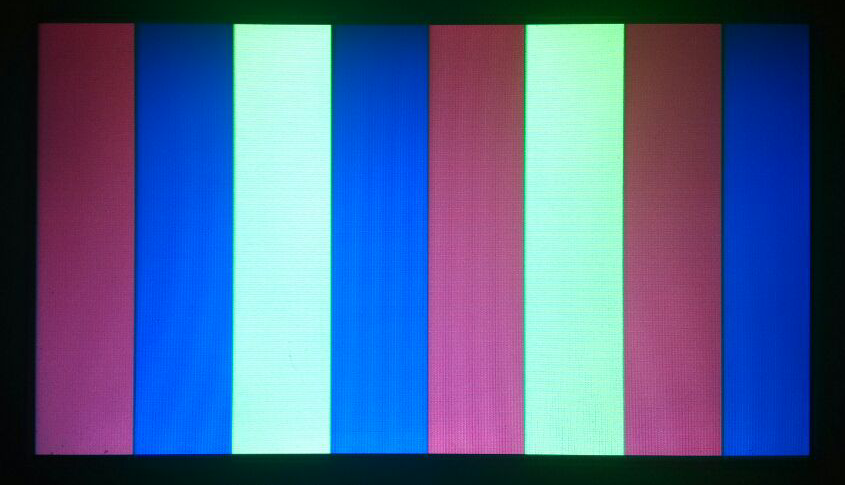

基本功能:

1、通过FPGA板的VGA接口在显示器上分别显示不同颜色的横向、竖直条纹图案,横向条纹和竖直条纹的切换通过FPGA板上的按键实现。

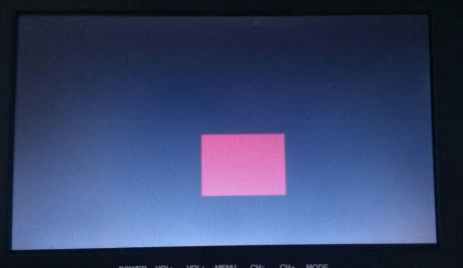

2、通过VGA控制器,在屏幕上显示640*480的单色背景,并在该背景上叠加一个小方块,该小方块能够在屏幕上上下左右移动,实现屏幕保护的效果。3、VGA单色的背景色自定,小方块的大小自定;

4、该小方块能够按照一定的轨迹在屏幕上运行,速度适中。

大三下学期的实验,贴出代码仅供参考:

1、分频模块:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity fenpin is

port

(

clk_fp_in :in std_logic;

reset_fp :in std_logic;

clk_fp_out :out std_logic;

clk_fp_dis :out std_logic

);

end fenpin;

architecture Behavioral of fenpin is

signal clk_signal :std_logic;

signal clk_dis :std_logic;

signal cnt:integer range 999999 downto 0 :=0;--移动

begin

process(clk_fp_in,reset_fp)

begin

if(reset_fp='1')then

clk_signal<= '0';

elsif(clk_fp_in'eventand clk_fp_in = '1')then

if(clk_signal= '0')then

clk_signal<= '1';

else

clk_signal<= '0';

endif;

endif;

endprocess;

clk_fp_out<= clk_signal;

process(clk_fp_in,reset_fp)

begin

if(reset_fp='1')then

cnt<= 0;

clk_dis<= '0';

elsif(clk_fp_in'eventand clk_fp_in = '1')then

if(cnt< 499999)then

cnt<= cnt+1;

clk_dis<= '1';

elsif(cnt= 999999)then

cnt<= 0;

else

cnt<= cnt+1;

clk_dis<= '0';

endif;

endif;

endprocess;

clk_fp_dis<= clk_dis;

end Behavioral;

2、VGA控制模块:

library IEEE;

useIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entity sync is

port( clk_sync :instd_logic;

reset_sync :in std_logic;

V_sync :out std_logic;

H_sync :out std_logic;

Ready_sync :out std_logic;

Lie_Add_sync :out integer range 800 downto 0;

Hang_Add_sync :out integer range 525 downto 0

);

end sync;

architectureBehavioral of sync is

signal count_h:integer range 800 downto 0;

signal count_v:integer range 525 downto 0;

signal isReady :std_logic;

begin

process (clk_sync,reset_sync)

begin

if(reset_sync='1')then

count_h <= 0;

H_sync <= '0';

elsif(clk_sync'event and clk_sync='1')then

if(count_h=799)then

count_h <= 0;

else

count_h <=count_h + 1;

if(count_h <96)then

H_sync <= '0';

else

H_sync <= '1';

end if;

end if;

end if;

end process;

process (clk_sync,reset_sync)

begin

if(reset_sync='1')then

count_v <= 0;

V_sync <= '0';

elsif(clk_sync'event and clk_sync='1')then

if(count_v = 524)then

count_v <= 0;

elsif(count_h=799)then

count_v <=count_v + 1;

else

if(count_v <3)then

V_sync <='0';

else

V_sync <='1';

end if;

end if;

end if;

end process;

process (reset_sync,clk_sync)

begin

if(reset_sync='1')then

isReady <= '0';

Lie_Add_sync <= 0;

Hang_Add_sync<= 0;

elsif(clk_sync'event and clk_sync='1')then

if((count_h >144)and(count_h < 785)and(count_v > 34)and(count_v < 515))then

isReady <= '1';

Lie_Add_sync <=count_h - 145;

Hang_Add_sync<=count_v - 35;

else

isReady <= '0';

Lie_Add_sync <=0;

Hang_Add_sync<=0;

end if;

end if;

end process;

Ready_sync <= isReady;

end Behavioral;

3、VGA显示模块:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

entityvga_control is

port( clk_vga :instd_logic;

signal_dis :in std_logic;

reset_vga :in std_logic;

choose_vga :in std_logic;

Ready_vga :in std_logic;

Lie_Add_vga :in integer range 800 downto 0; --0~640

Hang_Add_vga:in integer range 525downto 0; --0~480

rom_add :out std_logic_vector (13 downto 0);

rom_data :in std_logic_vector (7 downto 0);

RGB_vga_out :out std_logic_vector (7 downto 0);

RGB_vga_in :in std_logic_vector (7 downto 0)

);

end vga_control;

architectureBehavioral of vga_control is

type state is(s0,s1,s2,s3);--状态机类型

signalcurrent:state;

signal x:integerrange 639 downto 0 :=100;--移动

signal y:integerrange 479 downto 0 :=100;--移动

signalx_signal:std_logic;

signaly_signal:std_logic;

signal move :std_logic;

begin

process(choose_vga,reset_vga)

begin

if(reset_vga ='1')then

current <=s0;

elsif(choose_vga'event andchoose_vga ='0')then--检测到下降沿才开始响应

case current is

when s0 =>

current <=s1;

when s1 =>

current <=s2;

when s2 =>

current <=s3;

when s3 =>

current <=s0;

when others =>

current <=s0;

end case;

end if;

end process;

process (clk_vga,reset_vga)

begin

if(reset_vga='1')then

RGB_vga_out <="00000000";

move <='1';

elsif(clk_vga'event and clk_vga ='1')then

if(Ready_vga='1')then --可以显示

case current is

when s0=>--竖条纹

caseLie_Add_vga is --0~640

when0 to 79 =>RGB_vga_out <= "11100000";--红,蓝,绿,蓝,红,绿, 红,蓝

when 80 to 159 =>RGB_vga_out <= "00000011";

when160 to 239 => RGB_vga_out <="00011100";

when240 to 319 => RGB_vga_out <="00000011";

when320 to 399 => RGB_vga_out <="11100000";

when400 to 479 => RGB_vga_out <="00011100";

when480 to 559 => RGB_vga_out <="11100000";

when560 to 639 => RGB_vga_out <="00000011";

whenothers => RGB_vga_out<= "00000000";

endcase;

when s1=>--横条纹

caseHang_Add_vga is --0~480

when0 to 59 =>RGB_vga_out <= "11100000";--红,蓝,绿,蓝,红,绿, 红,蓝

when60 to 119 => RGB_vga_out <= "00000011";

when120 to 179 => RGB_vga_out <="00011100";

when180 to 239 => RGB_vga_out <="00000011";

when240 to 299 => RGB_vga_out <="11100000";

when300 to 359 => RGB_vga_out <="00011100";

when360 to 419 => RGB_vga_out <="11100000";

when420 to 479 => RGB_vga_out <="00000011";

whenothers => RGB_vga_out<= "00000000";

endcase;

when s2=>--调色观察

if(Hang_Add_vga> y and Hang_Add_vga< 128+y and Lie_Add_vga>x andLie_Add_vga < 128+x )then

move <='0';

RGB_vga_out<= RGB_vga_in;

else

move <='1';

RGB_vga_out<= "00000000";

endif;

when s3=>--屏保

if(Hang_Add_vga>y and Hang_Add_vga< 128+y and Lie_Add_vga>x and Lie_Add_vga <128+x)then

move <='0';

rom_add<= conv_std_logic_vector((Hang_Add_vga-y)*128 + Lie_Add_vga-x,14);

RGB_vga_out<= rom_data;

else

move <='1';--使用这个信号只是为了让扫描完一次再移动,但由于背景跟图片颜色不一样,还是有拖影,所以,这个信号可以不用!

RGB_vga_out<= "00000000";

endif;

when others=>

RGB_vga_out<= "00000000";

end case;

end if;

end if;

end process;

--屏保图片的移动实现

process(reset_vga,signal_dis)

begin

if(reset_vga='1')then

x_signal <='1';

x <=0;

elsif(signal_dis'event andsignal_dis ='1')then

if(move='1')then

if(x_signal ='1')then

if(x<634-128)then

x<= x+1;

else

x<= x-1;

x_signal<='0';

end if;

else

if(x<1)then

x<= x+1;

x_signal<='1';

else

x<= x-1;

end if;

end if;

end if;

end if;

end process;

process(reset_vga,signal_dis)

begin

if(reset_vga='1')then

y_signal <='1';

y <=0;

elsif(signal_dis'event andsignal_dis ='1')then

if(move='1')then

if(y_signal ='1')then

if(y<479-128)then

y<= y+1;

else

y<= y-1;

y_signal<='0';

end if;

else

if(y<1)then

y<= y+1;

y_signal<='1';

else

y<= y-1;

end if;

end if;

end if;

end if;

end process;

end Behavioral;

5、顶层模块:

library IEEE;

useIEEE.STD_LOGIC_1164.ALL;

entity VGA_top is

port( clk :instd_logic; --50M时钟输入

reset :in std_logic; --复位,高有效

choose :in std_logic;

--pll_led :out std_logic; --提示PLL正常工作的LED

V :outstd_logic;

H :outstd_logic;

RGB :out std_logic_vector (7 downto 0);

RGB_top :in std_logic_vector (7 downto 0)

);

end VGA_top;

architectureBehavioral of VGA_top is

component fenpin

port( clk_fp_in : in std_logic;

reset_fp :in std_logic;

clk_fp_out :out std_logic;

clk_fp_dis :out std_logic

);

end component;

component sync

port( clk_sync :instd_logic;

reset_sync :in std_logic;

V_sync :out std_logic;

H_sync :out std_logic;

Ready_sync :out std_logic;

Lie_Add_sync :out integer range 800 downto 0;

Hang_Add_sync :out integer range 525 downto 0

);

end component;

component vga_control

port( clk_vga :instd_logic;

signal_dis :in std_logic;

reset_vga :in std_logic;

choose_vga :in std_logic;

Ready_vga :in std_logic;

Lie_Add_vga :in integer range 800 downto 0; --0~640

Hang_Add_vga:ininteger range 525 downto 0; --0~480

rom_add :out std_logic_vector (13 downto 0);

rom_data :in std_logic_vector (7 downto 0);

RGB_vga_out :out std_logic_vector (7 downto 0);

RGB_vga_in :in std_logic_vector (7 downto 0)

);

end component;

COMPONENT rom1

PORT (

clka : IN STD_LOGIC;

addra : IN STD_LOGIC_VECTOR(13 DOWNTO 0);

douta : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END COMPONENT;

signal clk_sig :std_logic;

signal clk_dis :std_logic;

signal Ready :std_logic;

signal Lie_Add :integer range 800 downto0; --0~640

signal Hang_Add:integer range 525 downto0; --0~480

signal rom_add_signal:STD_LOGIC_VECTOR(13 DOWNTO 0);

signal rom_data_signal:STD_LOGIC_VECTOR(7DOWNTO 0);

begin

u1:fenpin

port map( clk,

reset,

clk_sig,

clk_dis

);

u2:sync

port map( clk_sig,

reset,

V,

H,

Ready,

Lie_Add,

Hang_Add

);

u3:vga_control

port map( clk_sig,

clk_dis,

reset,

choose,

Ready,

Lie_Add,

Hang_Add,

rom_add_signal,

rom_data_signal,

RGB,

RGB_top

);

u4:rom1

PORT map( clk_sig,

rom_add_signal,

rom_data_signal

);

end Behavioral;

FPGA开发板截图:

1161

1161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?