声明:原文版权归属Intel®,这里仅作学习使用

来源:Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: System Programming Guide, Part 1

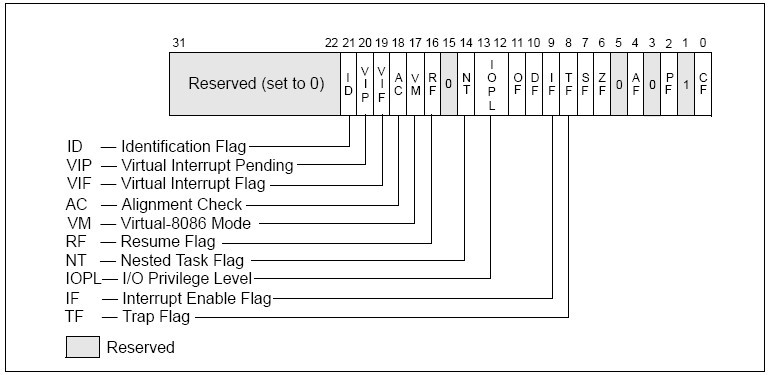

Chapter 2.3 SYSTEM FLAGS AND FIELDS IN THE EFLAGS REGISTER

EFLAGS寄存器中的系统标志位和字段

The system flags and IOPL field of the EFLAGS register control I/O, maskable hardware interrupts, debugging, task switching, and the virtual-8086 mode (see Figure 2-4). Only privileged code (typically operating system or executive code) should be allowed to modify these bits.

Figure 2-4. System Flags in the EFLAGS Register

The system flags and IOPL are:

-

TF Trap (bit 8) (陷阱标志位)— Set to enable single-step mode for debugging(单步调试模式); clear to disable single-step mode. In single-step mode, the processor generates a debug exception after each instruction(处理器在每个指令之后抛出一个debug异常). This allows the execution state of a program to be inspected after each instruction. If an application program sets the TF flag using a POPF, POPFD, or IRET instruction, a debug exception is generated after the instruction that follows the POPF, POPFD, or IRET.

-

IF Interrupt enable (bit 9)(中断使能位) — Controls the response of the processor to maskable hardware interrupt requests(控制对可屏蔽的硬件中断请求的响应) (see also: Section 5.3.2, “Maskable Hardware Interrupts”). The flag is set to respond to maskable hardware interrupts; cleared to inhibit(阻止) maskable hardware interrupts. The IF flag does not affect the generation of exceptions or nonmaskable interrupts (NMI interrupts)(不可屏蔽中断). The CPL, IOPL, and the state of the VME flag in control register CR4 determine whether the IF flag can be modified by the CLI, STI, POPF, POPFD, and IRET.

-

IOPL I/O privilege level field (bits 12 and 13)(I/O特权字段) — Indicates the I/O privilege level (IOPL) of the currently running program or task. The CPL of the currently running program or task must be less than or equal to the IOPL to access the I/O address space. (CPL必须小于或者等于IOPL)This field can only be modified by the POPF and IRET instructions when operating at a CPL of 0.(仅当执行在CPL0时,才可以由POPF和IRET指令修改)

The IOPL is also one of the mechanisms that controls the modification of the IF flag and the handling of interrupts in virtual-8086 mode when virtual mode extensions are in effect (when CR4.VME = 1). See also: Chapter 13, “Input/Output,” in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1.

-

NT Nested task (bit 14)(嵌套任务位) — Controls the chaining of interrupted and called tasks(控制对中断和调用的任务的链接). The processor sets this flag on calls to a task initiated with a CALL instruction, an interrupt, or an exception(处理器在处理由CALL指令开始的新任务,中断或者异常时设置该位). It examines and modifies this flag on returns from a task initiated with the IRET instruction(IRET指令返回时检查该位). The flag can be explicitly set or cleared with the POPF/POPFD instructions; however,changing to the state of this flag can generate unexpected exceptions in application programs.

See also: Section 6.4, “Task Linking.

-

RF Resume (bit 16) (恢复位)— Controls the processor’s response to instruction-breakpoint conditions. When set, this flag temporarily disables debug exceptions (#DB) from being generated for instruction breakpoints (although other exception conditions can cause an exception to be generated). When clear, instruction breakpoints will generate debug exceptions.(设置该位可关掉debug异常)

The primary function of the RF flag is to allow the restarting of an instruction following a debug exception that was caused by an instruction breakpoint condition. Here, debug software must set this flag in the EFLAGS image on the stack just prior to returning to the interrupted program with IRETD (to prevent the instruction breakpoint from causing another debug exception). The processor then automatically clears this flag after the instruction returned to has been successfully executed, enabling instruction breakpoint faults again. See also: Section 18.3.1.1, "Instruction-Breakpoint Exception Condition."

- VM Virtual-8086 mode (bit 17) (虚拟8086模式位)— Set to enable virtual-8086 mode; clear to return to protected mode.See also: Section 15.2.1, “Enabling Virtual-8086 Mode.”

- AC Alignment check (bit 18) (对齐检查位)— Set this flag and the AM flag in control register CR0 to enable alignment checking of memory references; clear the AC flag and/or the AM flag to disable alignment checking. An alignment-check exception is generated when reference is made to an unaligned operand, such as a word at an odd byte address or a doubleword at an address which is not an integral multiple of four. Alignment-check exceptions are generated only in user mode (privilege level 3). Memory references that default to privilege level 0, such as segment descriptor loads, do not generate this exception even when caused by instructions executed in user-mode.

The alignment-check exception can be used to check alignment of data. This is useful when exchanging data with processors which require all data to be aligned. The alignment-check exception can also be used by interpreters to flag some pointers as special by misaligning the pointer. This eliminates overhead of checking each pointer and only handles the special pointer when used.

-

VIF Virtual Interrupt (bit 19) (虚拟中断位)— Contains a virtual image of the IF flag. This flag is used in conjunction with the VIP flag. The processor only recognizes the VIF flag when either the VME flag or the PVI flag in control register CR4 is set and the IOPL is less than 3. (The VME flag enables the virtual-8086 mode extensions; the PVI flag enables the protected-mode virtual interrupts.) See also: Section 15.3.3.5, "Method 6: Software Interrupt Handling," and Section 15.4, "Protected-Mode Virtual Interrupts."

- VIP Virtual interrupt pending (bit 20)(虚拟中断等待位) — Set by software to indicate that an interrupt is pending; cleared to indicate that no interrupt is pending. This flag is used in conjunction with the VIF flag. The processor reads this flag but never modifies it. The processor only recognizes the VIP flag when either the VME flag or the PVI flag in control register CR4 is set and the IOPL is less than 3. The VME flag enables the virtual-8086 mode extensions; the PVI flag enables the protected-mode virtual interrupts.

See Section 15.3.3.5, "Method 6: Software Interrupt Handling," and Section 15.4, "Protected-Mode Virtual Interrupts."

-

ID Identification (bit 21)(ID位). — The ability of a program or procedure to set or clear this flag indicates support for the CPUID instruction.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?