本文重点是怎么根据ddr去配置参数和配置avalon总线接口数据位宽,更深层的参数细节及使用细节可以参考intel官方例程:

Intel® Cyclone® 10 GX官方开发板

在使用Altera(intel) FPGA(cyclone10)官方硬件开发板《Intel® Cyclone® 10 GX FPGA

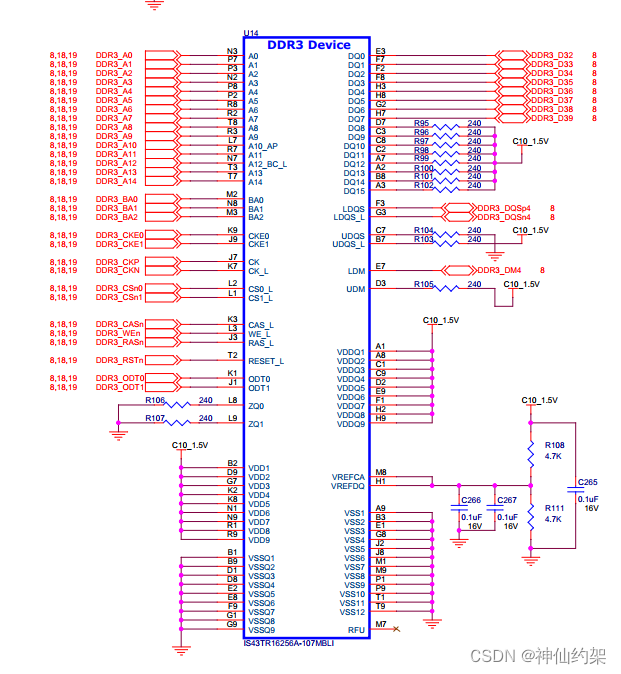

Development Kit》时会发现其共使用了3片DDR3 (IS43TR16256A-107MBLI),其中有40bitDQ连接到了FPGA,如下图。

因此有两个关键点

- DDR3型号:IS43TR16256A-107MBLI

- DQ位宽:40

生成DDR interface IP

IP

在quartus IP catalog 中选择external memory interfaces intel cyclone 10 fpga IP

利用presets快速设置参数

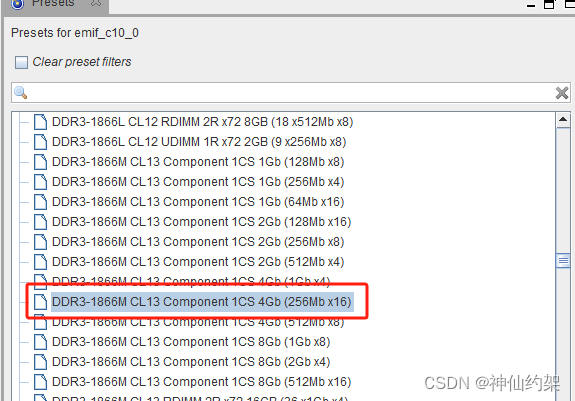

查看DDR3手册,确认ddr具体参数

选择库

107M对应DDR3-1866M CL13,因此可选择

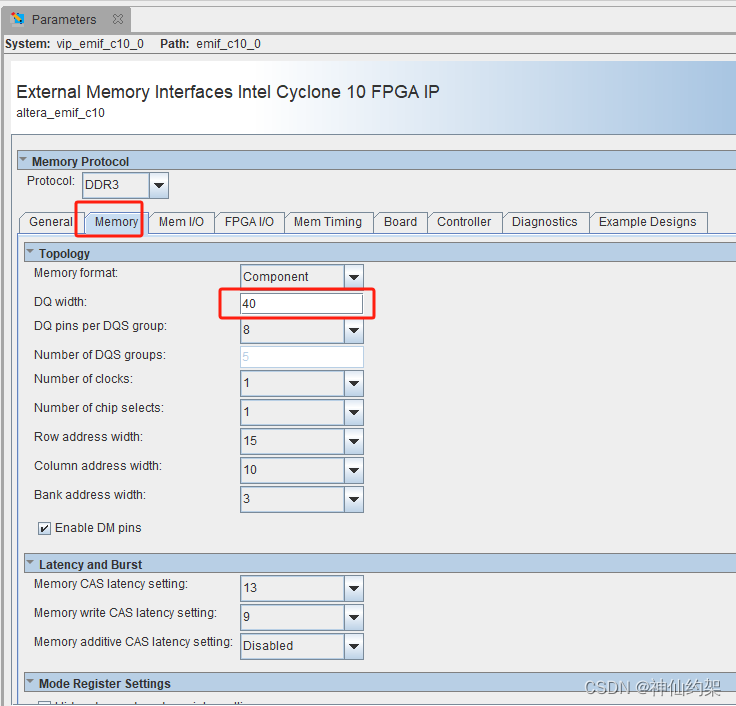

设置DQ为40bit

和官方使用一样的ddr,其他参数可以参考intel官方例程:

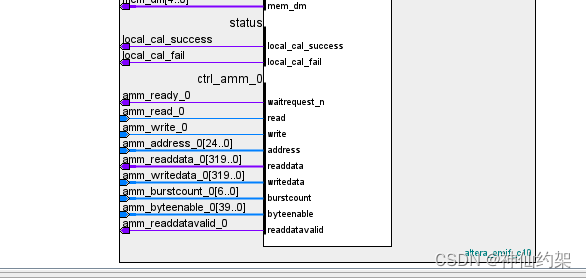

关于amm 部分avalon总线的数据位宽

使用上面的默认配置,avalon总线数据位宽为320.40bit*8。

对于 DDR3 UniPHY 控制器,Avalon数据总线的宽度取决于控制器Avalon-MM 接口设置的速率。选项为半速率或四分之一速率。半速率控制器的Avalon数据宽度是外部数据总线宽度的 4 倍。四分之一速率控制器的Avalon数据宽度是外部数据总线的 8 倍。

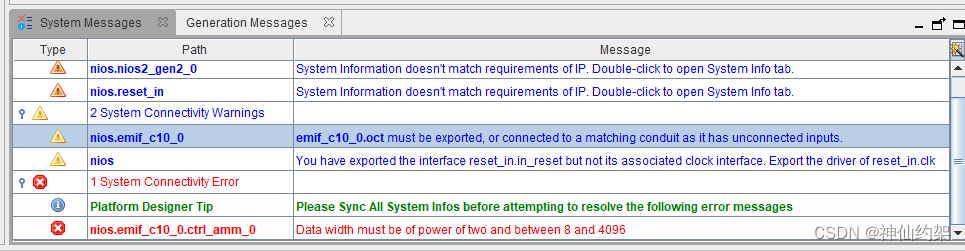

此时如果您还会使用platform qsys平台,可能会遇到下面的问题

Error: nios.emif_c10_0.ctrl_amm_0: Data width must be of power of two and between 8 and 4096

这里总线位宽需要是2的幂次方,64 128 256 512,但上面的配置为320,因此会出错。

需要把ddr interface ip amm接口数据位宽改为256.

在Controller下勾选Enable error detection and correction logic with ecc

这里为什么会出现启用ecc后位宽就变化了,我也找到了一个官方解释,没有深入了解

Avalon数据总线如何通过 ECC 接口映射到用于 DDR3 的外部 DDR3 总线?

启用 ECC 后,DDR3 UniPHY 控制器将在外部数据总线上为 ECC 代码词添加额外的 8 位。此 ECC 代码词占用外部数据总线中最重要的 8 位代码词。

例如,如果您使用 ECC 生成了 64 位 DDR3 四分之一速率控制器,则Avalon 数据总线为 512 位宽,外部数据总线为 72 位宽(64 位数据 8 位 ECC 代码词)。每个Avalon写突发 1 将导致外部数据总线的突发长度 8 (BL8) 传输。Avalon数据总线映射到外部数据总线,如下所示:

外部数据 0 [71:0] = {ECC 代码词 0[7:0],Avalon数据[63:0]}

外部数据 1 [71:0] = {ECC 代码词 1[7:0],Avalon数据[127:64]

外部数据 2 [71:0] = {ECC 代码词 2[7:0],Avalon数据[191:128]

外部数据 3 [71:0] = {ECC 代码词 3[7:0],Avalon数据[255:192]

外部数据 4 [71:0] = {ECC 代码词 4[7:0],Avalon数据[319:256]

外部数据 5 [71:0] = {ECC 代码词 5[7:0],Avalon数据[383:320]

外部数据 6 [71:0] = {ECC 代码词 6[7:0],Avalon数据[447:384]

外部数据 7 [71:0] = {ECC 代码词 7[7:0],Avalon数据[511:448]

这里位宽没有一个直接的更改位置,起码我没有找到,如果您有方法请一定留言教我一下~谢谢

如果这篇文章帮到了您,烦请点个关注,后续会发布更多fpga相关文章。

2013

2013

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?