学习更多相关知识,关注博主知乎账号,用户名Trustintruth https://www.zhihu.com/people/suo-yi-xin-90/activities

首先几个问题是我们在一开始就要牢牢记住的。

1.chisel是寄宿在Scala里的语言,本质是Scala,所以scala的语法在chisel中也可以用,比如Scala的基本值等

2.由于在Verilog中存在不可综合的语法,所以在chisel经过Firrtl文件生成类似于Verilog的中间文件,再转化为Verilog是最终生成的Verilog,只会采用最基础的可综合的语法。所以不必担心Chisel写出的数据是不可综合的。

3.Chisel不能支持四态逻辑中的Z和X,只支持0和1,且会对未被驱动的输出型端口和网线进行检测,如果存在就会报错

4.Chisel的代码包并不会像Scala的标准库那样被编译器隐式导入,所以每个Chisel文件都应该在开头至少写一句“import chisel3._”。这个包包含了基本的语法,对于某些高级语法,则可能需要“import chisel3.util._”、“import chisel3.experimental._”、 “import chisel3.testers._”等等。

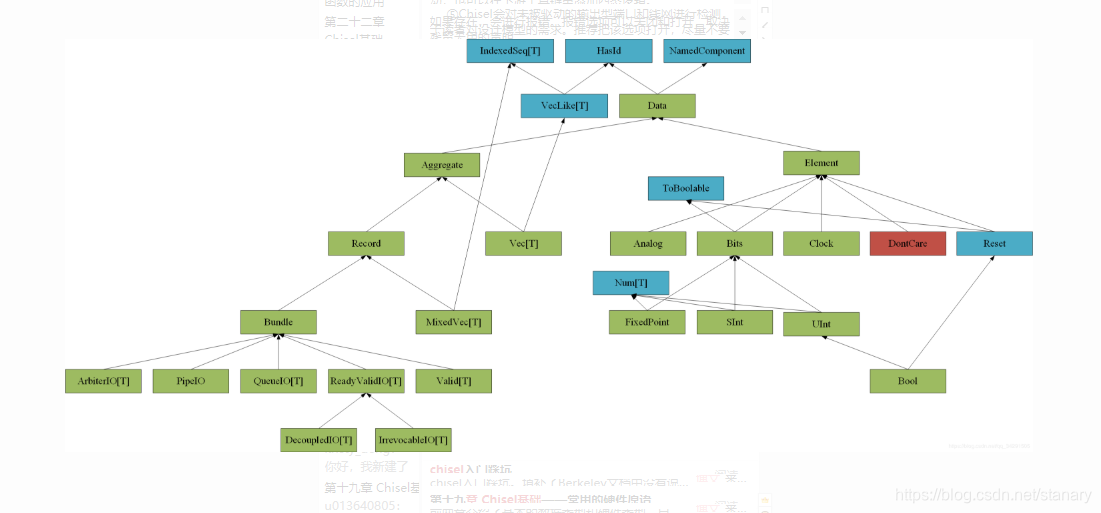

chisel的数据类型

绿色为class,红色为object,蓝色为trait,箭头为超类

1668

1668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?