cs stage 负载电阻必须足够大才能获得高增益(否则和输出电阻并再乘gm 增益会很小)

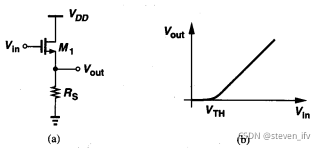

source follower as a voltage buffer(可以理解为阻抗变换器)

最好做到输入电阻∞ 输出电阻为0 增益可以为1 接在cs stage后面 实现阻抗变换

input 在G output在S 也可以成为common drain stage(仅有截止和饱和两种状态)

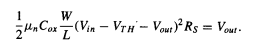

小信号分析

![]()

![]() A<1

A<1

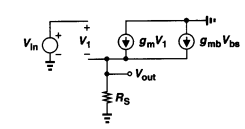

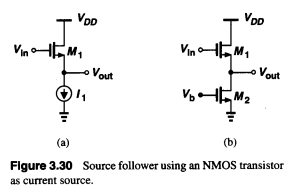

Id严重依赖Vin 仍然非线性 解决方法就是使用电流源代替电阻(即增加nmos长L电流源)

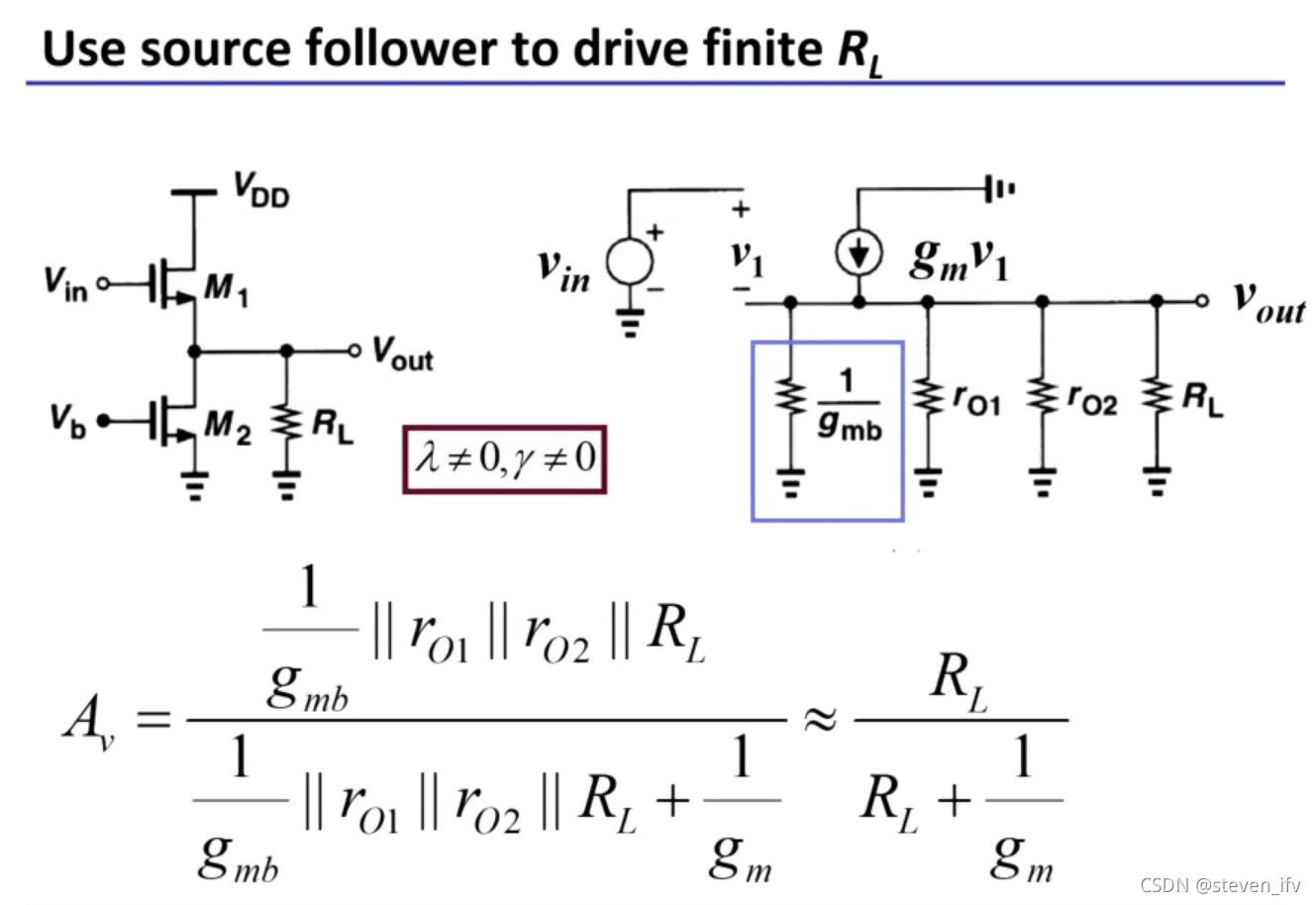

电流源可以视为Rs趋于∞ Av![]() 此时受M1体效应的影响

此时受M1体效应的影响

推导输出电阻

小信号模型中 电流源等效无穷大电阻(开路) 常用一个Vx代替来进行分析 (b接地)

同时希望输入mos管的跨导尽可能大 即W大 L小 宽长比大就会有很大的跨导 输出电阻就会小

源随器的常见应用

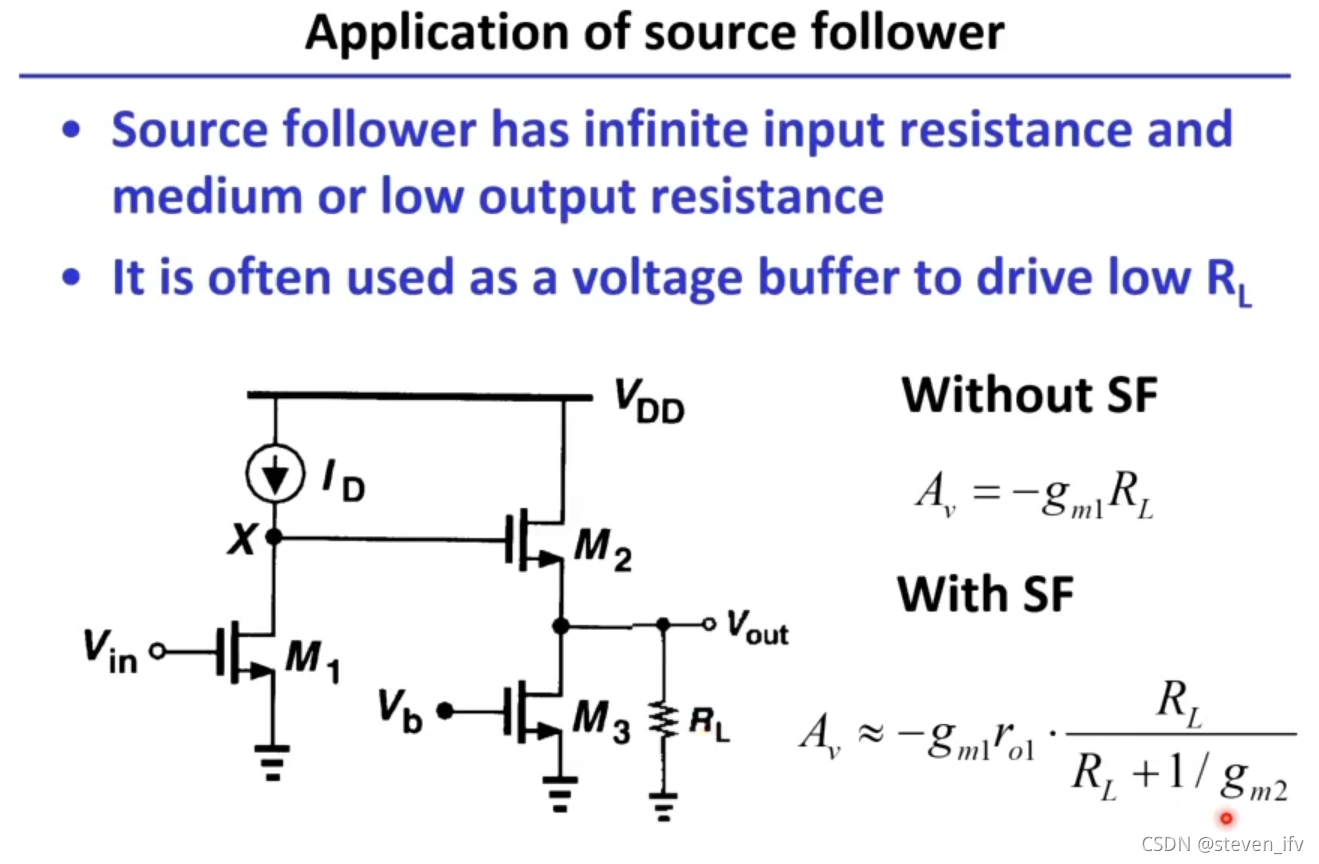

直接用CS很难推动小电阻的负载,因此增加源随器进行阻抗变换可以得到较大的增益

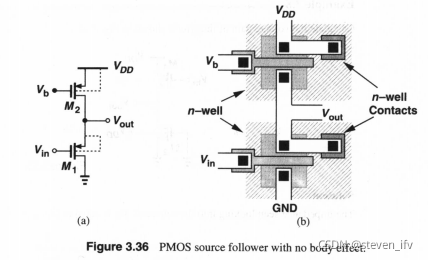

通过将n阱与源端连接可以消除体效应

level shifer(电平移位器)

如果输入信号时麦克风这样的中心电平为0的信号,可以将其与源随器连接(抬升电压用P 降低n)

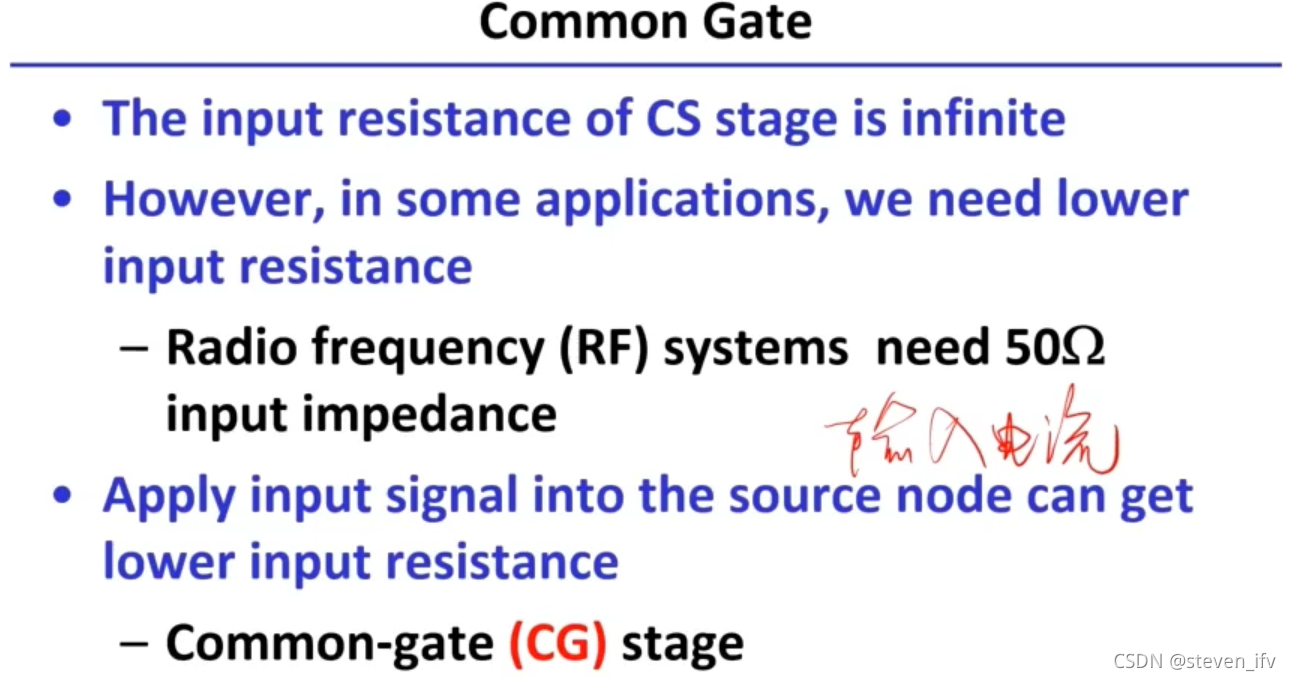

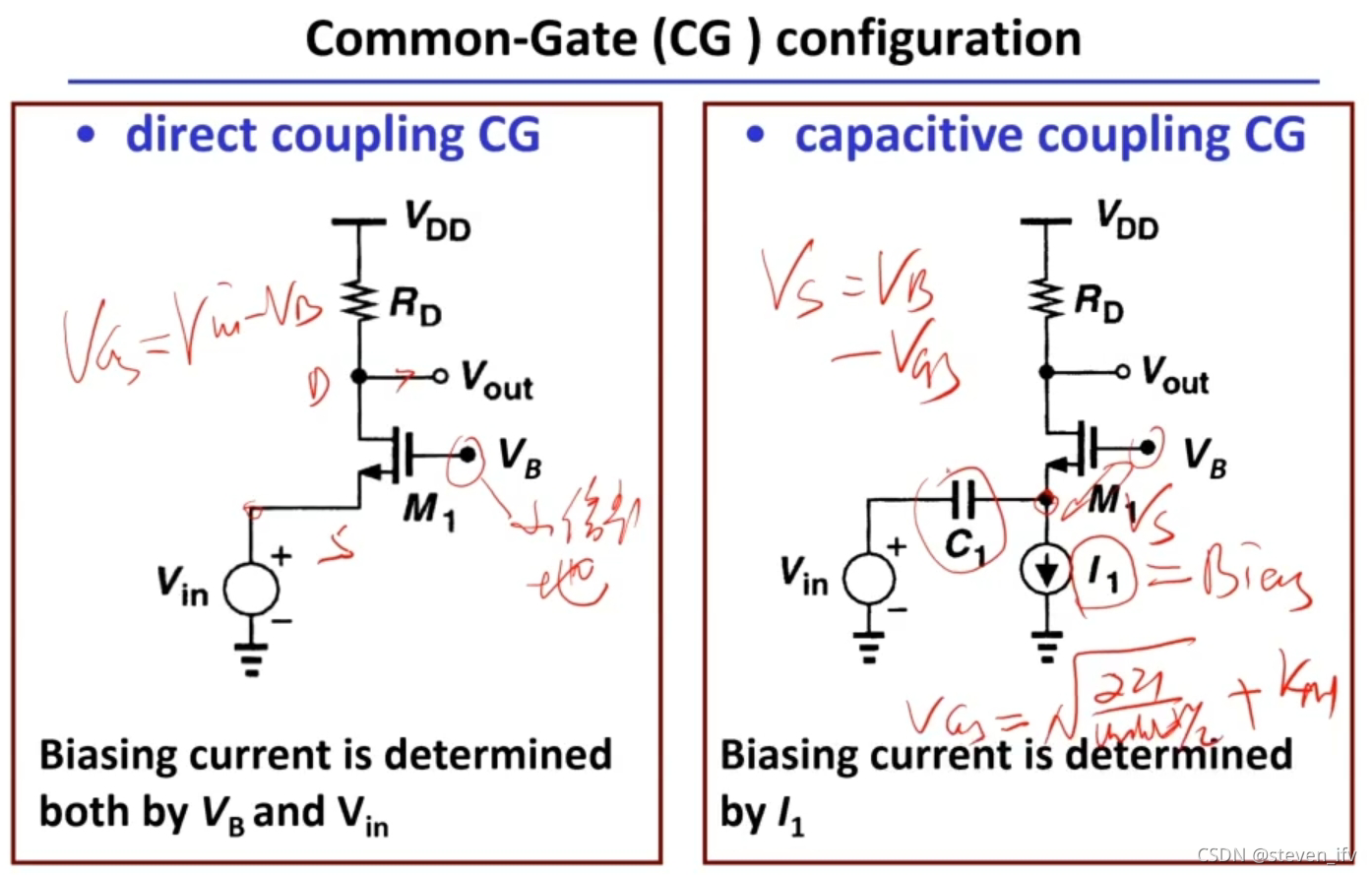

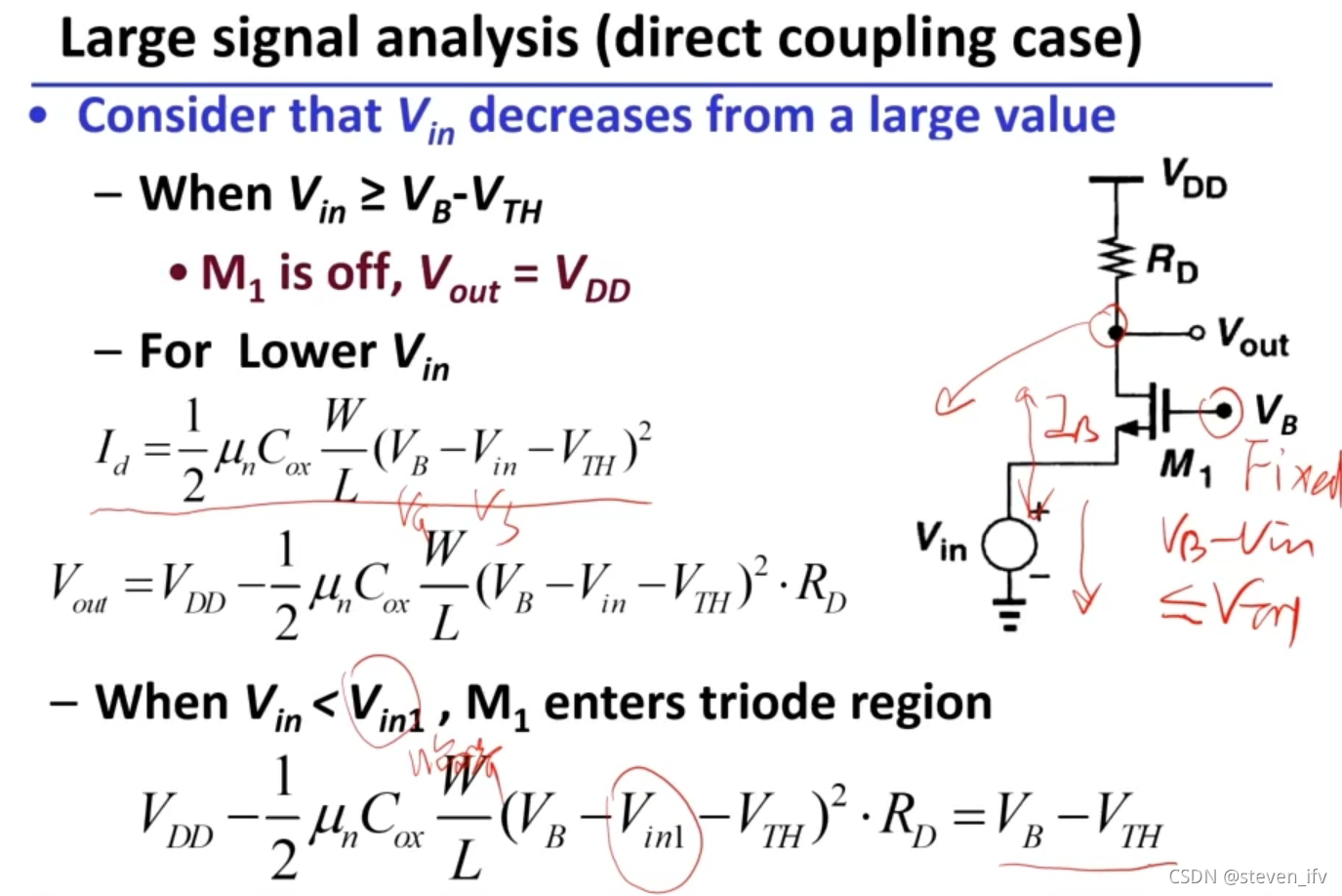

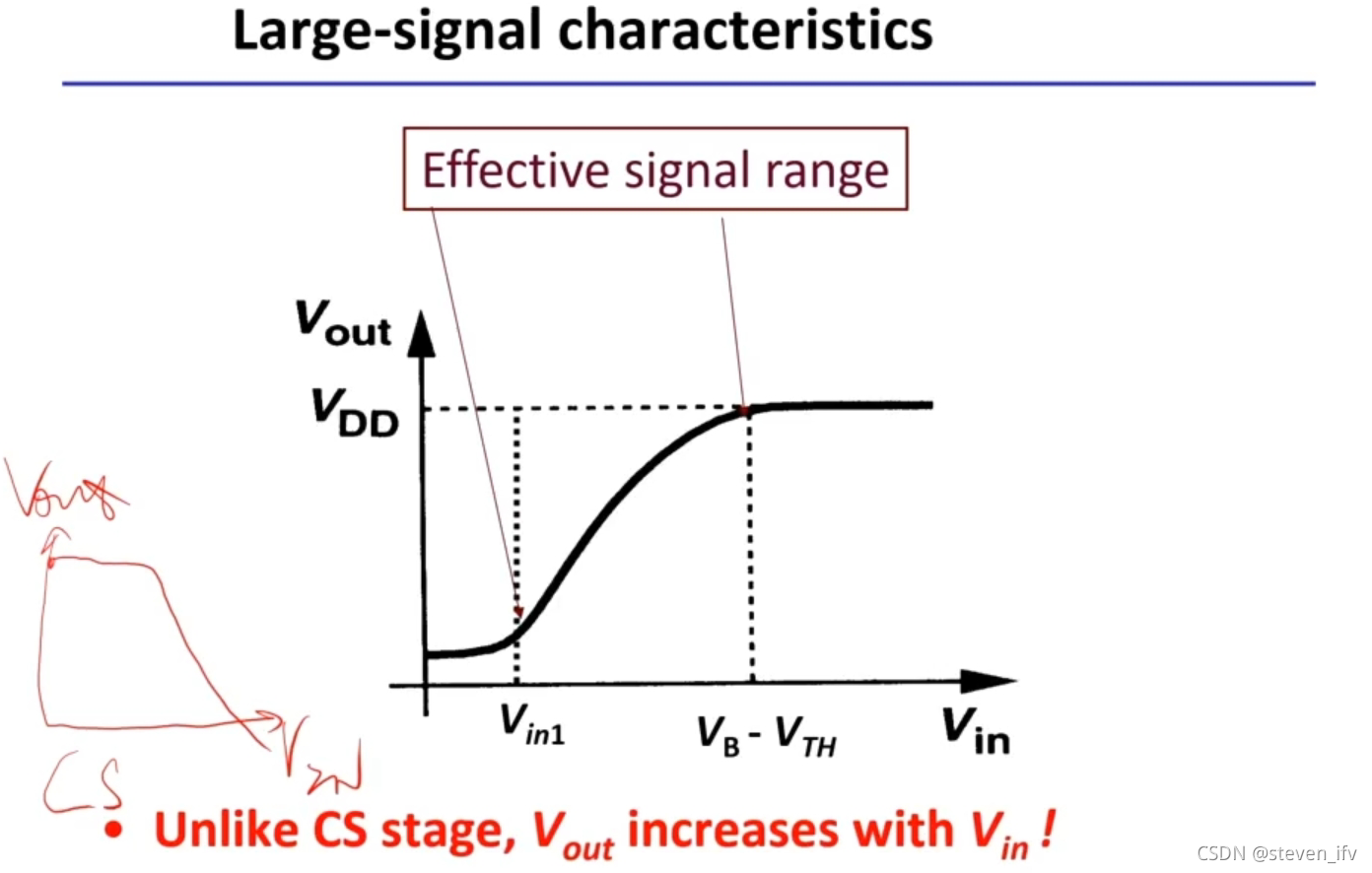

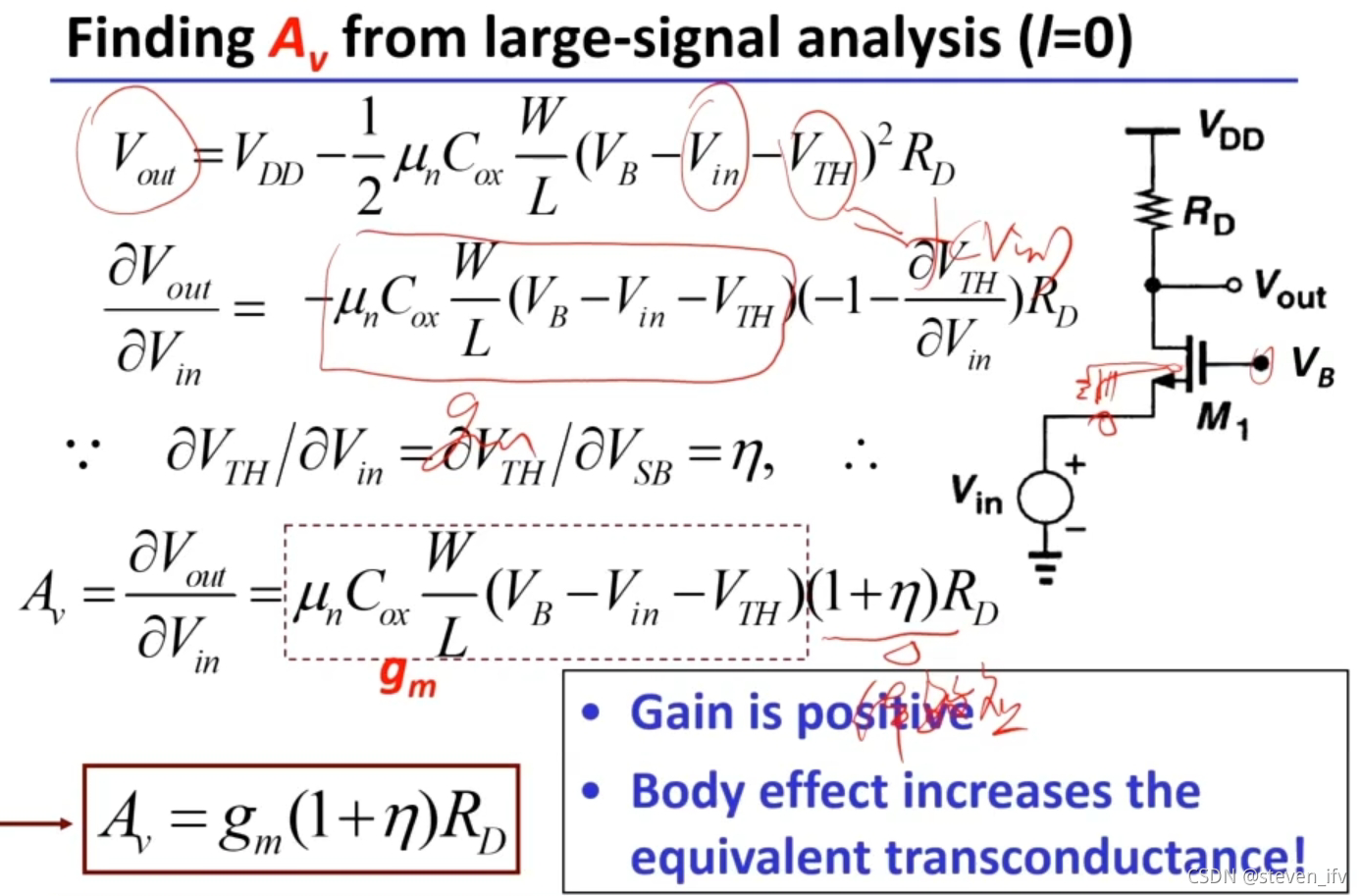

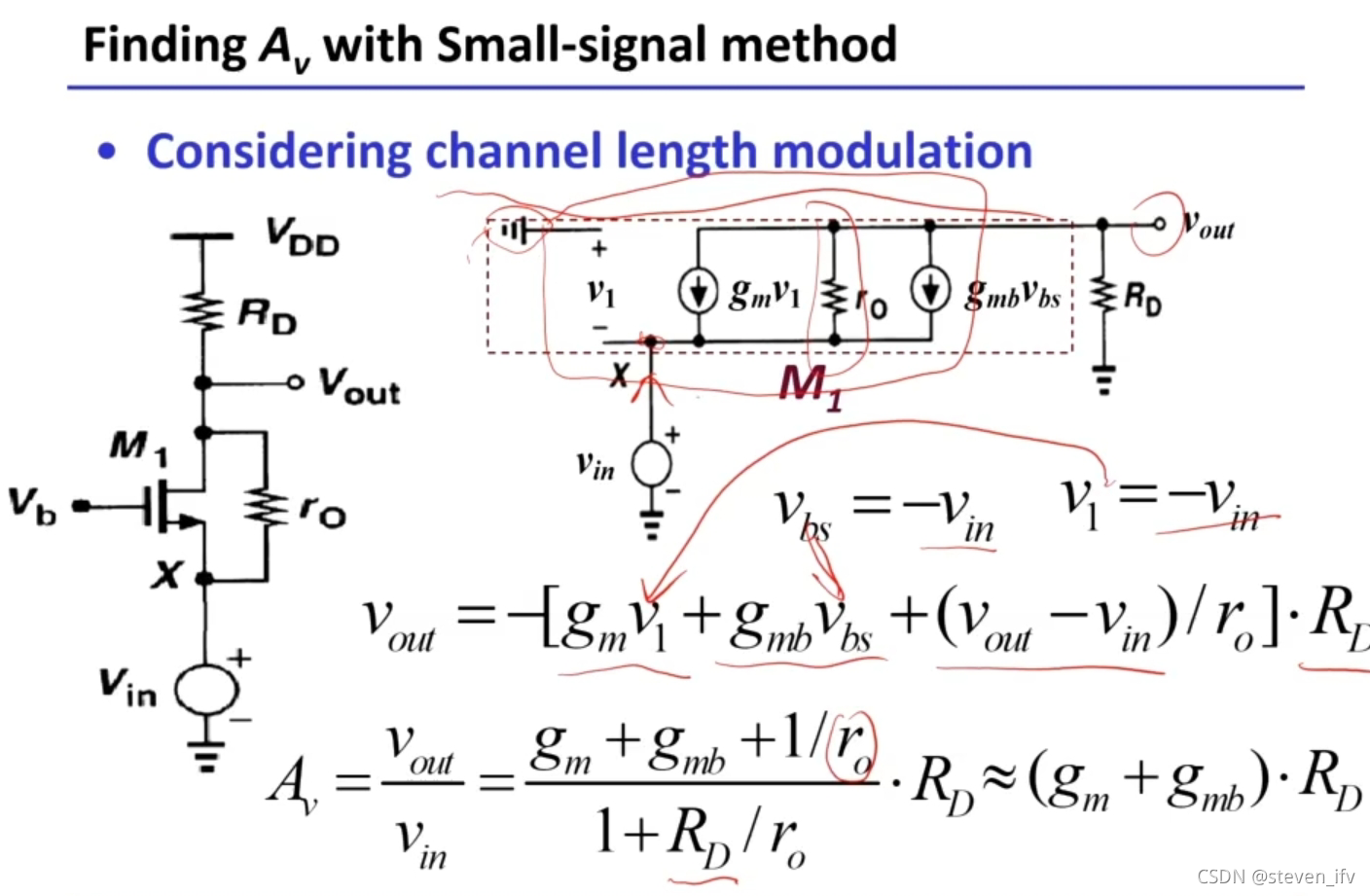

common gate(共栅放大器)指栅极接小信号的地 并不是真正接地

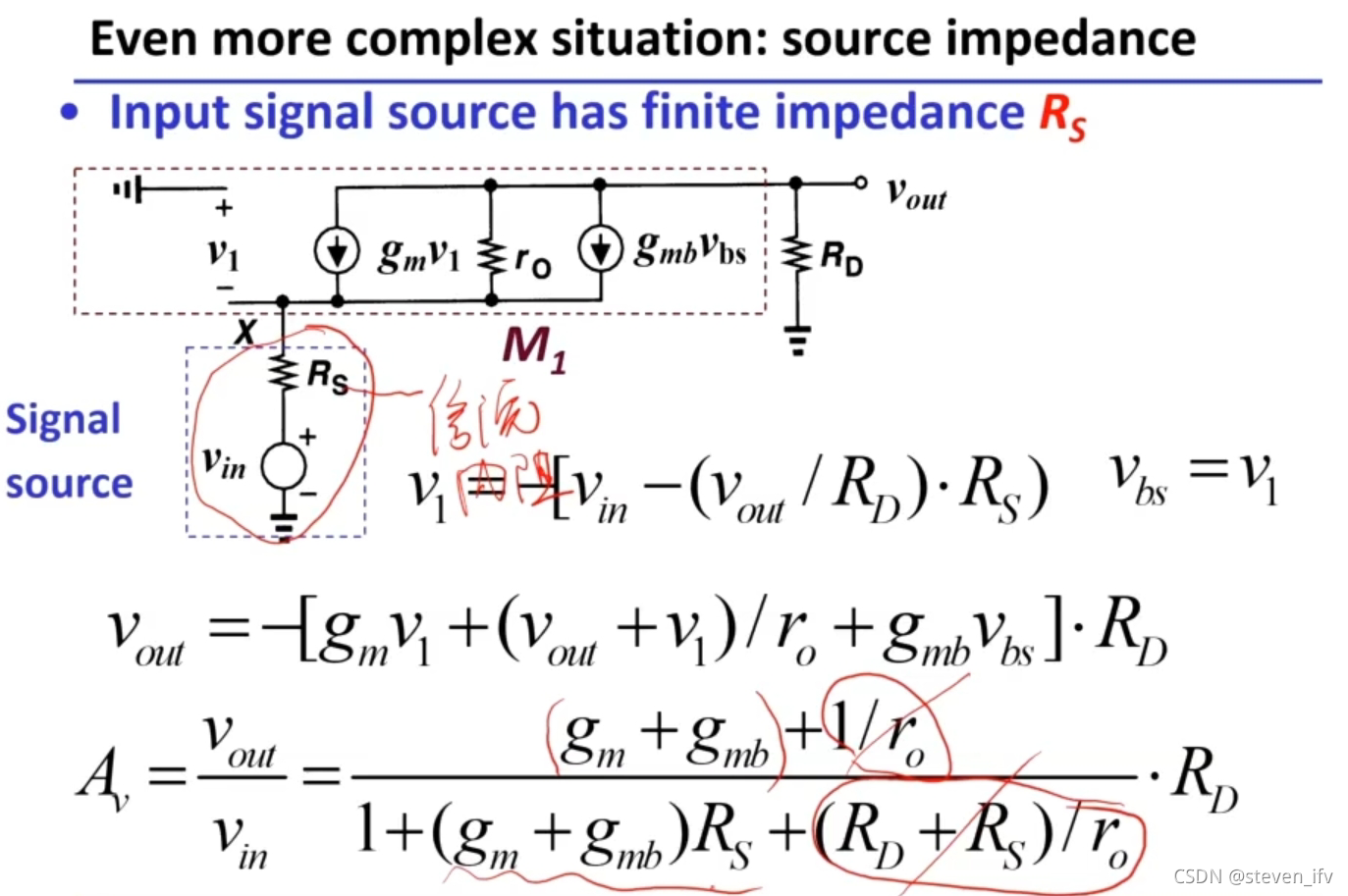

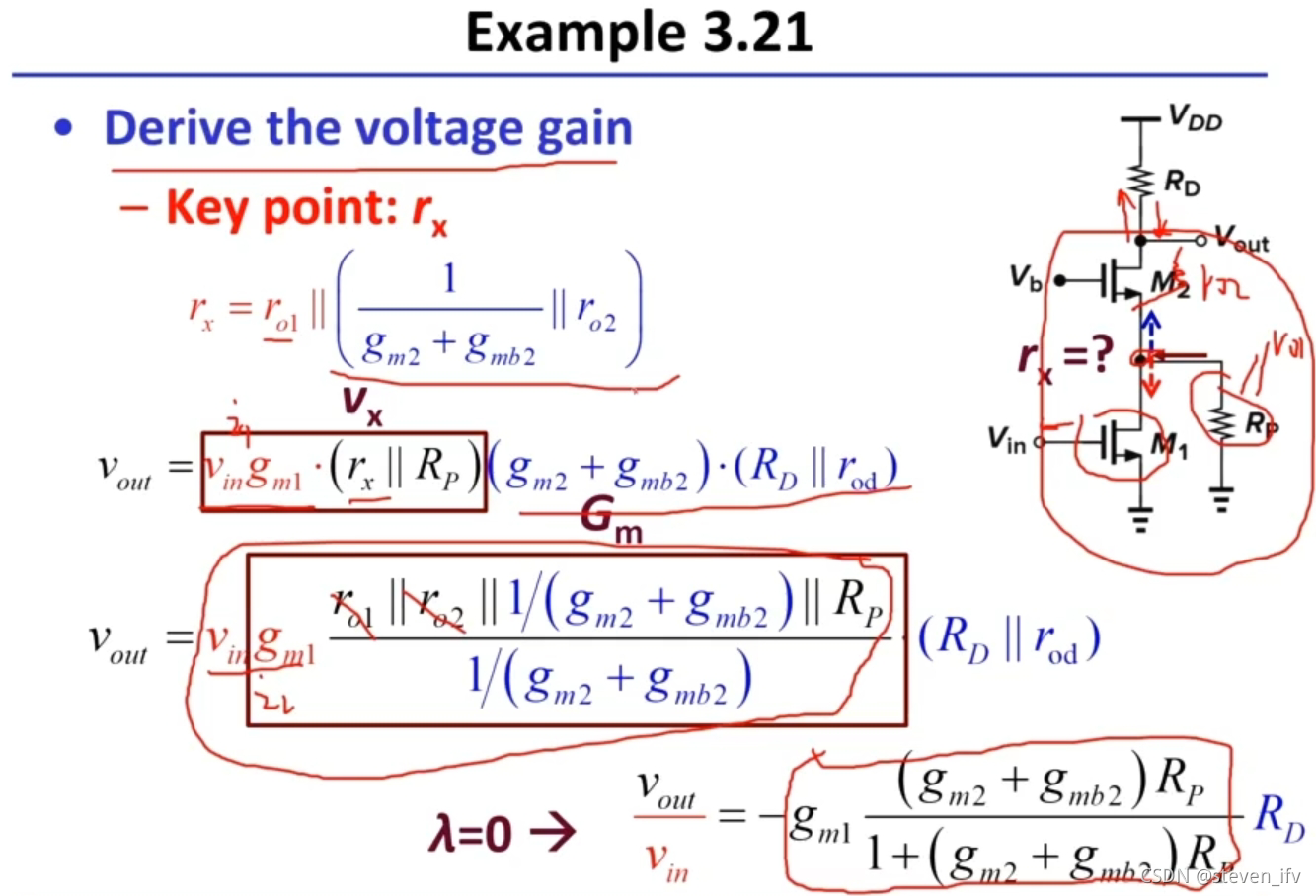

输入信号源的内阻会影响增益

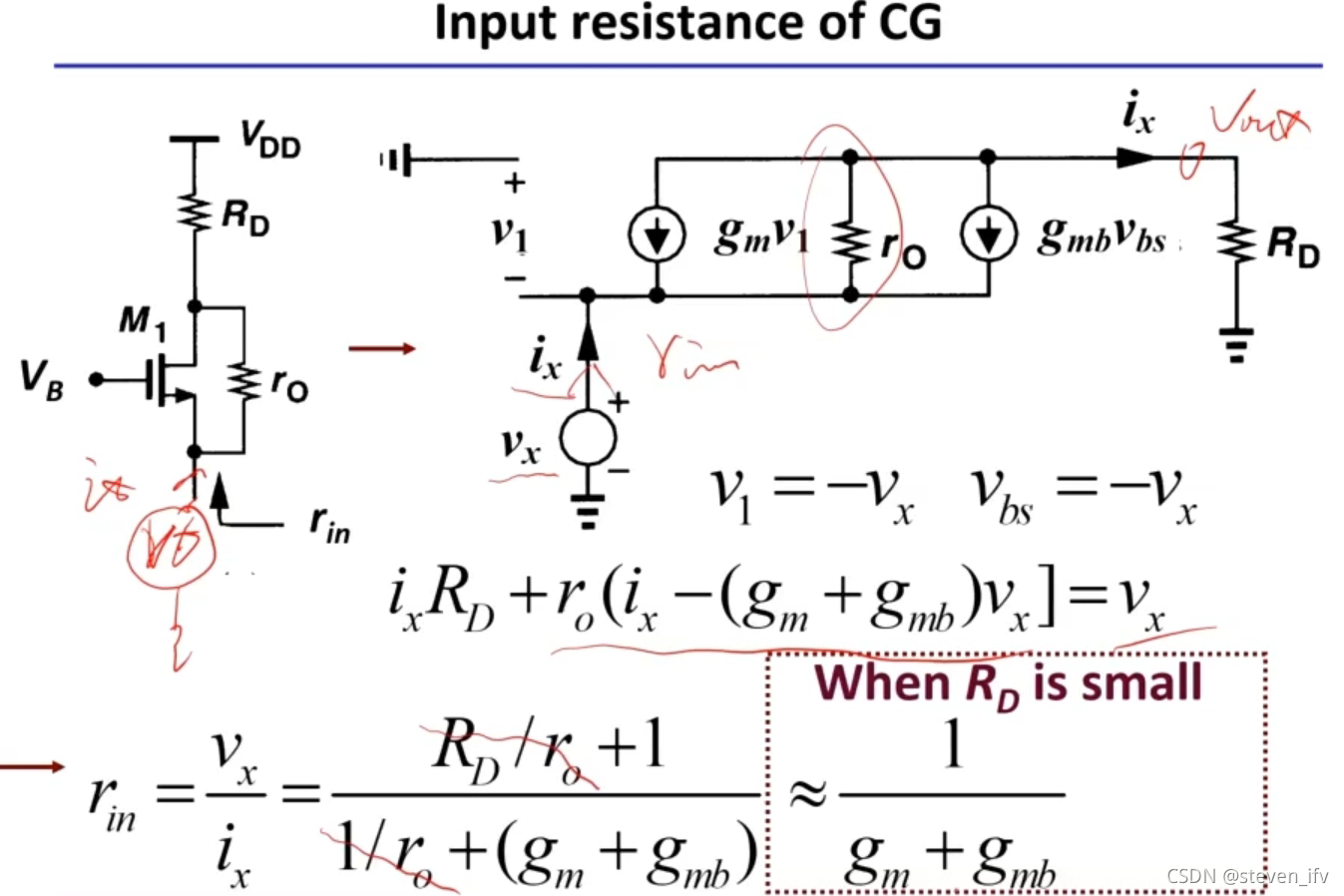

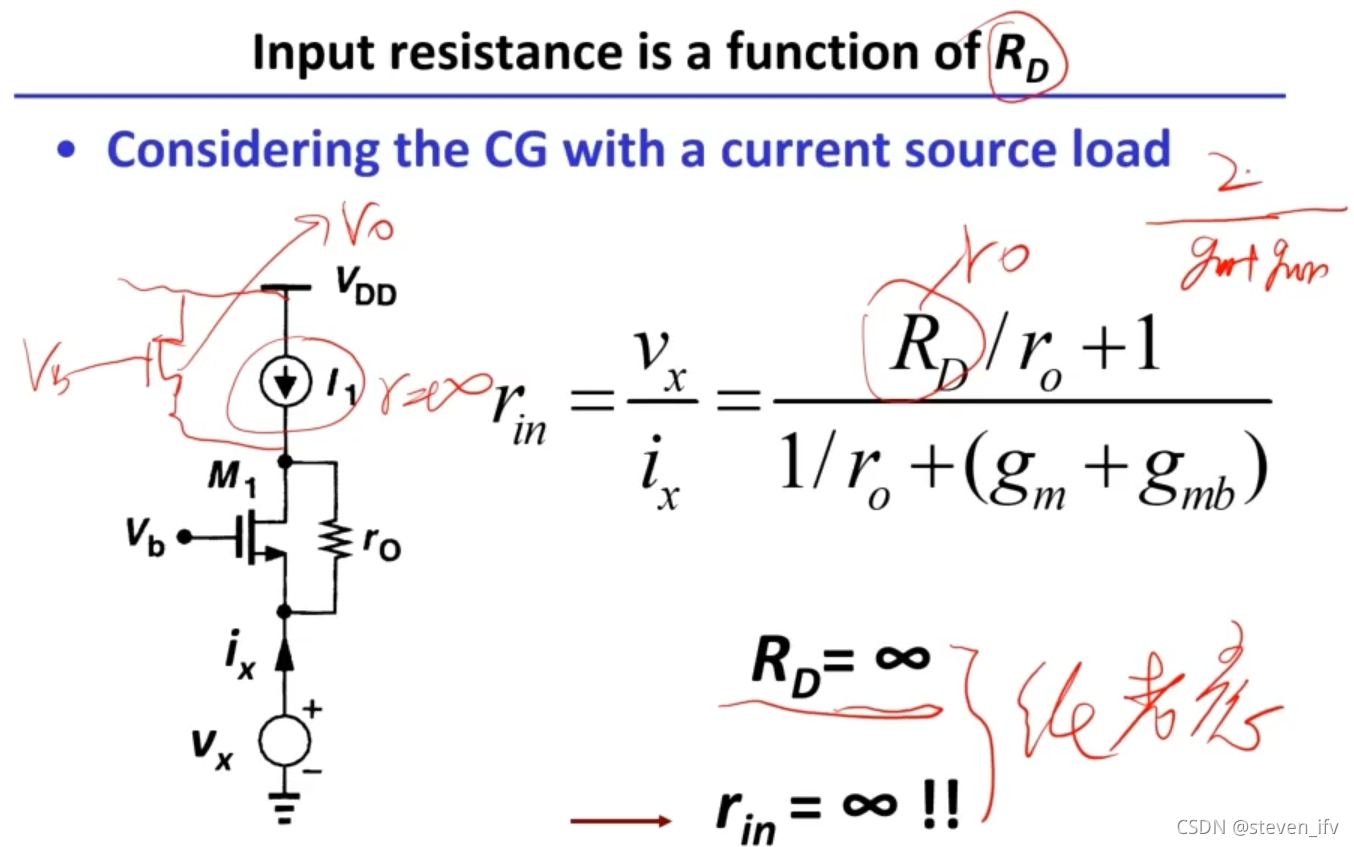

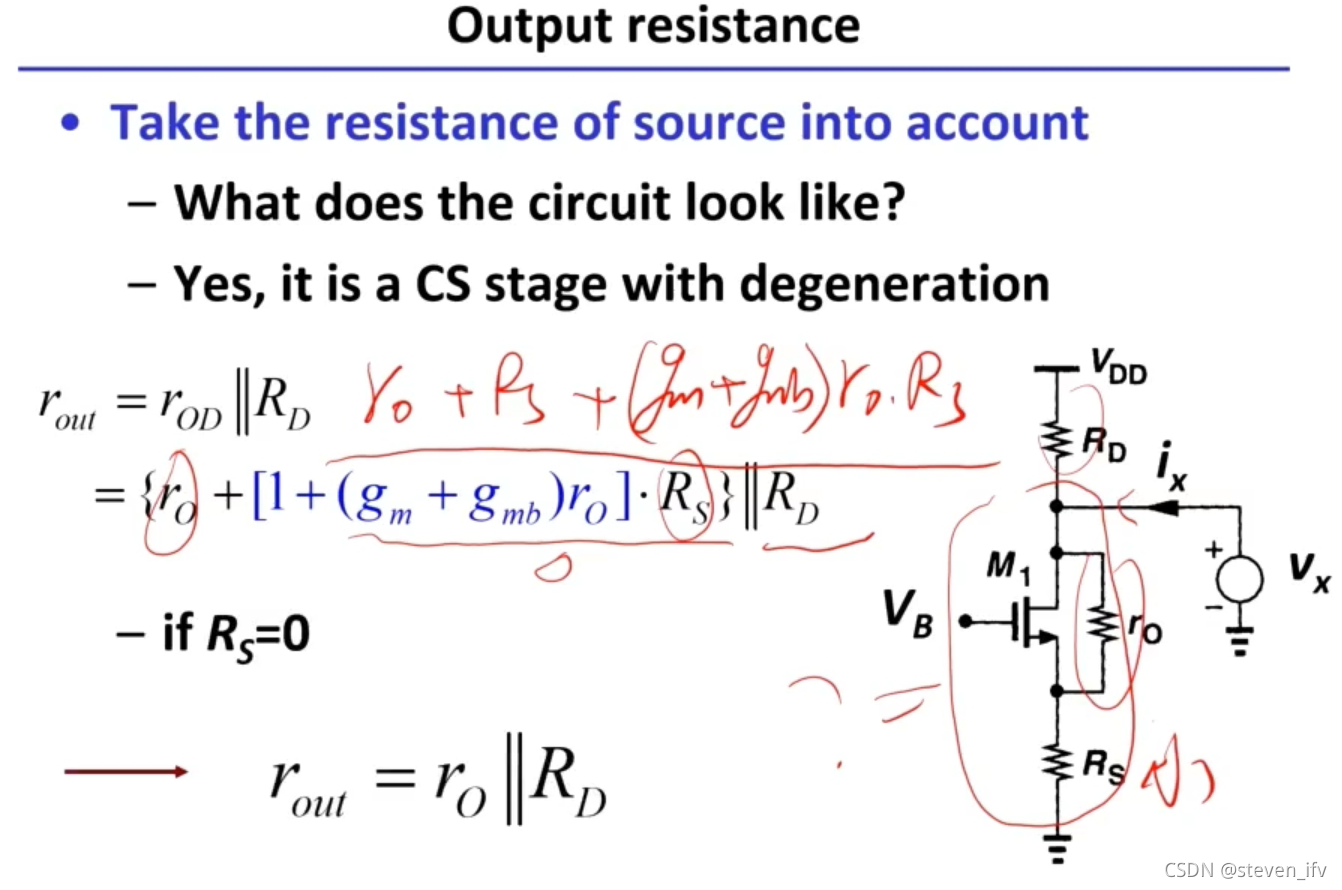

共栅级输入电阻的推导

即使用最接近电流源的pmos代替理想电流源 也仅仅变为2/gm rin仍然很小

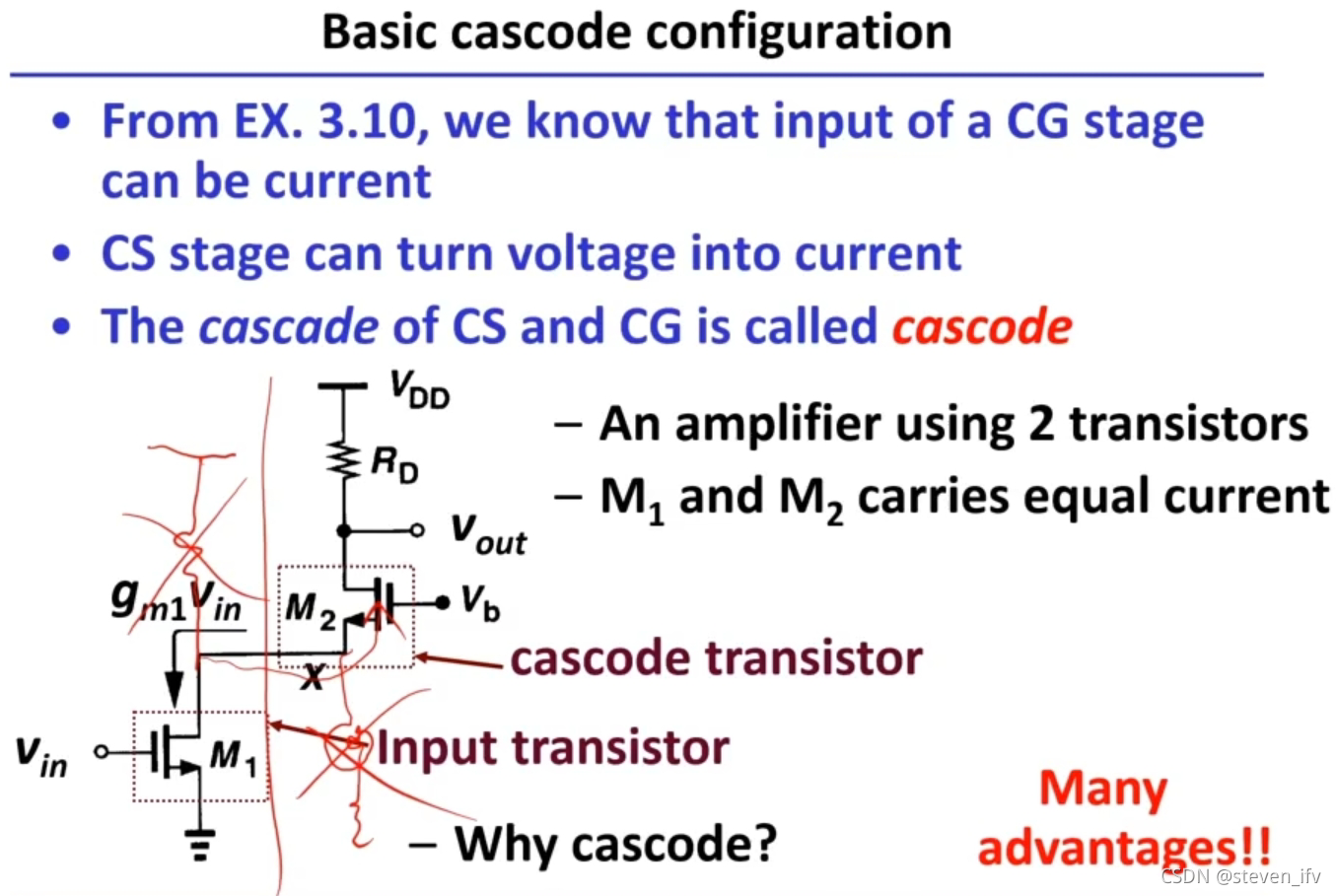

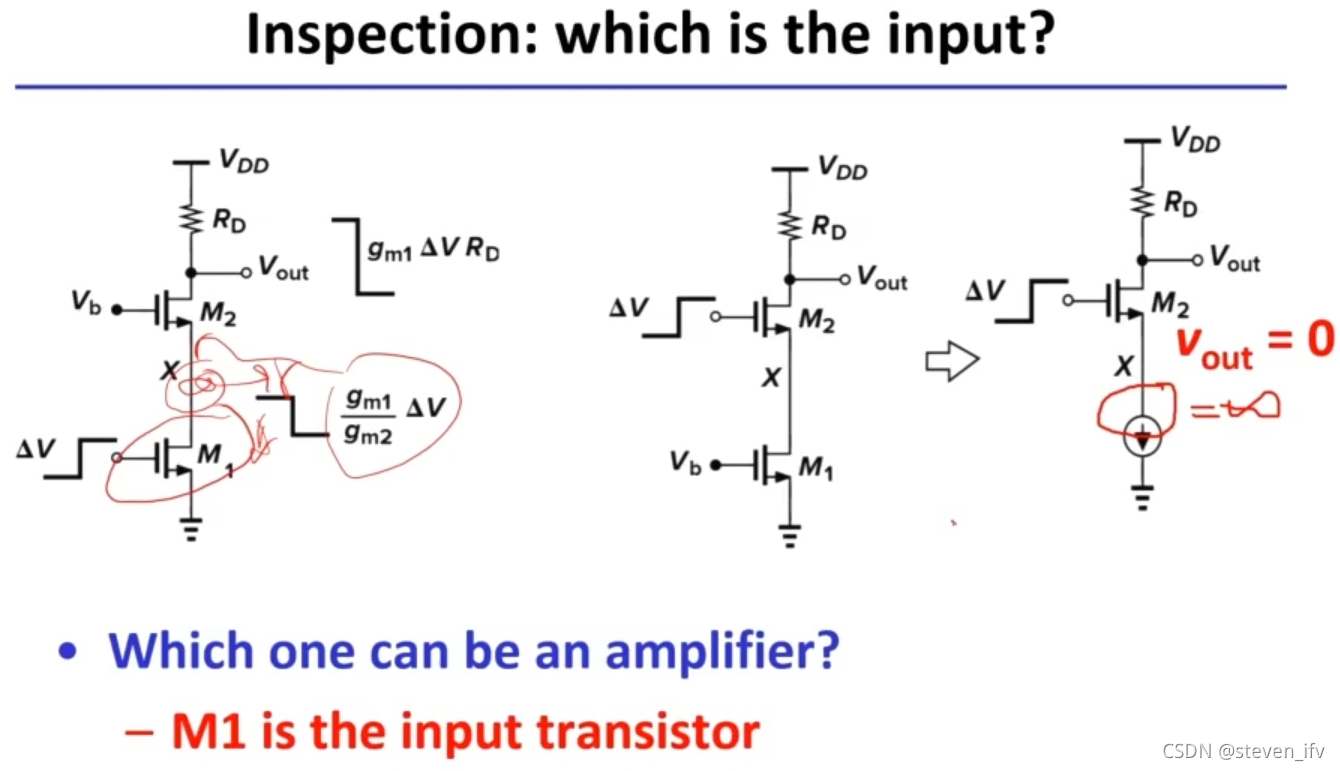

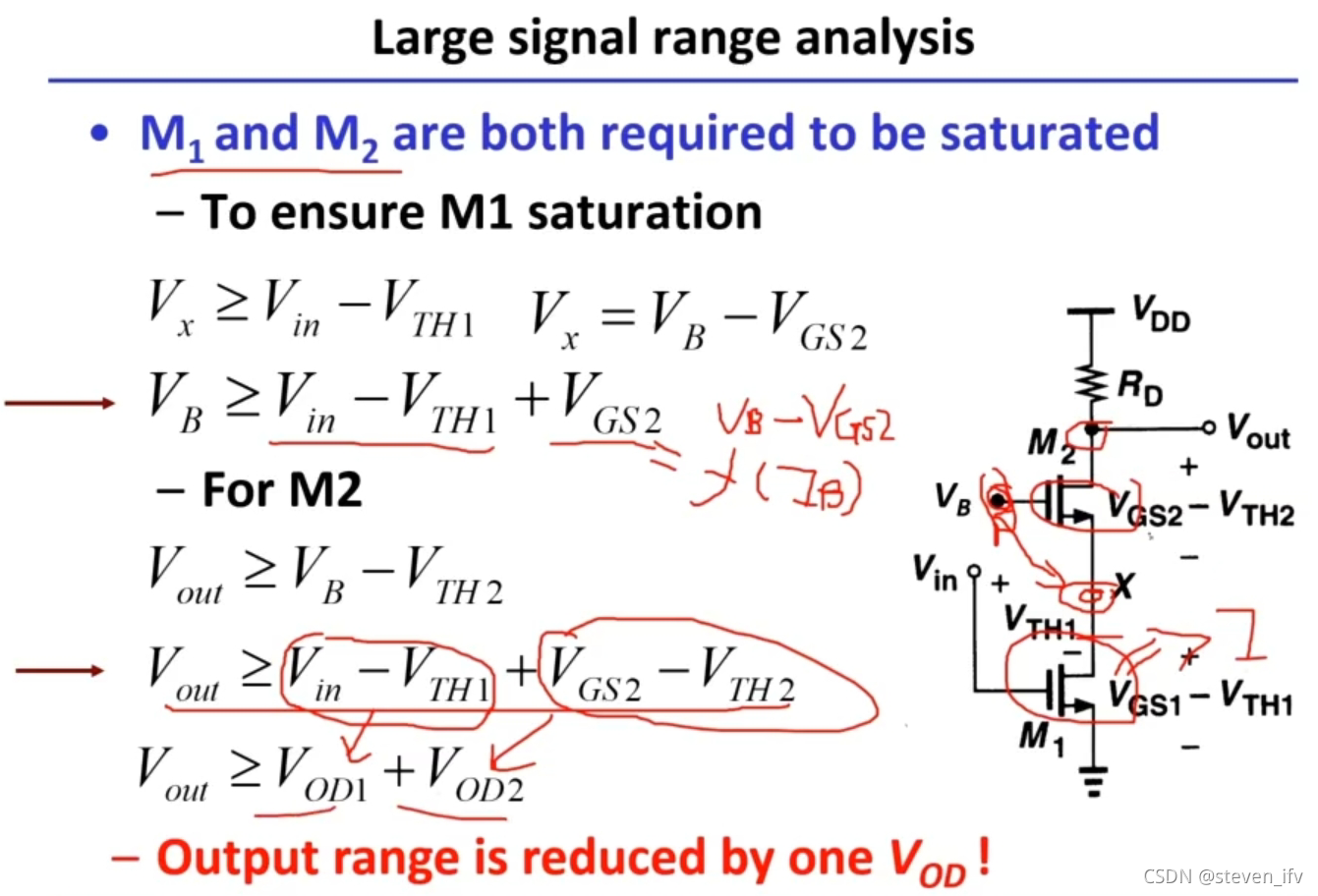

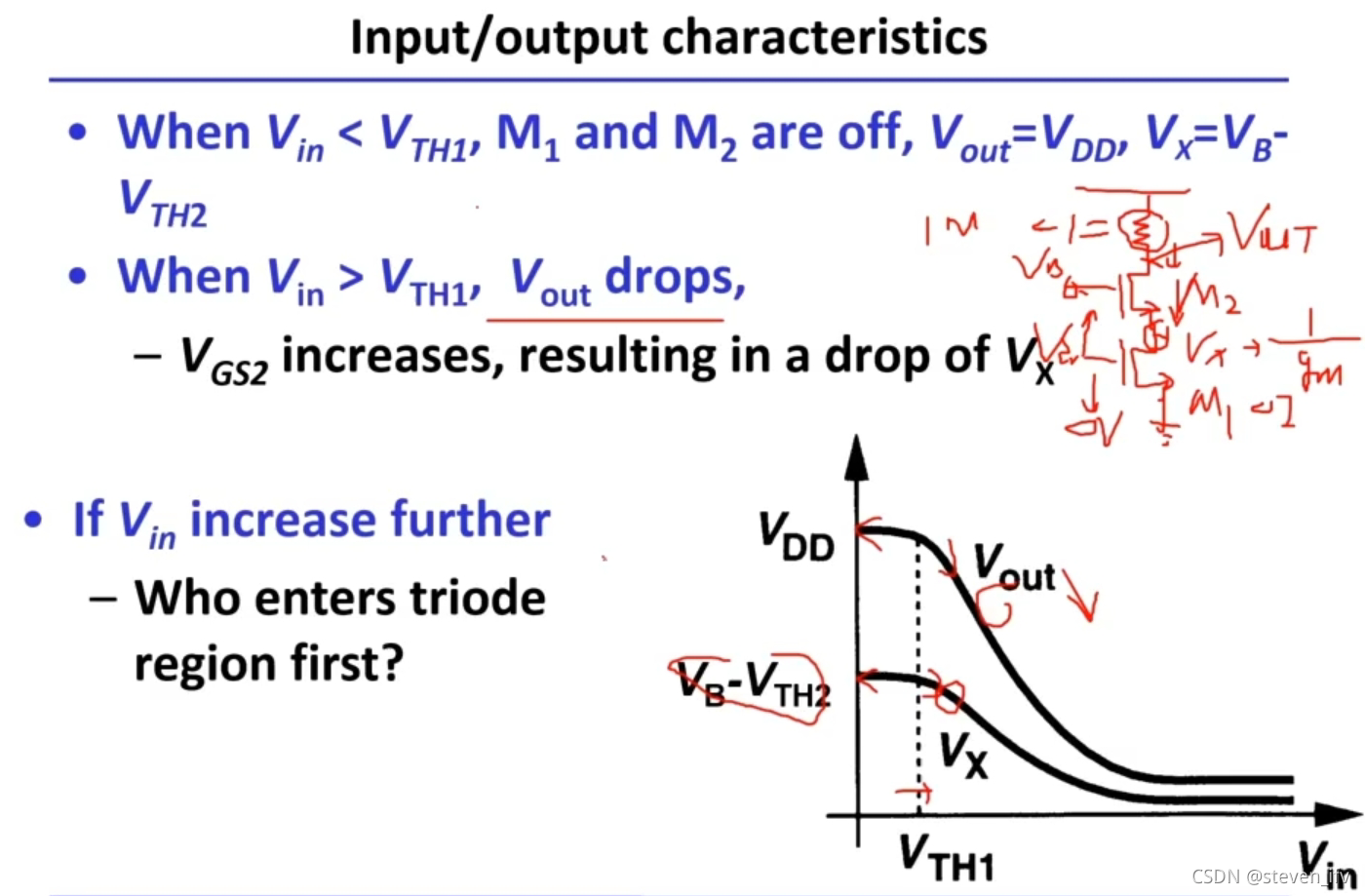

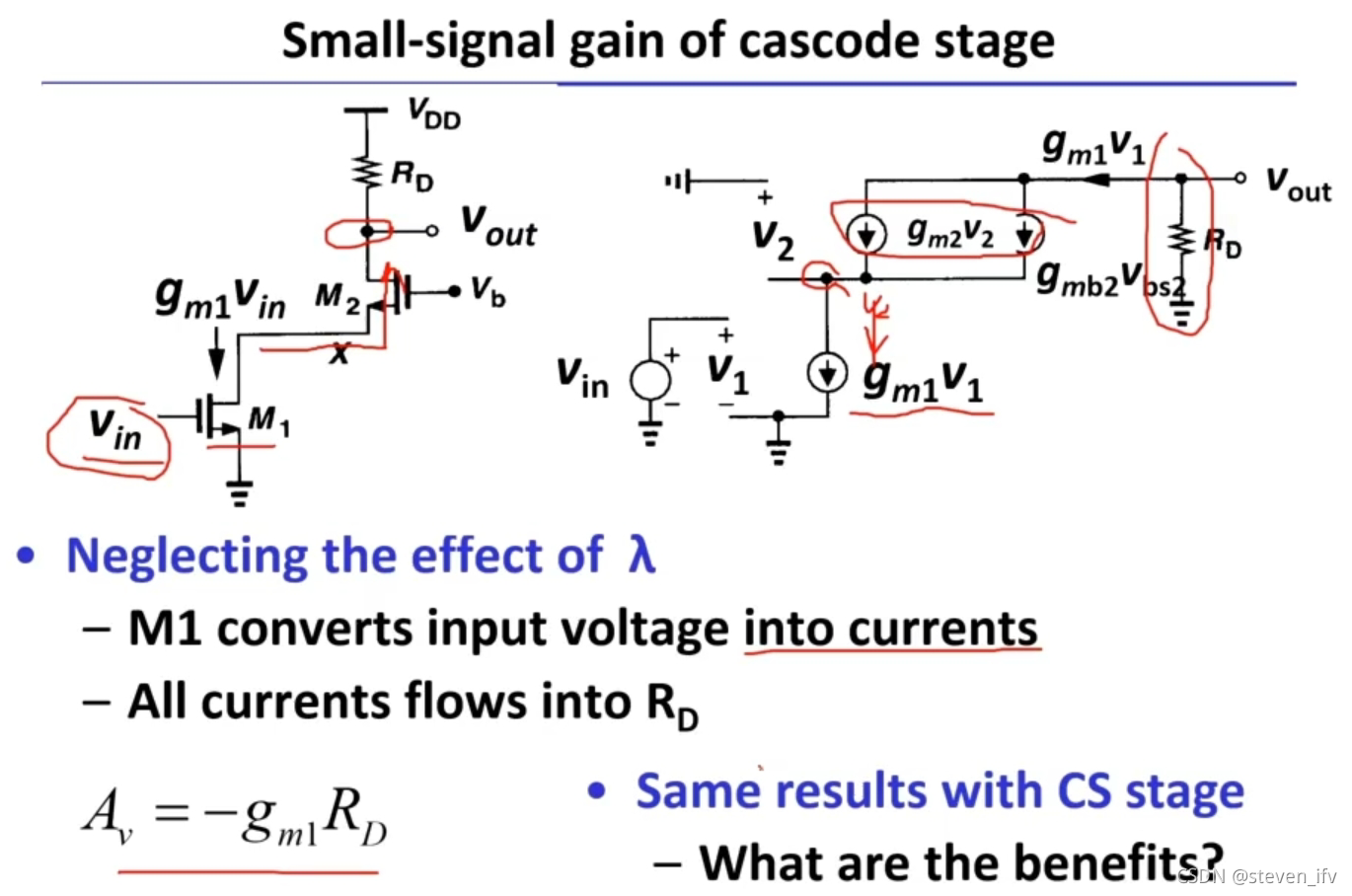

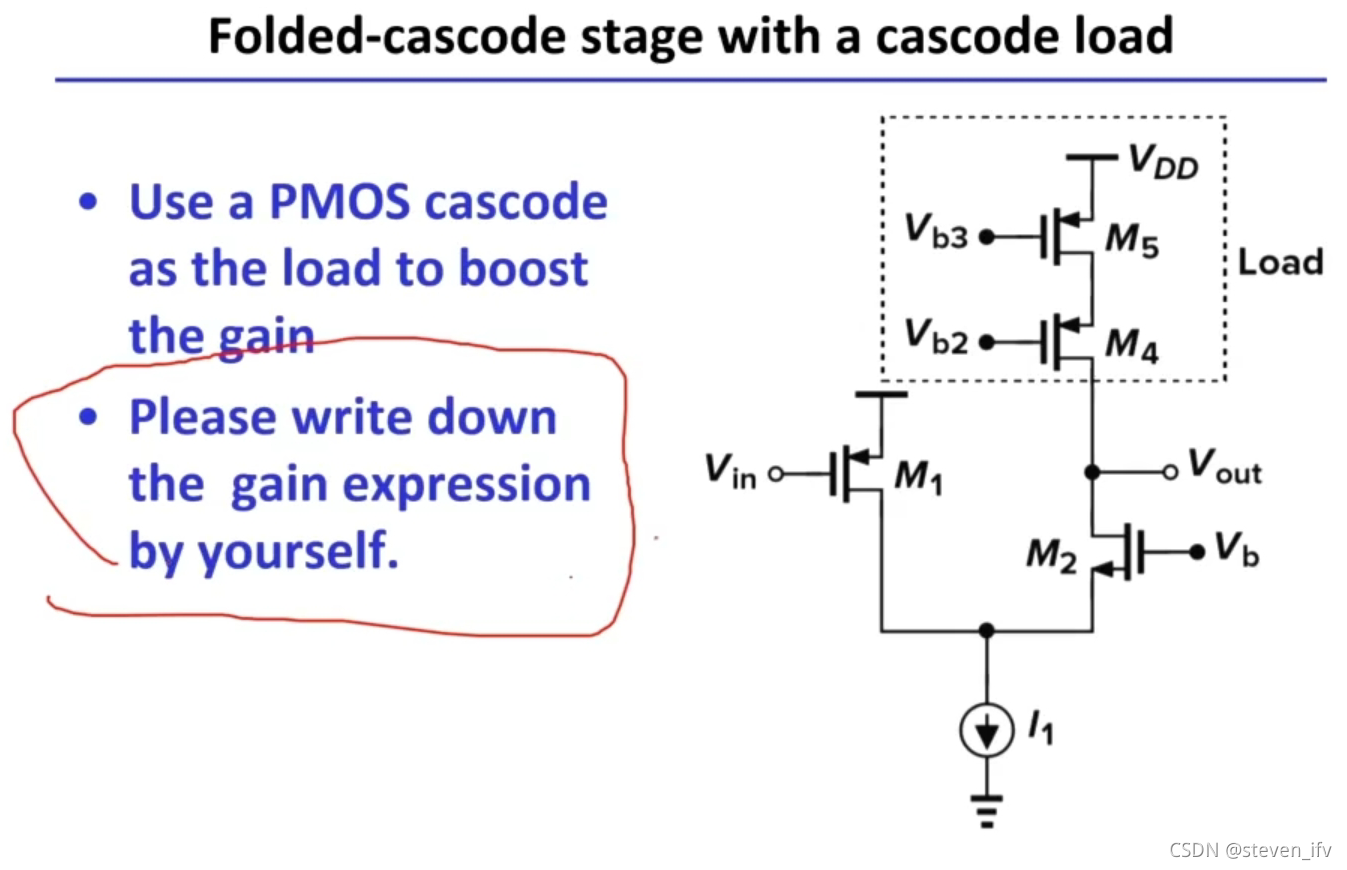

cascode stage(共源共栅) 将输入共源极得到的输出电流直接流进共栅极的输入端就称为cascode 流过相等的电流 电流复用

如果输入选错晶体管就会输出为0

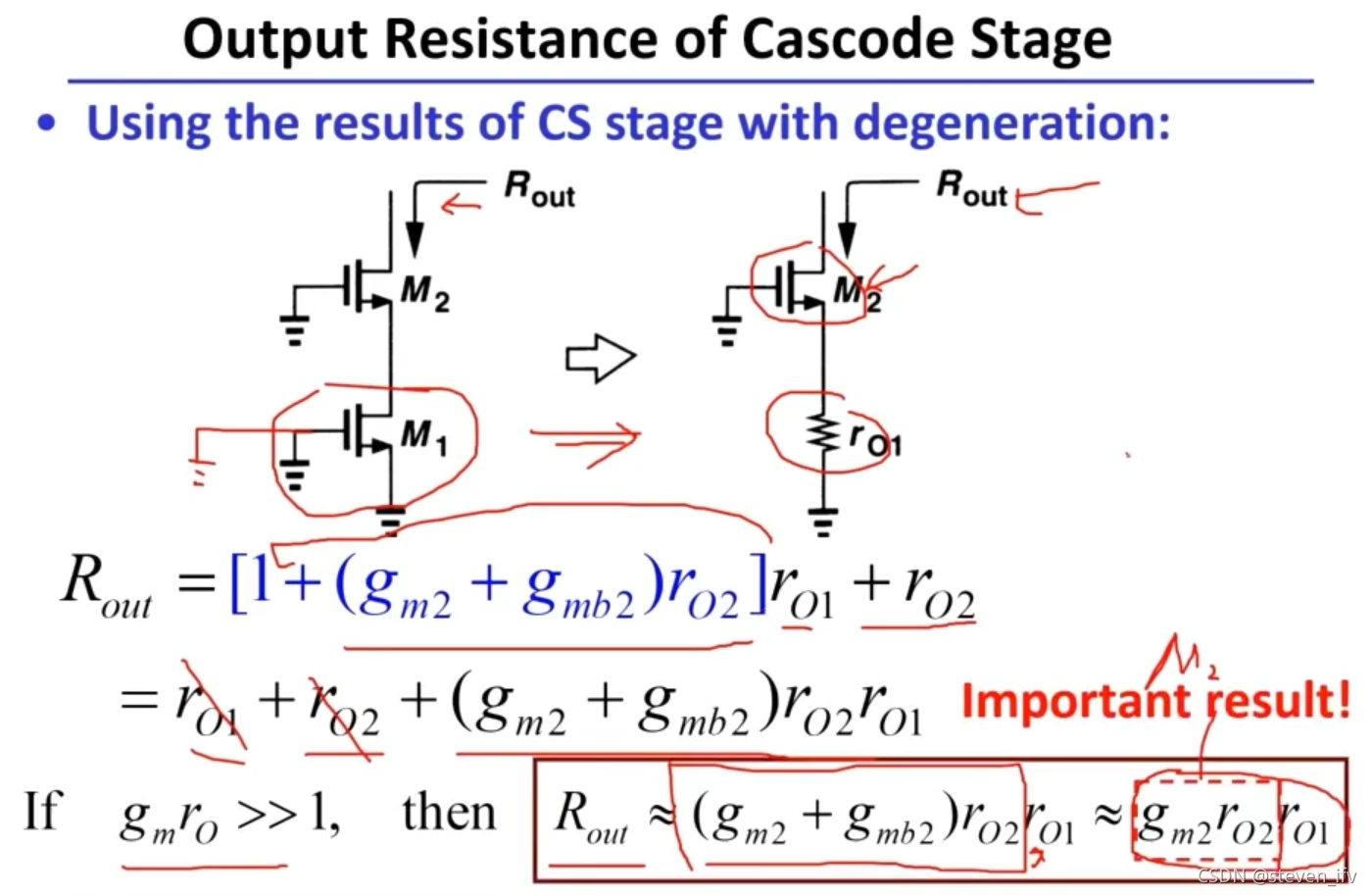

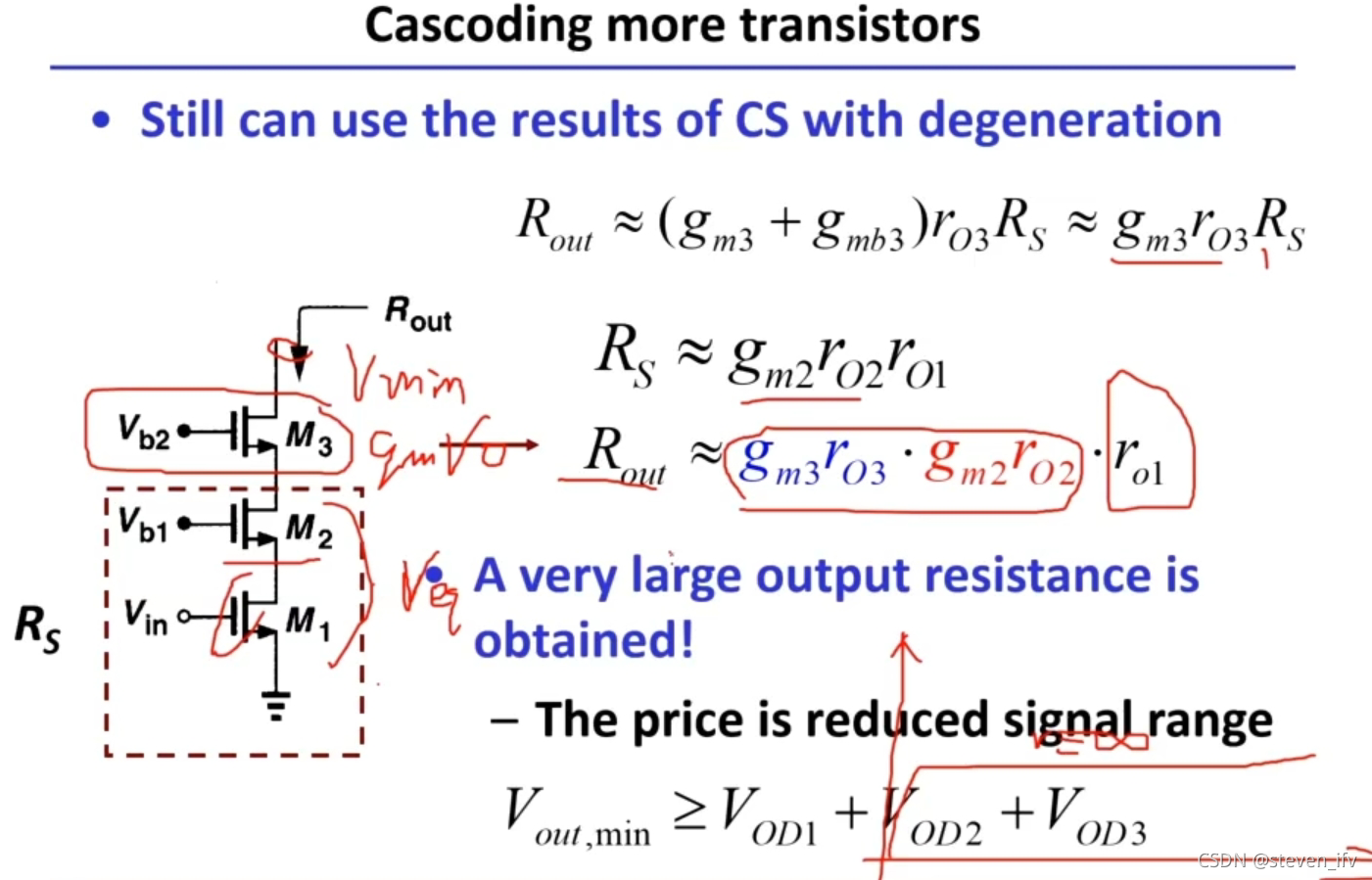

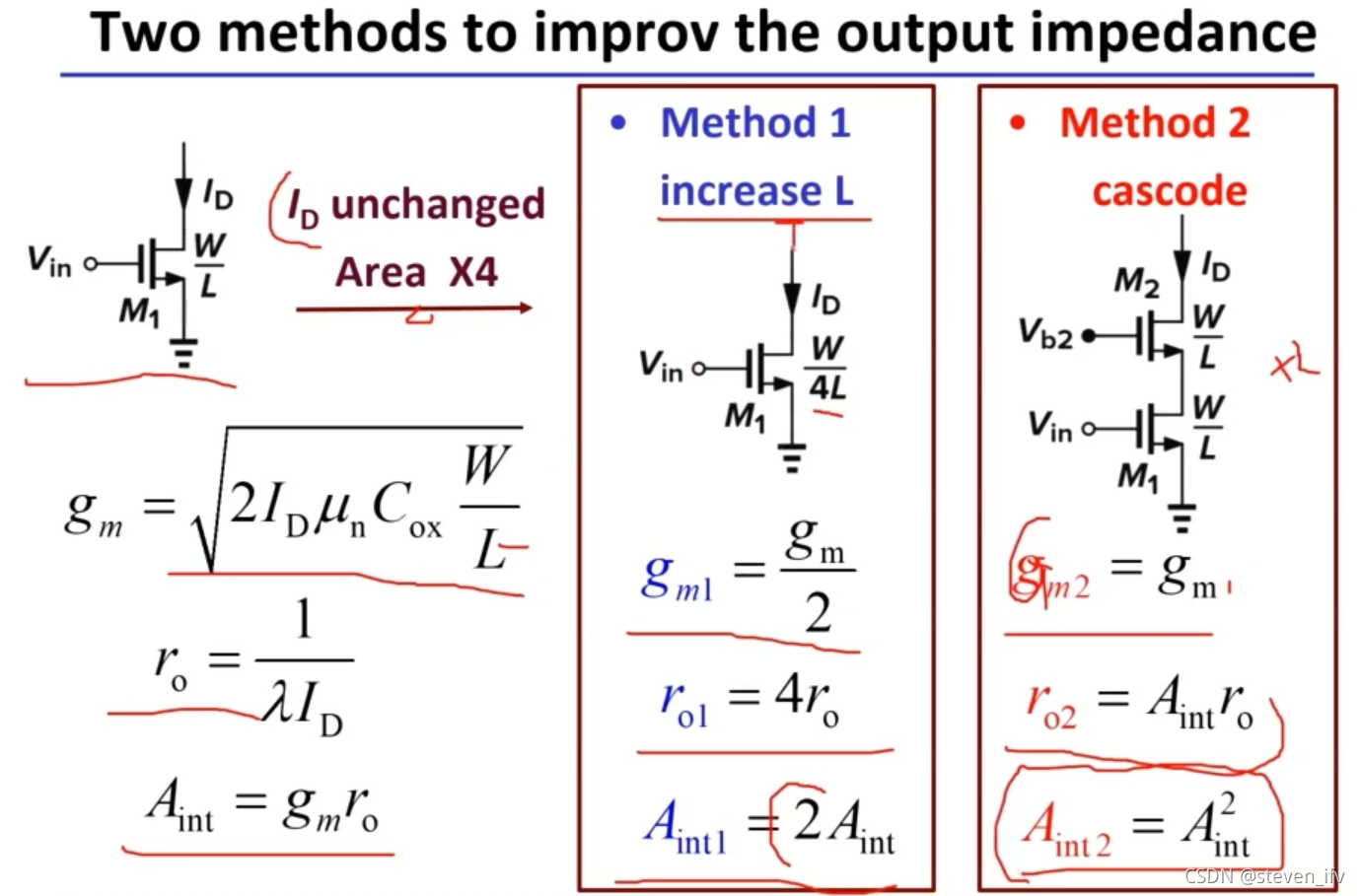

实现几乎∞的输出电阻 但是会损失输出电压的范围 一根管子200mv

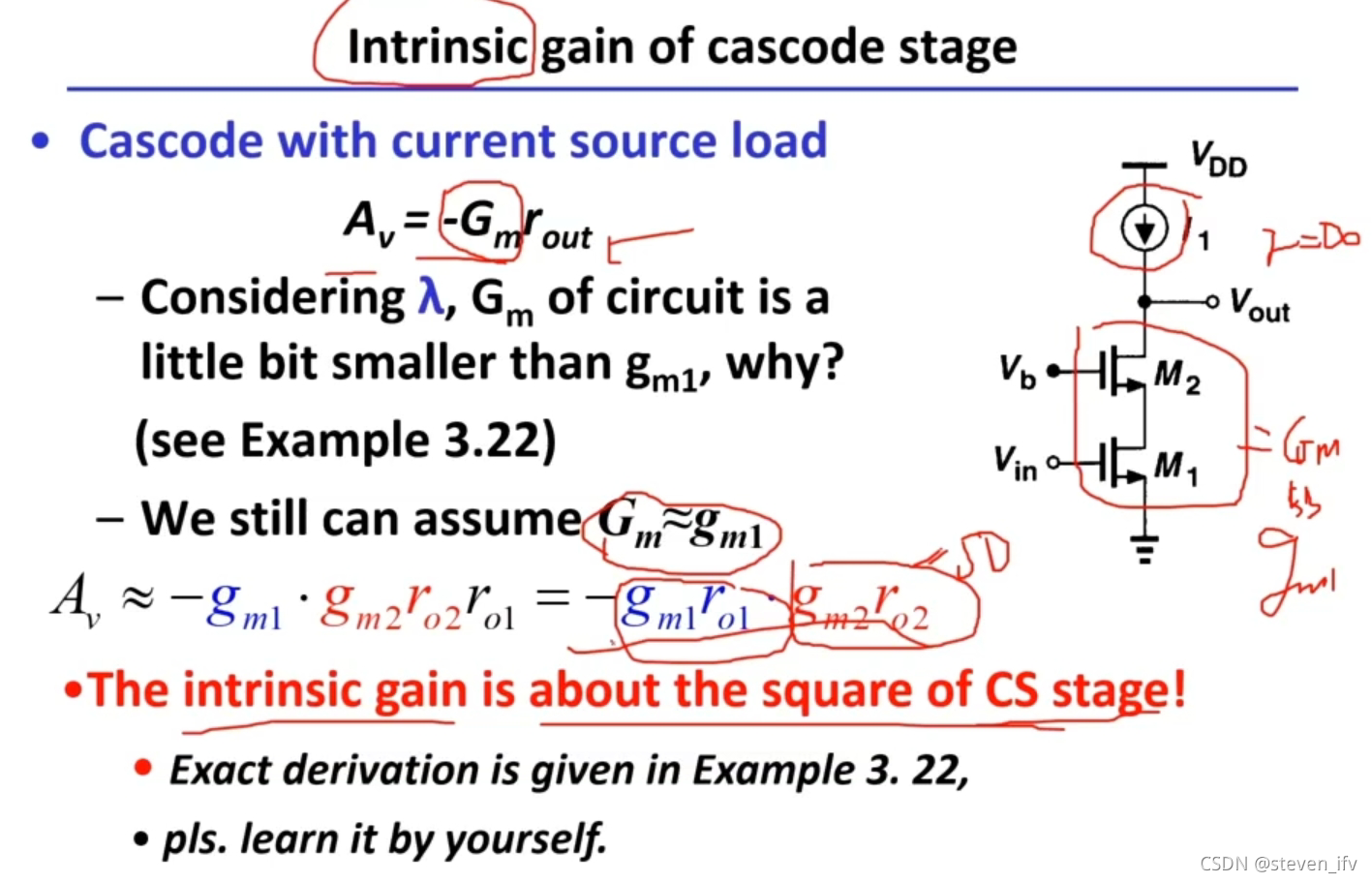

电流源负载时会获得很大的本征增益 但如果接电阻就不会体现出这样的特性

增益可以记为m1的跨导成输出电阻

输入输出的隔离度也会提升;;缺点就是要偏置Vb准确 否则m1就进入线性区了且消耗2Vod(过驱动电压)sway小

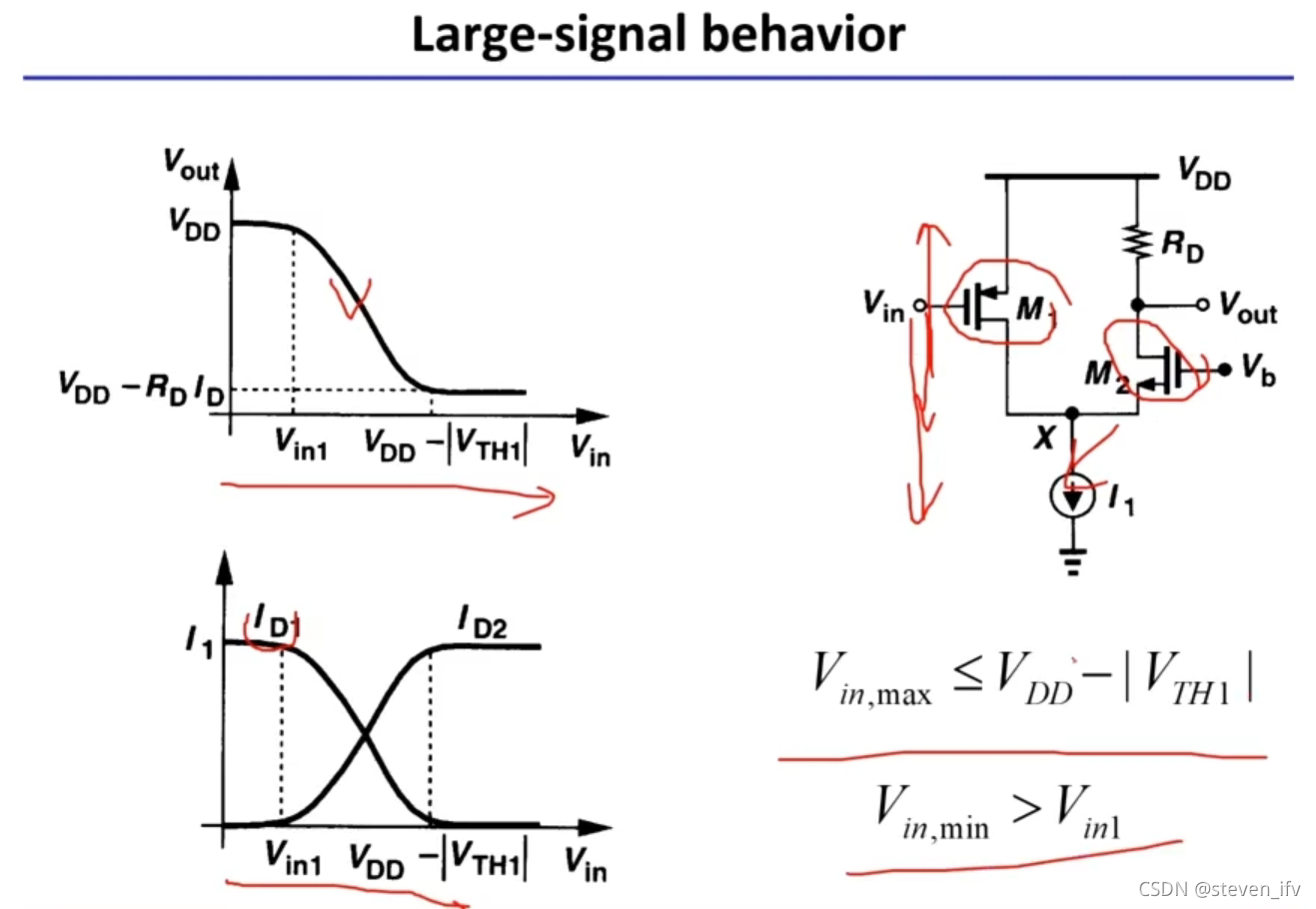

由于上面的结构增益太大了 输入端微小的变化就会引起输出端很大的变化,因此对于高增益放大器不考虑Vin的范围而重点关注Vout的范围

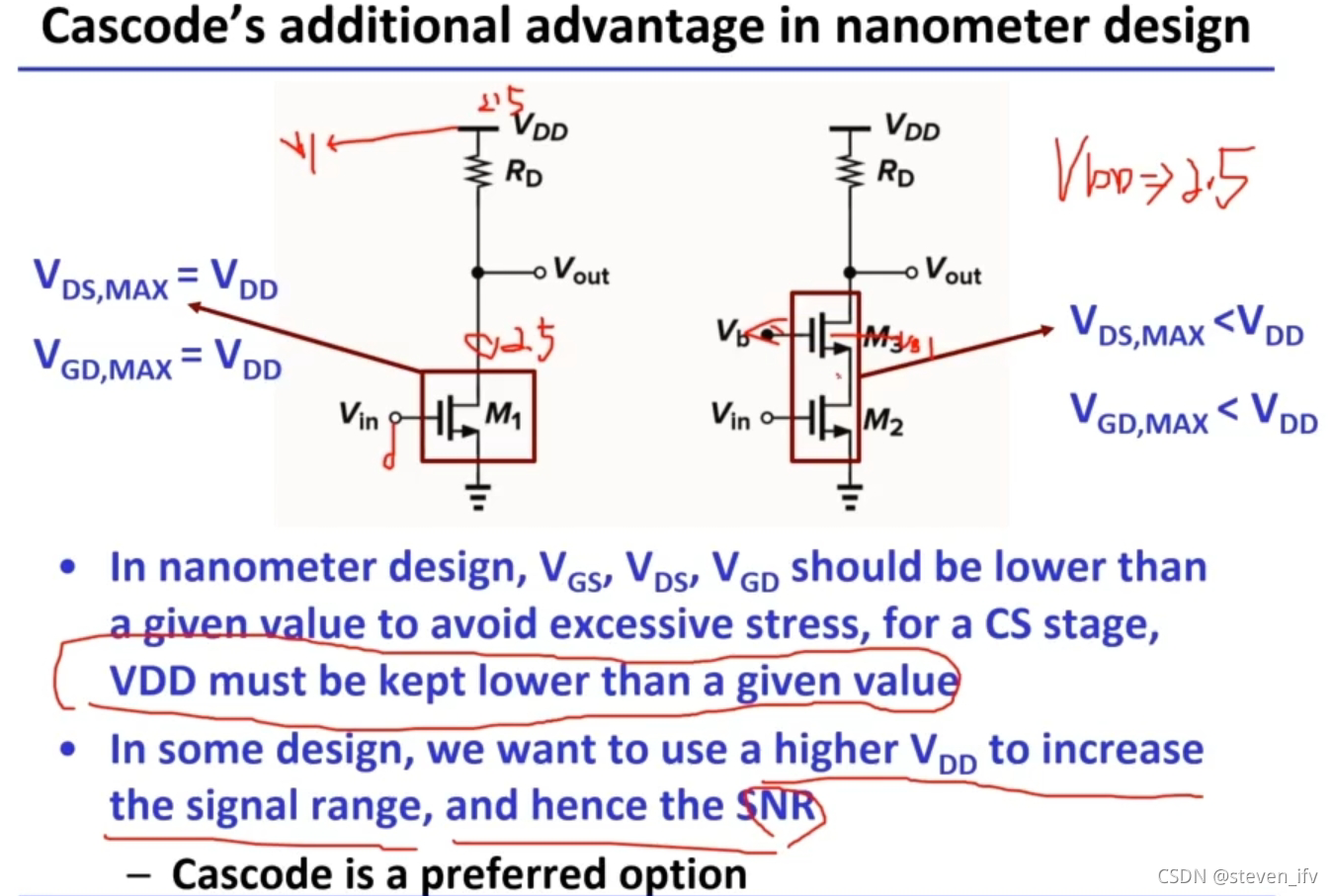

采用cascode结构可以承受更大的电压

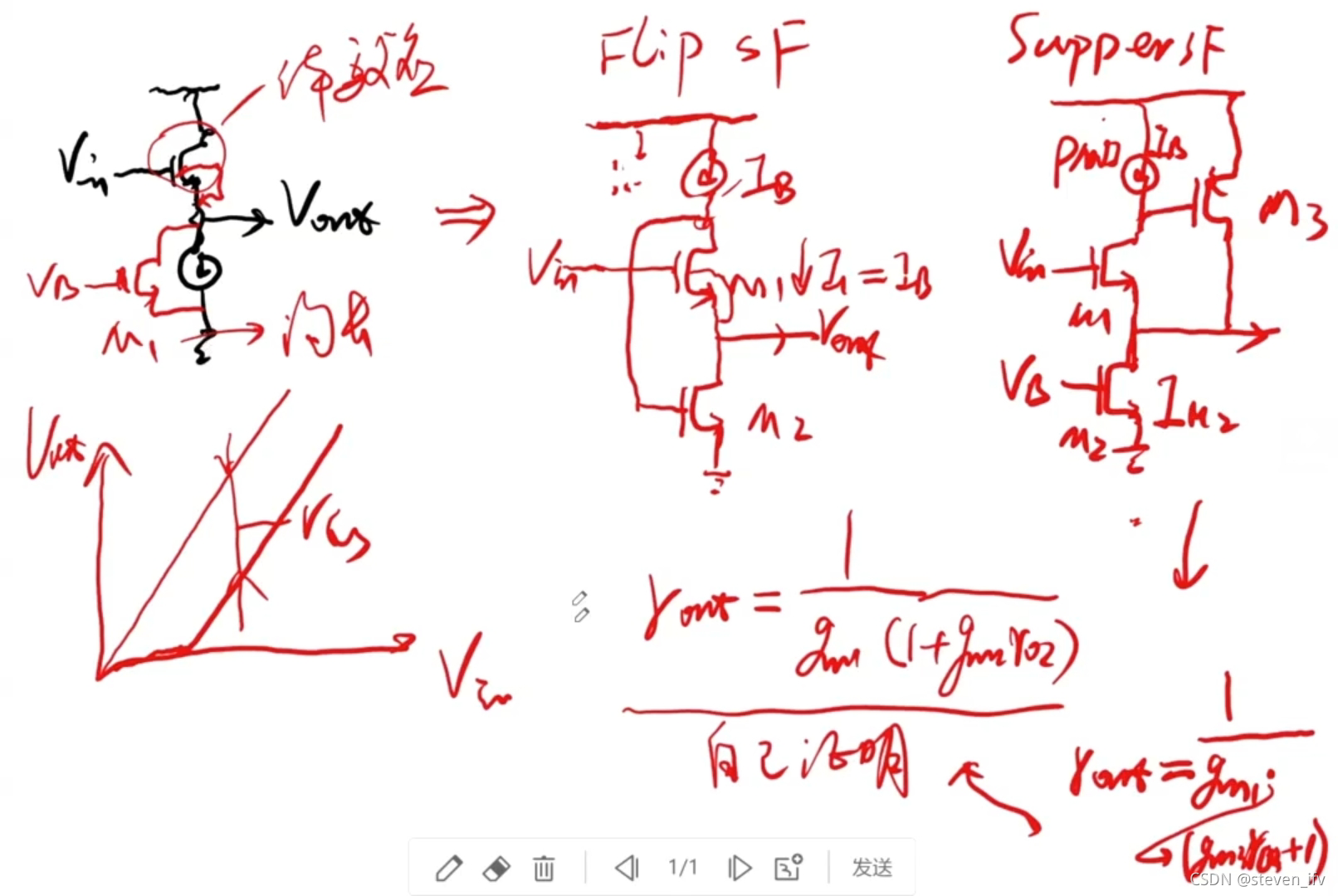

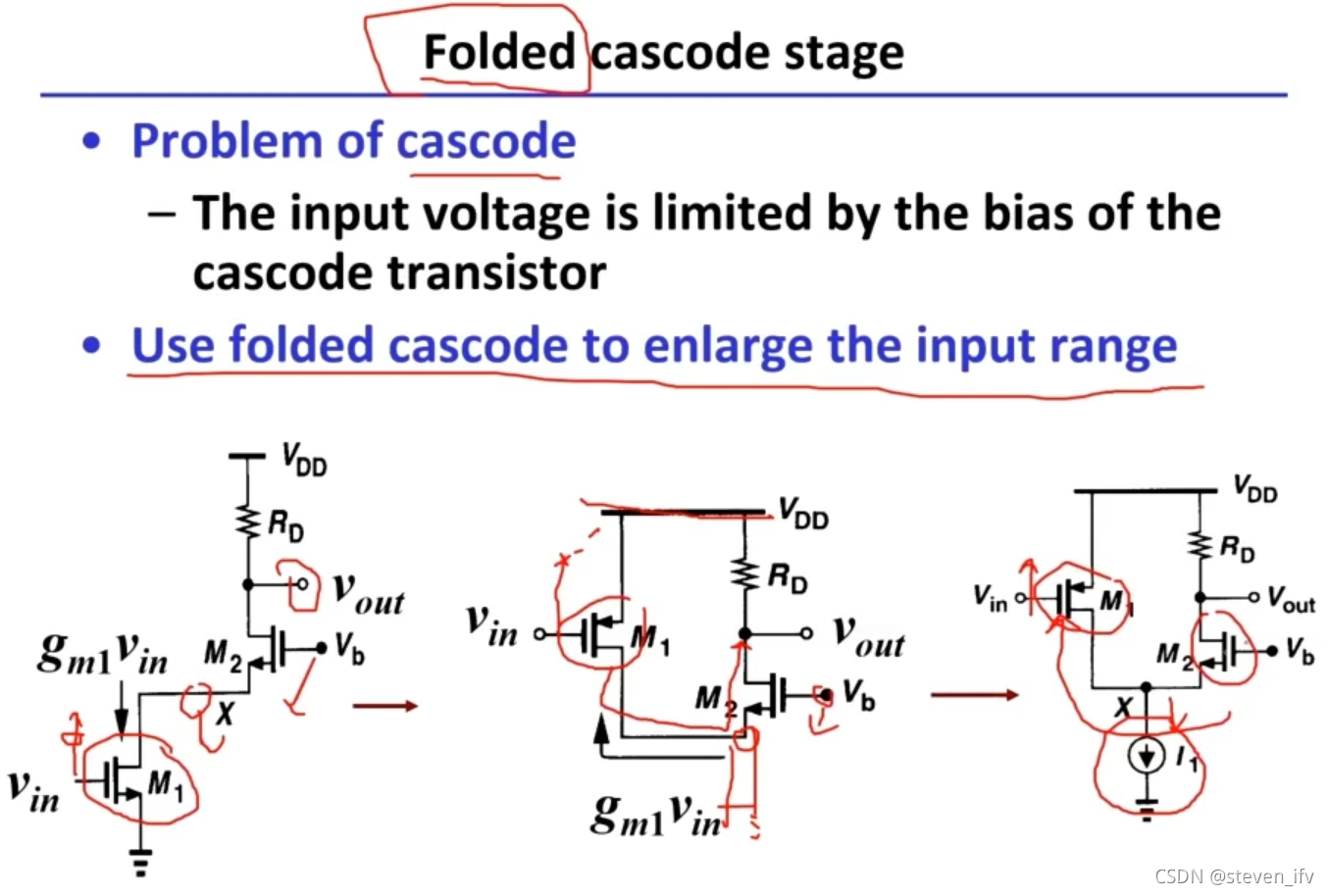

使用folded 可以降低偏置点设置的困难 m1不易被压入线性区

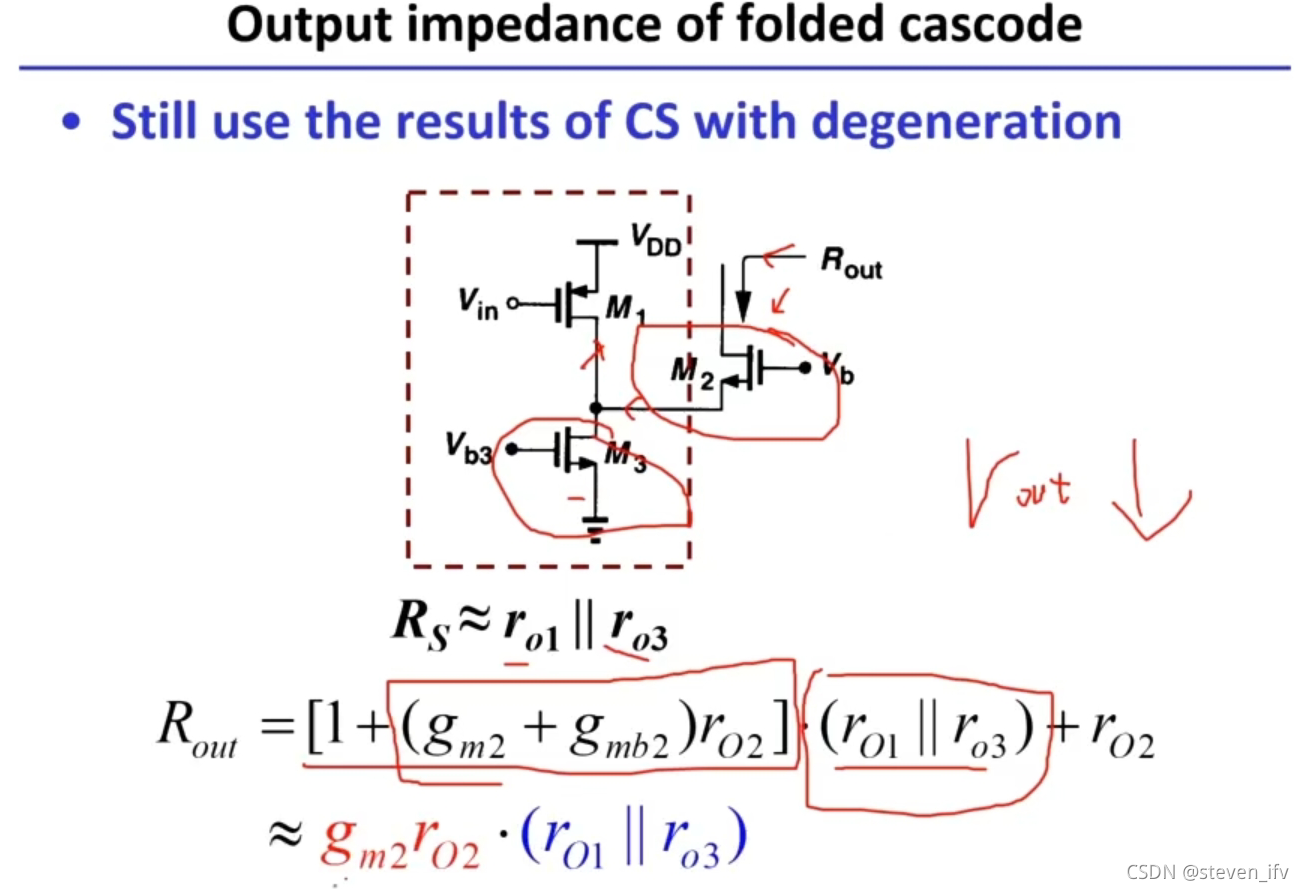

缺点就是rout会下降

缺点就是rout会下降

本文探讨了源随器(CS Stage)在阻抗变换中的作用,强调其在提升增益和实现输入高阻抗、输出低阻抗方面的优势。电流源的引入改善了线性度问题,而共栅放大器(Common-Gate)和共源共栅(Cascode)结构则提供了更高的电压承受能力和输出电阻。Cascode结构通过降低偏置点设置的难度避免了M1进入线性区,但可能降低输出电阻。关键词包括电流源、源随器、共源共栅、增益、阻抗变换。

本文探讨了源随器(CS Stage)在阻抗变换中的作用,强调其在提升增益和实现输入高阻抗、输出低阻抗方面的优势。电流源的引入改善了线性度问题,而共栅放大器(Common-Gate)和共源共栅(Cascode)结构则提供了更高的电压承受能力和输出电阻。Cascode结构通过降低偏置点设置的难度避免了M1进入线性区,但可能降低输出电阻。关键词包括电流源、源随器、共源共栅、增益、阻抗变换。

1186

1186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?