nmos 高电压一侧:drain 低电压一侧:source

pmos 高电压一侧:source 低电压一侧:drain

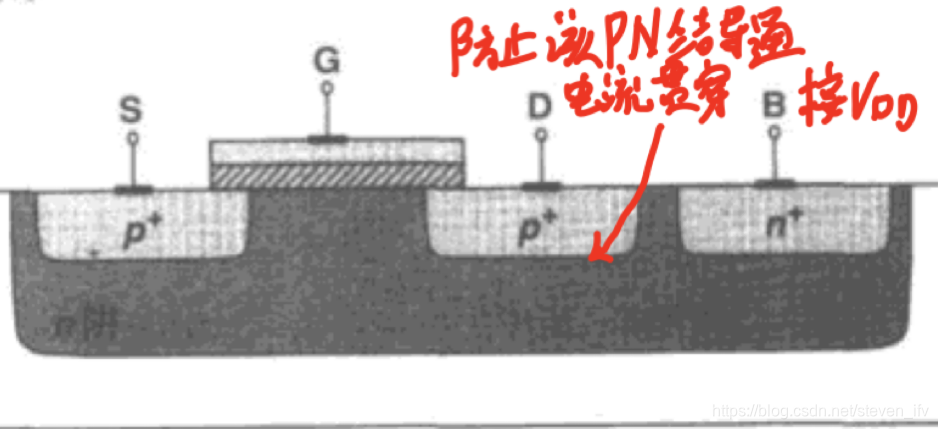

pmos制作在n阱中(n-well)n阱要接电路中最高电位Vdd 使得PN结截止防止贯通(不同pmos的B可以接不同电位)

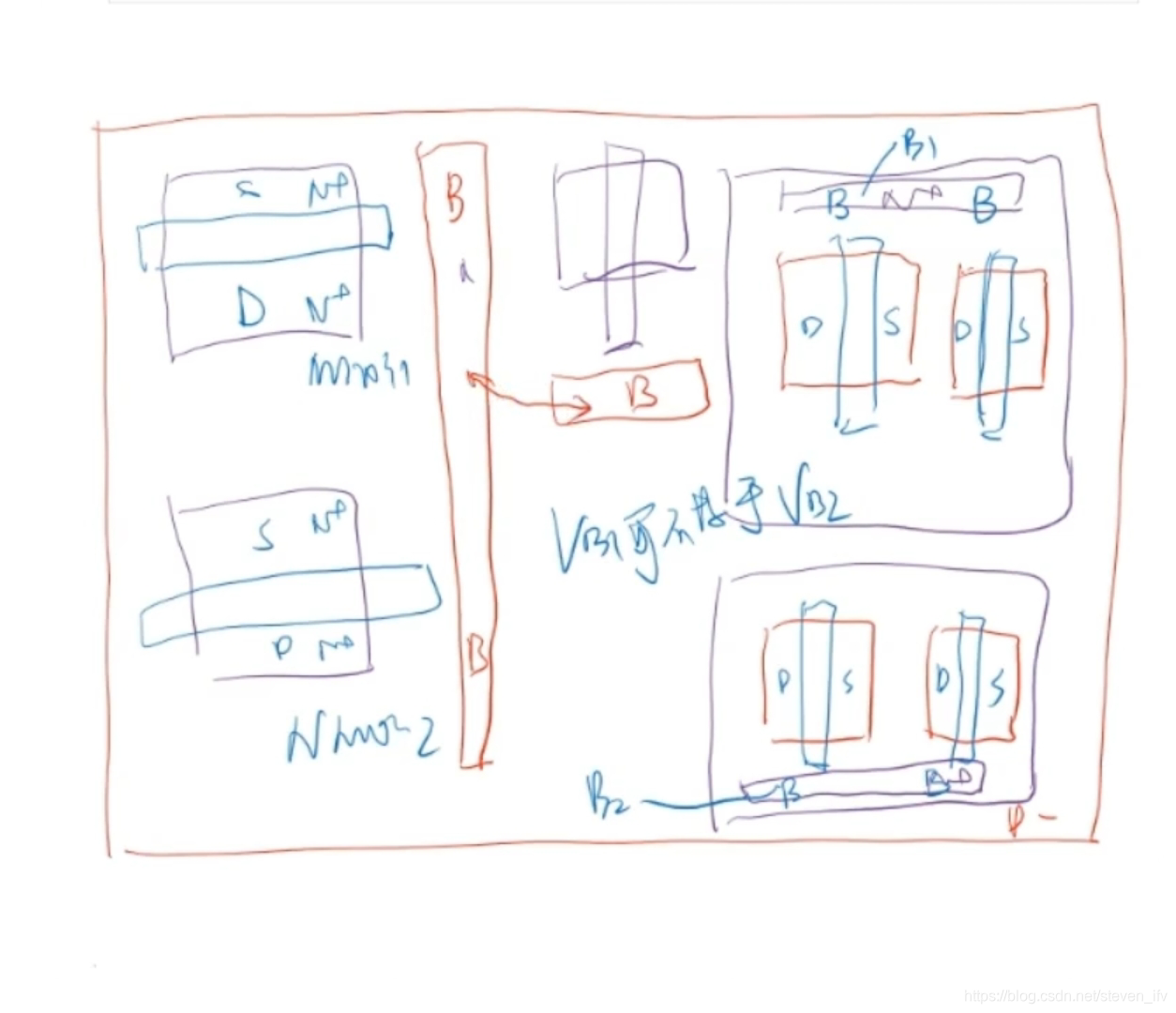

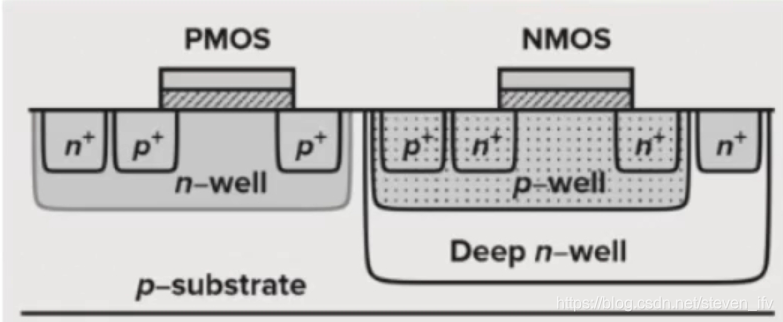

现代常用双阱工艺(double-well)即Psub上也制作浅的P阱 也叫做标准cmos工艺

但不同的nmos的bulk(body)端不能接不同的电压(本质上是在同一块P衬底上),可以看作一块wafer上所有的nmos的B是连在一起的。(通常接地)

crosstalk 各个nmos会相互串扰 因为所有nmos的B端都是连接在一起的

上图为解决方法 深n阱工艺 实现不同nmos有不同bulk(不同电位/降低串扰) 但工艺复杂(更大电路区域/多一层掩膜)

cmos做开关较常见

cmos做压控电流源(VCCS)

331

331

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?