FPGA XDMA 中断模式的PCIE测速例程

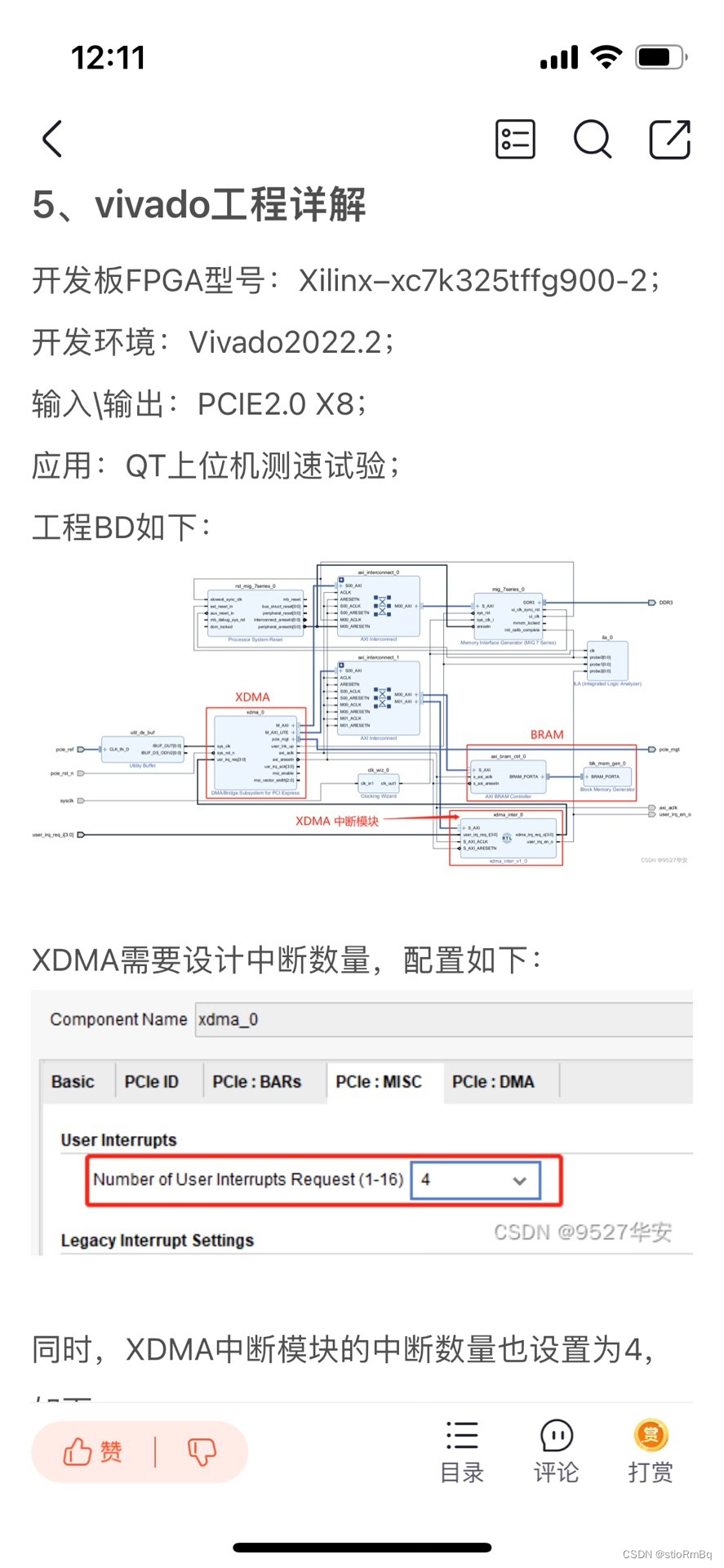

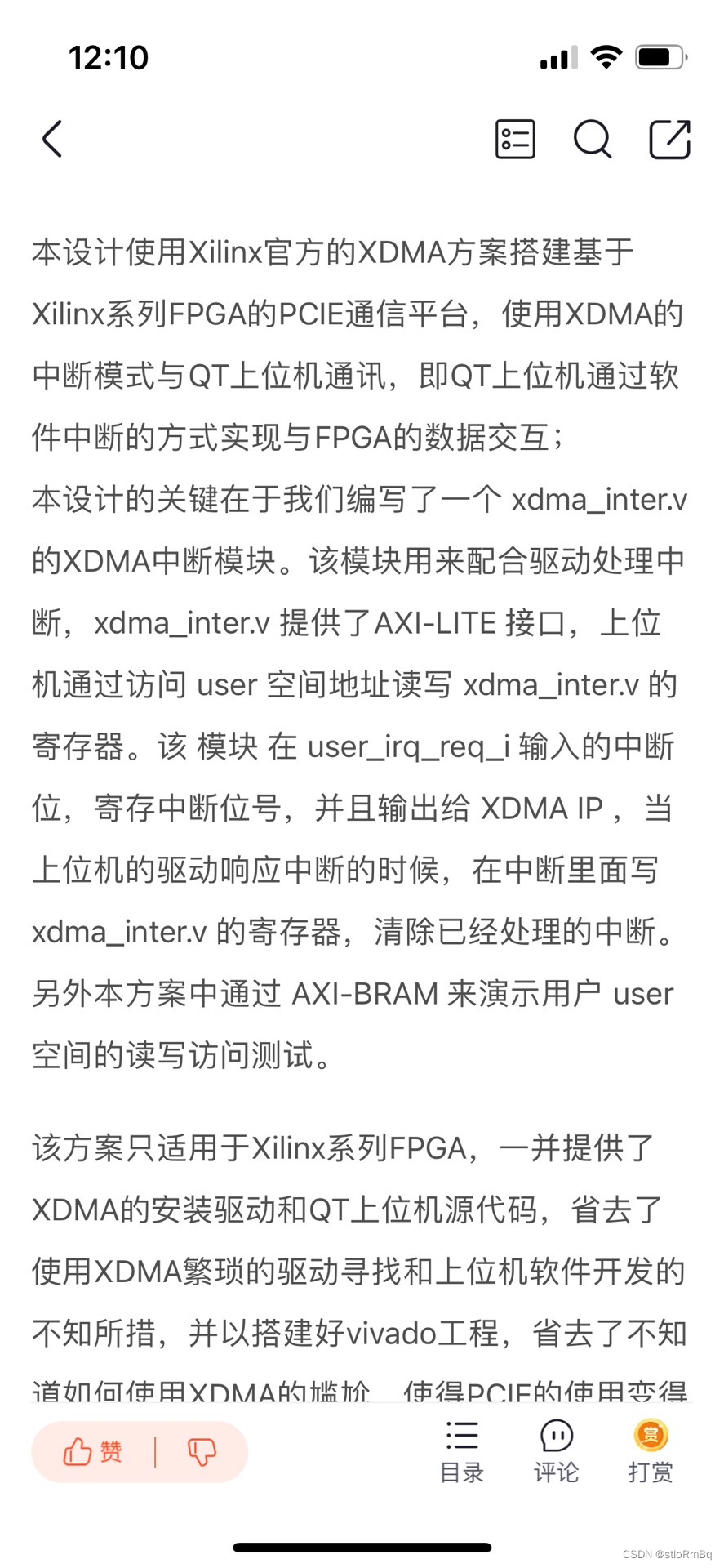

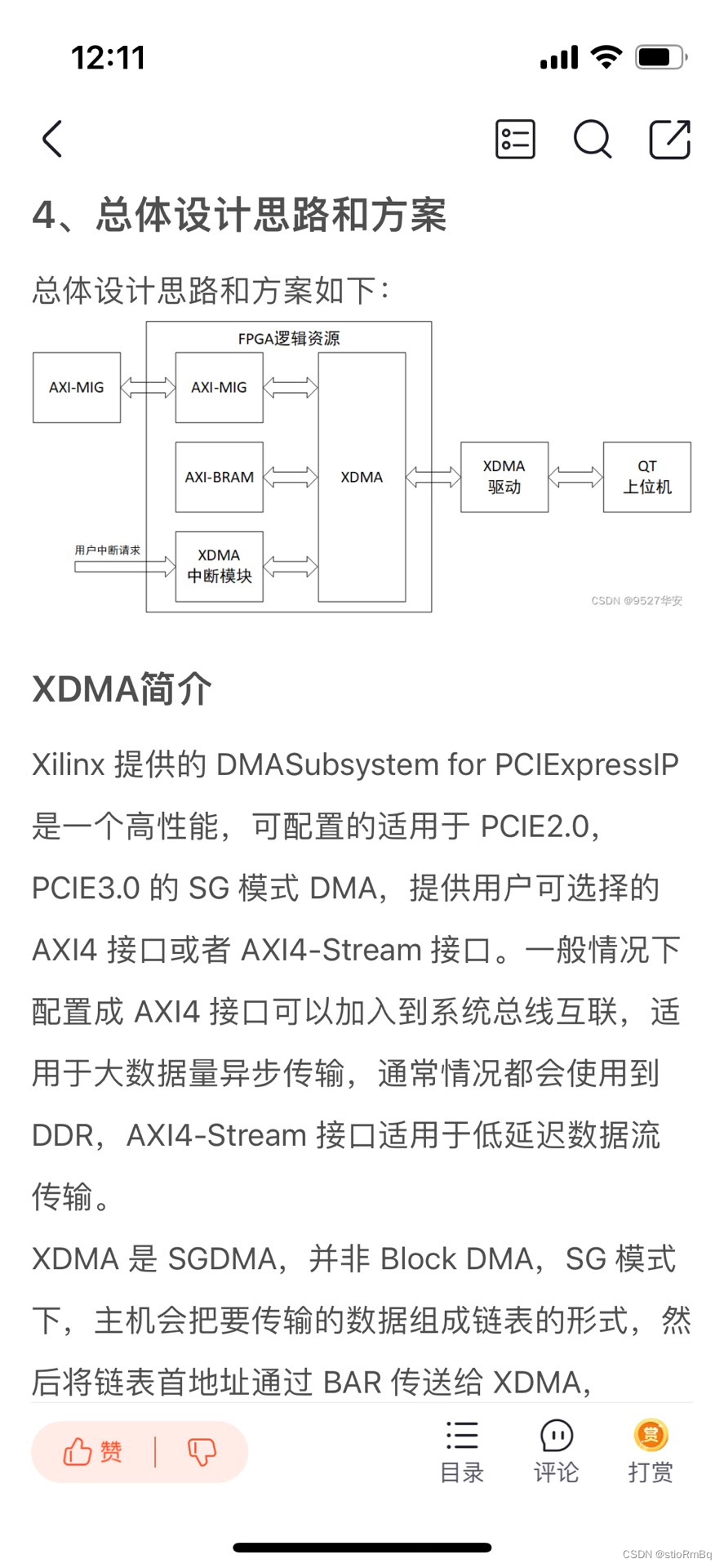

本设计使用Xilinx官方的XDMA方案搭建基于Xilinx系列FPGA的PCIE通信平台,使用XDMA的中断模式与QT上位机通讯,即QT上位机通过软件中断的方式实现与FPGA的数据交互;

本设计的关键在于我们编写了一个 xdma_inter.v 的XDMA中断模块。

该模块用来配合驱动处理中断,xdma_inter.v 提供了AXI-LITE 接口,上位机通过访问 user 空间地址读写 xdma_inter.v 的寄存器。

该 模块 在 user_irq_req_i 输入的中断位,寄存中断位号,并且输出给 XDMA IP ,当上位机的驱动响应中断的时候,在中断里面写 xdma_inter.v 的寄存器,清除已经处理的中断。

另外本方案中通过 AXI-BRAM 来演示用户 user 空间的读写访问测试。

FPGA XDMA 中断模式的PCIE测速例程

引言

随着科技的不断发展,FPGA(Field Programmable Gate Array)逐渐成为创新和解决复杂问题的重要工具。而在FPGA开发中,高速通信是一个关键的技术需求。本文将介绍一种基于Xilinx系列FPGA的PCIE通信平台,该平台利用Xilinx官方提供的XDMA方案,通过中断模式实现与QT上位机的数据交互。

一、设计概述

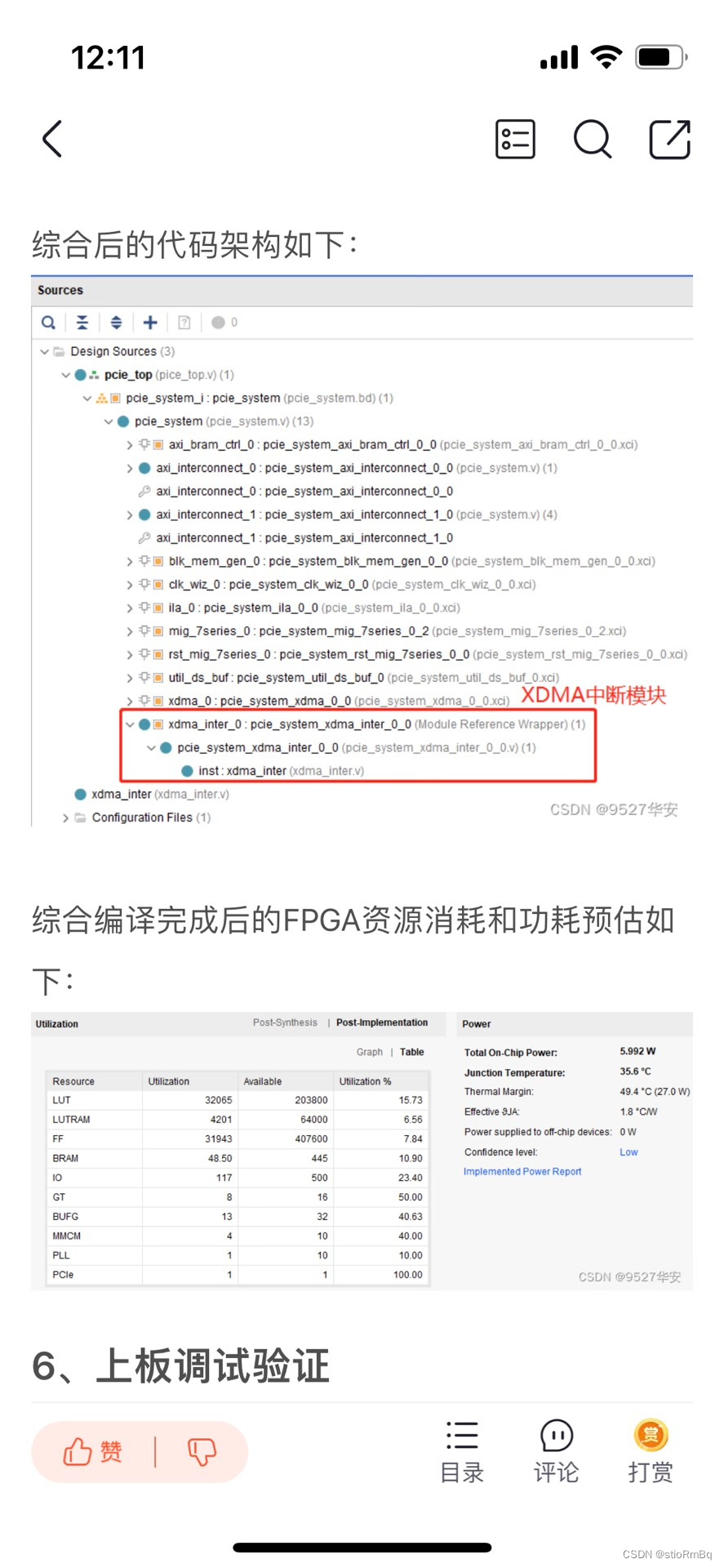

本设计利用Xilinx官方的XDMA方案构建了一个基于Xilinx系列FPGA的PCIE通信平台。该平台通过中断模式与QT上位机进行通信,即QT上位机通过软件中断的方式与FPGA进行数据交互。设计的关键在于编写了一个名为xdma_inter.v的XDMA中断模块。

二、xdma_inter.v模块设计与功能

xdma_inter.v模块是为配合驱动处理中断而编写的。该模块提供了AXI-LITE接口,上位机可以通过访问用户空间地址来读写xdma_inter.v的寄存器。具体功能如下所述:

1. 该模块可以接收来自user_irq_req_i输入的中断信号,将中断位号存入寄存器,并输出给XDMA IP。

2. 当上位机的驱动程序响应中断时,可以在中断程序中写入xdma_inter.v的寄存器,以清除已处理的中断。

三、用户空间读写访问测试

本方案还通过AXI-BRAM来演示用户空间的读写访问测试。用户可以通过该测试来验证用户空间地址的可读写性。

结论

本设计利用Xilinx官方的XDMA方案搭建了一个基于Xilinx系列FPGA的PCIE通信平台,通过中断模式实现了与QT上位机的数据交互。通过编写xdma_inter.v模块,实现了中断的处理和清除功能。此

本文简要介绍了一种基于Xilinx系列FPGA的PCIE通信平台,该平台利用Xilinx官方的XDMA方案,并通过中断模式实现了与QT上位机的数据交互。通过详细阐述xdma_inter.v模块的设计与功能,读者能够更加深入地了解该设计方案的实现原理。同时,通过提供待参考的详细设计文档,读者可以深入研究该技术,并应用于自己的项目中。希望本文对读者在FPGA开发中的工作有所帮助。

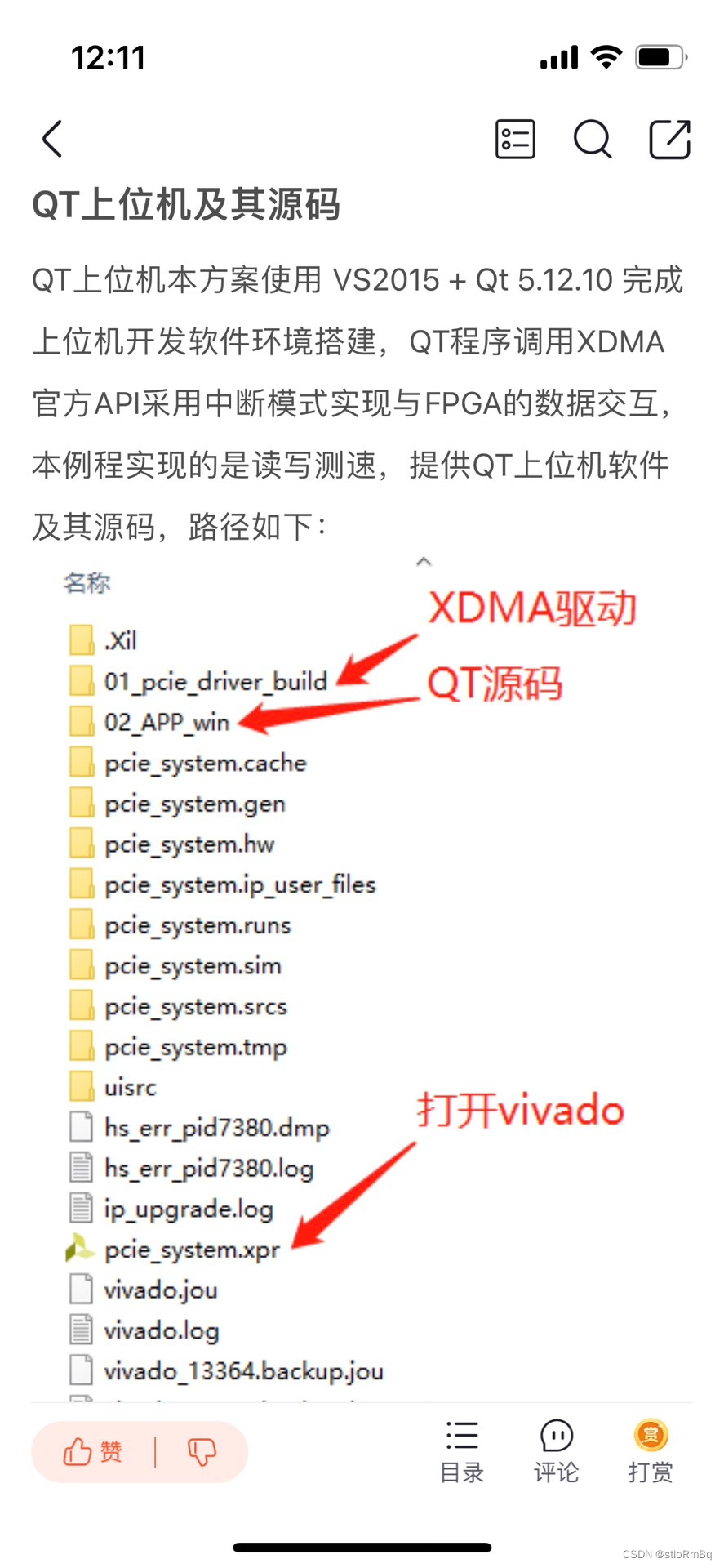

相关代码,程序地址:http://imgcs.cn/lanzoun/724952177152.html

2801

2801

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?