RISC处理器的硬件结构解析

在现代计算机体系结构中,RISC(Reduced Instruction Set Computer,精简指令集计算机)无疑占据了极其重要的地位。RISC的设计哲学是简化指令集,从而实现高效的指令执行速度。与之对应的是CISC(Complex Instruction Set Computer,复杂指令集计算机)。今天我们就来深入探讨RISC的特点以及它的CPU硬件结构。

RISC的核心特点

在探讨RISC的硬件结构前,首先了解RISC的几个核心特点是必要的:

- 简化的指令集: RISC选择使用频率最高的一些简单指令,这些指令不仅简单而且实用。

- 固定的指令长度: RISC的指令长度是固定的,指令格式和寻址方式的种类也较少。

- 存储器访问限制: 在RISC中,只有加载和存储指令可以访问存储器,其他的指令仅在寄存器间进行操作。

- 富集的通用寄存器: RISC处理器通常包含数量众多的通用寄存器。

- 高效的指令执行: 大部分指令可以在一个机器周期内完成,尤其是在采用流水线技术的情况下。

- 硬布线控制: RISC偏向于使用硬布线控制而不是微程序控制,这样可以进一步提高执行速度。

- 优化的编译器: RISC处理器通常配合高级语言和优化的编译器,这样可以减少程序的执行时间。

SPARC CPU的硬件结构

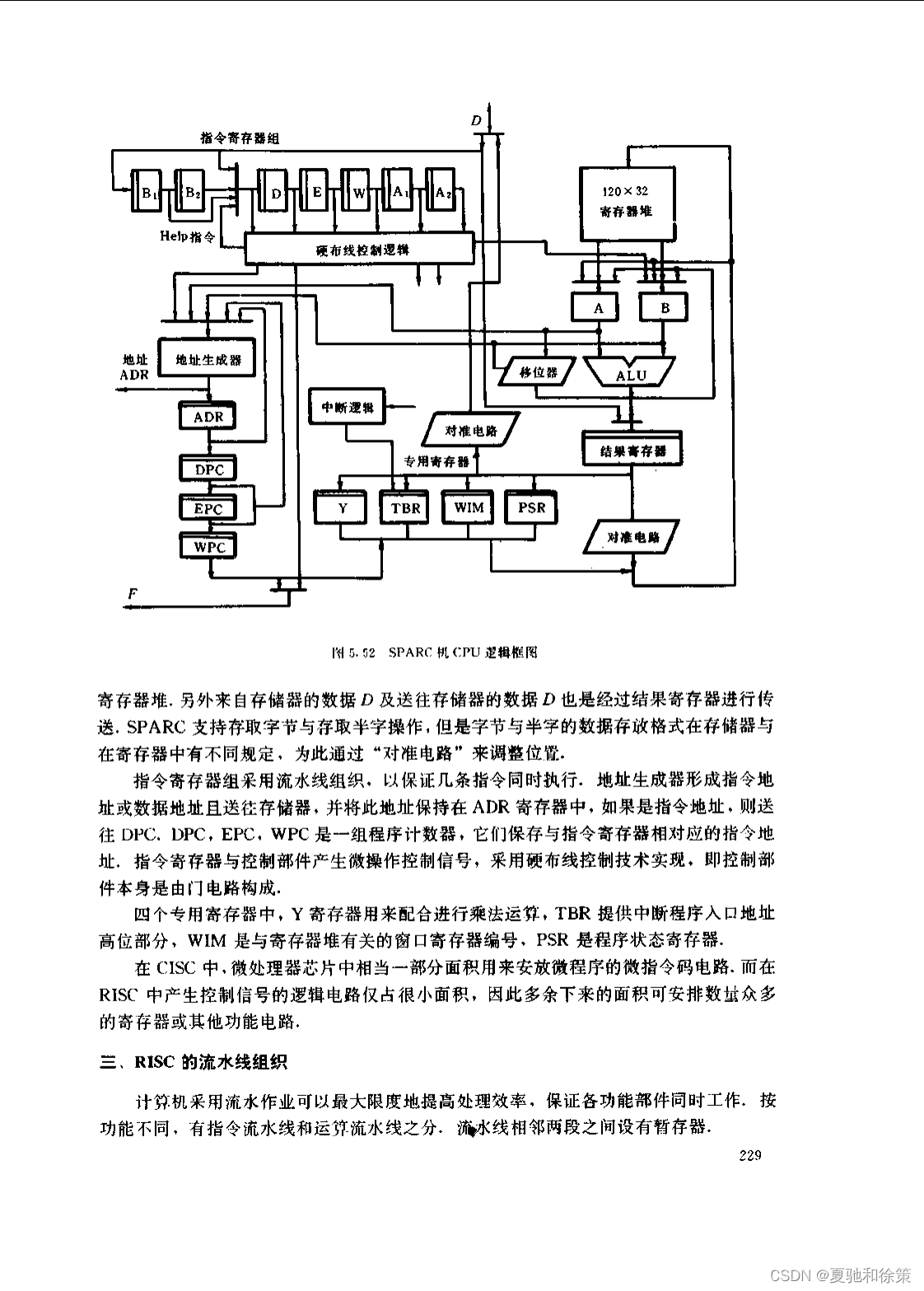

SPARC是一种经典的RISC架构,其CPU的硬件结构反映了RISC的设计理念。下面是对SPARC CPU硬件结构的详细解析:

运算器和控制器

在SPARC的CPU架构中,右半部分是由运算器组成,负责执行各种算术和逻辑运算;左半部分是控制器,负责指令的译码、执行控制等。

算术逻辑单元(ALU)

ALU是32位的,它可以执行算术和逻辑运算。与ALU紧密相关的是移位器,它能够在一个机器周期内完成0到31位之间的任意位移操作。

寄存器堆

SPARC拥有一个非常大的寄存器堆,共有120个32位的寄存器,以便提供足够的寄存器进行运算操作。源操作数和运算结果都是来自于或者送往这个寄存器堆。

对准电路

对于字节和半字的操作,SPARC提供了专门的对准电路,以确保数据在存储器与寄存器中的格式能够正确匹配。

指令寄存器和程序计数器

SPARC采用流水线技术,可以同时执行多条指令。地址生成器负责形成指令地址或数据地址,并通过程序计数器组(DPC、EPC、WPC)保持这些地址。

专用寄存器

在SPARC中,还有几个专用寄存器如Y寄存器用于辅助乘法运算,TBR用于提供中断程序入口地址,WIM与寄存器堆有关的窗口寄存器编号,PSR则是程序状态寄存器。

硬布线控制技术

在RISC中,硬布线控制技术取代了传统CISC处理器中微指令码电路的角色,极大地简化了CPU内部的控制逻辑。

在RISC设计理念的引领下,SPARC机CPU表现出了优异的处理能力和高效的性能表现。它的成功案例激励了后续更多的RISC架构的发展,为我们提供了计算能力上的巨大提升。

RISC流水线组织的高效性分析

在现代计算机架构中,流水线技术是一项革命性的设计,它大幅提高了处理器的工作效率。RISC(精简指令集计算机)架构采用流水线设计来实现指令的快速执行。让我们一起来探究RISC流水线的组织原理,以及它是如何在SPARC(一种典型的RISC架构)中得到应用的。

流水线作业的基本概念

流水线作业的基本思想是将一个任务分解成若干个子任务,每个子任务由流水线的不同阶段并行处理。这样的分工合作能确保处理器的每个部件都能持续工作,避免了因等待某个特定操作而产生的闲置时间。

指令流水线与运算流水线

在RISC架构中,流水线可以分为指令流水线和运算流水线两大类。指令流水线负责指令的取出、译码、执行等过程;而运算流水线则专注于指令执行过程中的具体算术或逻辑运算。

SPARC的流水线设计

SPARC处理器的流水线采用四级设计,这四个级别分别是:取指、译码、执行和写回。这种组织确保了处理器在每个机器周期都能完成一条指令的某一操作。

四级指令流水线

SPARC的四级指令流水线工作原理如下:

- 取指阶段:首先从存储器中取出指令,并送入D寄存器。

- 译码阶段:指令从D寄存器送入E寄存器,在这一阶段完成译码。

- 执行阶段:指令移至W寄存器,ALU完成加法等运算。

- 写回阶段:最终,运算结果被写回寄存器。

流水线的并行工作

在任一给定的机器周期中,SPARC可以同时处理多条指令。例如,当CPU正在取第n+3条指令时,第n+2条指令会在D寄存器中译码,第n+1条指令在E寄存器中等待执行,而第n条指令则在W寄存器中完成写回操作。

存储器的读写与机器周期

通常存储器的读写速度比CPU的处理速度慢,因此存储器的读写周期会决定整个机器周期的长度。为了缩短机器周期,提高效率,SPARC采取了指令预取和Cache存储器的策略。

指令预取与Cache应用

指令预取机制通过在CPU中设置一个指令寄存器堆,将指令提前从存储器取到寄存器堆中。而Cache的使用则可以避免因指令预取而可能出现的数据无效问题,因为大多数RISC机器采用Cache方案。

处理复杂指令

SPARC在处理如LOAD指令这样的复杂指令时,会增加一个机器周期。这是因为除了取指之外,还需要从存储器中取出数据。为了不影响流水线的效率,SPARC在D段发现LOAD指令时,会通过控制硬件生成一条空操作指令(Help指令),并将取出的指令暂存在缓冲寄存器中。

数据依赖性和指令转移问题

在连续的加法指令中,如果源操作数和目标操作数寄存器相同,将出现数据依赖性问题。SPARC通过设置专用通路直接将ALU的输出传送给需要的寄存器来解决这个问题。

当执行转移指令时,由于转移地址需要经过判断和计算,下一条指令的取指操作会被推迟,导致流水线暂时失去效率。为了解决这个问题,SPARC设计者通过软硬件的紧密结合,采用编译优化技术,在转移指令后插入必执行的指令,从而保持流水线的畅通。

RISC架构下的SPARC处理器展示了流水线组织在提高计算机处理能力方面的巨大潜力。通过精妙的设计,流水线技术不仅解决了复杂计算任务,也为我们提供了更高效的处理速度。

深入理解RISC寄存器及其优化策略

在对比RISC与CISC(复杂指令集计算机)的设计理念时,我们不难发现,RISC架构通过增加寄存器的数量来减少对存储器的访问次数,这一策略有效提升了程序的运行效率。接下来,我们将详细探讨RISC中的寄存器组织以及SPARC架构如何运用这些原则以优化性能。

RISC寄存器的优化方案

RISC系统通常采用两种主要策略来优化寄存器的使用:

- 大量寄存器堆的应用: RISC通过实现一个较大的寄存器堆并组成若干个寄存器窗口,以此提高程序的运行速度。这利用了重叠寄存器窗口技术,减少了访问存储器的需要。

- 寄存器分配算法: 结合编译器的优化处理,采用一套高效的寄存器分配算法,以充分利用可用的寄存器资源,这在编译时期尤为重要。

SPARC的寄存器窗口

SPARC机采用的是第一种优化方案。在这种架构下,指令寄存器的地址码字段长5位,能够访问32个逻辑寄存器,具体分为全局寄存器和窗口寄存器。

全局寄存器与窗口寄存器

- 全局寄存器: 共有8个,对所有程序都是可见的。

- 窗口寄存器: 其余24个寄存器被组成窗口,分为输入、局部和输出三部分。

寄存器窗口技术

SPARC允许设置多个窗口,窗口数由硬件设计决定。当前程序访问的窗口由窗口指针(CWP)指出。通过这种技术,过程调用和参数传递不需要存储器的参与,从而极大地提高了执行速度。

寄存器窗口的工作原理

下面是一个三层嵌套程序调用的例子,以展示寄存器窗口技术的高效性:

- 过程A调用过程B: 过程A的输出寄存器(outs)存放将要传递给过程B的参数。过程B通过自己的输入寄存器(ins)直接获得这些参数,无需访问存储器。

- 过程B调用过程C: 类似地,过程B将参数传递给过程C的输入寄存器。

寄存器窗口的调用与返回

当一个过程调用完毕并返回时,它的返回值被放入其输入寄存器中,这时调用它的过程可以直接从自己的输出寄存器中获取返回值。

寄存器窗口的编号和循环处理

每个窗口都有一个编号,并且这些编号是循环处理的。例如,如果有8个窗口,编号将是0到7,窗口6的上一个窗口是窗口7,而窗口7的下一个窗口又是窗口0。

寄存器窗口溢出处理

当嵌套程序的层数超过窗口数量时,会发生窗口溢出。这种情况下,最早的窗口内容会被保存到存储器中,由WIM专用寄存器指示这一窗口的编号。必要时,这些内容会从存储器中恢复。

通过上述分析可见,RISC的寄存器组织和管理是其高性能的关键所在。SPARC架构通过寄存器窗口技术,优雅地解决了参数传递和过程调用的问题,极大地减少了访问存储器的次数,为现代高性能计算设立了标杆。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?