第六章 时序逻辑电路

6.1 概述

时序逻辑电路的基本概念

时序逻辑电路是区别于组合逻辑电路的一类重要电路。在组合逻辑电路中,任一时刻的输出信号仅依赖于当前的输入信号,而在时序逻辑电路中,输出信号不仅取决于当前输入信号,还取决于电路的当前状态,即电路的历史输入。因此,时序逻辑电路需要具备记忆功能。

时序逻辑电路一般由两个部分组成:

- 组合逻辑电路:负责当前输入信号和存储电路输出信号的逻辑运算。

- 存储电路:负责记忆电路的状态,通常由触发器(如D触发器、JK触发器等)构成。

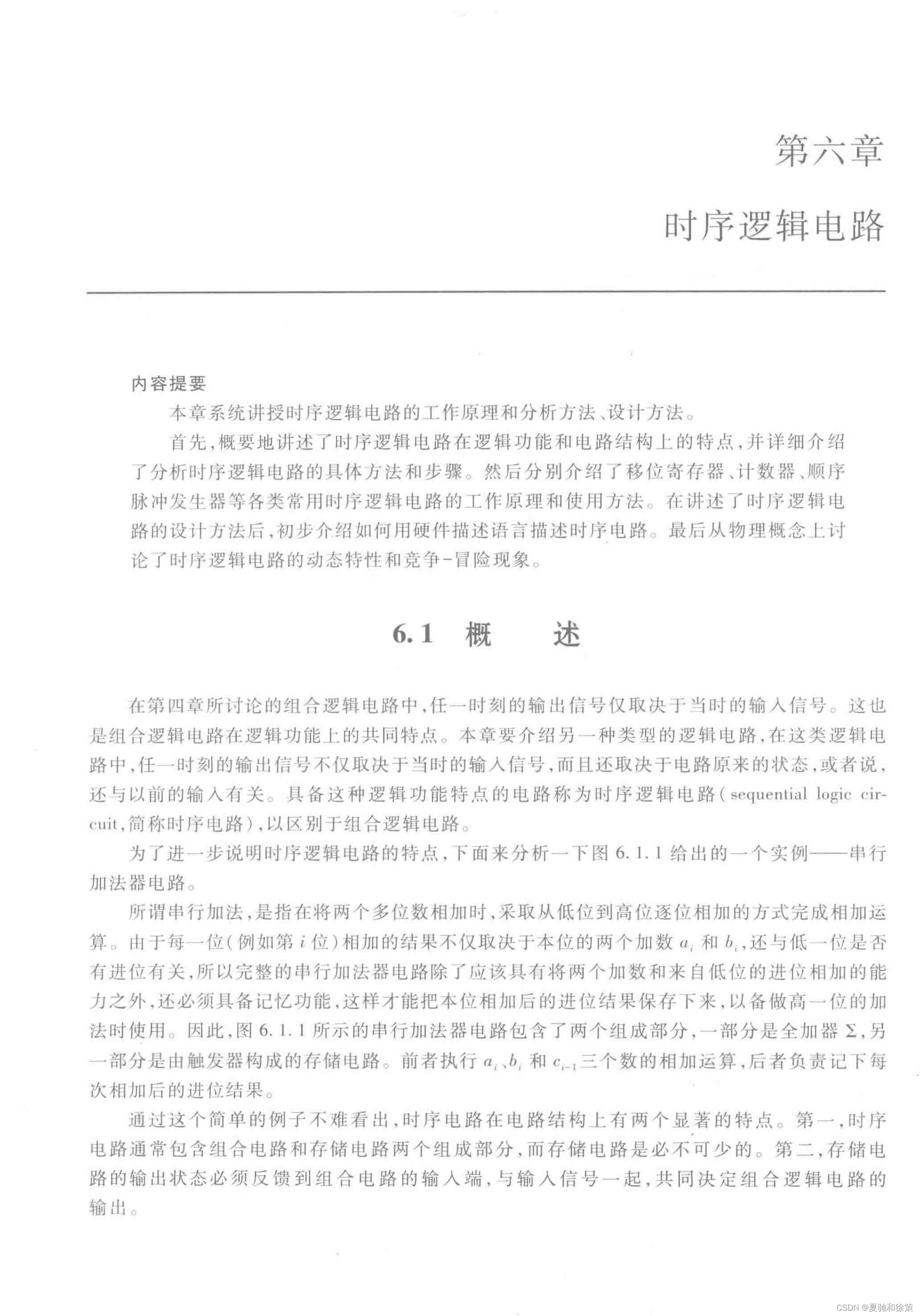

例如,图6.1.1中的串行加法器电路展示了时序逻辑电路的典型结构。

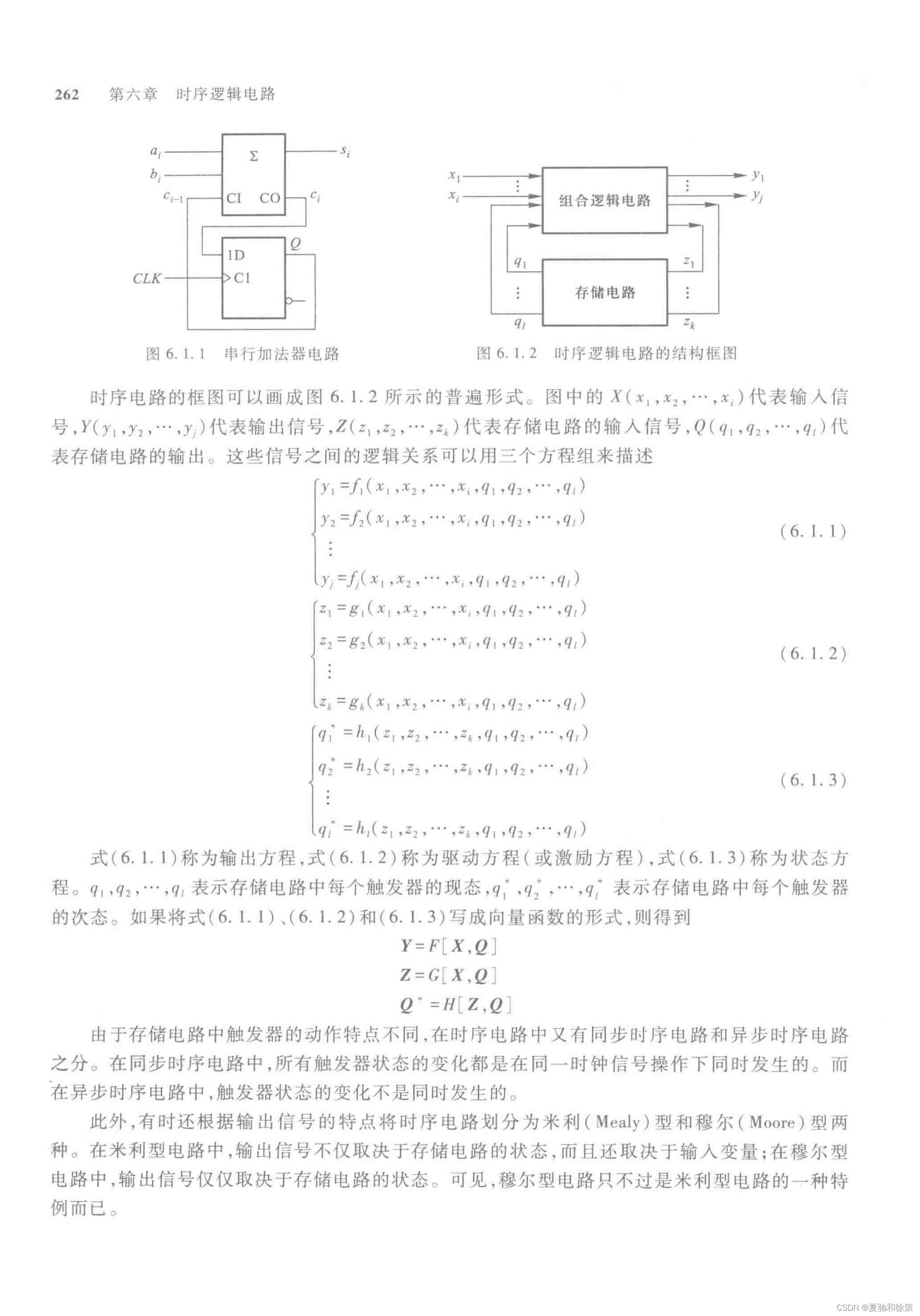

时序逻辑电路的结构框图

时序逻辑电路的框图如图6.1.2所示,其中包含输入信号𝑋(𝑥1,𝑥2,...,𝑥𝑘)X(x1,x2,...,xk)、输出信号𝑌(𝑦1,𝑦2,...,𝑦𝑟)Y(y1,y2,...,yr)、存储电路的输入信号𝑍(𝑧1,𝑧2,...,𝑧𝑙)Z(z1,z2,...,zl)和存储电路的输出信号𝑄(𝑞1,𝑞2,...,𝑞𝑚)Q(q1,q2,...,qm)。

这些信号之间的逻辑关系可以用以下三个方程组描述:

输出方程

描述输出信号与输入信号及存储电路输出信号之间的关系

𝑦𝑖=𝑓𝑖(𝑥1,𝑥2,...,𝑥𝑘,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑟)yi=fi(x1,x2,...,xk,q1,q2,...,qm)(i=1,2,...,r)

驱动方程(激励方程)

描述存储电路的输入信号与输入信号及存储电路输出信号之间的关系

𝑧𝑖=𝑔𝑖(𝑥1,𝑥2,...,𝑥𝑘,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑙)zi=gi(x1,x2,...,xk,q1,q2,...,qm)(i=1,2,...,l)

状态方程

描述存储电路的次态信号与存储电路输入信号及存储电路当前输出信号之间的关系

𝑞𝑖′=ℎ𝑖(𝑧1,𝑧2,...,𝑧𝑙,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑚)qi′=hi(z1,z2,...,zl,q1,q2,...,qm)(i=1,2,...,m)

这些方程可以简写为向量函数的形式:

𝑌=𝐹[𝑋,𝑄]Y=F[X,Q]

𝑍=𝐺[𝑋,𝑄]Z=G[X,Q]

𝑄′=𝐻[𝑍,𝑄]Q′=H[Z,Q]

同步时序电路与异步时序电路

根据存储电路中触发器的动作特点,时序电路可以分为同步时序电路和异步时序电路:

- 同步时序电路:所有触发器的状态变化都在同一时钟信号操作下同时发生。

- 异步时序电路:触发器的状态变化不是同时发生的。

此外,时序电路根据输出信号的特点还可分为米利型(Mealy)电路和穆尔型(Moore)电路:

- 米利型电路:输出信号不仅取决于存储电路的状态,还取决于输入信号。

- 穆尔型电路:输出信号仅取决于存储电路的状态。

时序电路的分析方法

在分析时序电路时,需要将状态变量和输入信号一样当作逻辑函数的输入变量处理。由于状态变量的取值与电路的历史情况有关,时序电路的分析比组合电路复杂。

常用的分析方法包括:

- 状态表法:列出电路所有可能的状态及其对应的输出和次态。

- 状态图法:用状态图形象地描述电路的状态转换过程。

时序电路的设计方法

时序电路的设计较为复杂,通常包括以下步骤:

- 明确设计要求:确定电路所需的功能和性能指标。

- 状态分析与设计:定义状态,绘制状态图或状态表。

- 选择触发器类型:根据设计需要选择合适的触发器。

- 设计组合逻辑部分:实现状态转移逻辑和输出逻辑。

- 验证与优化:通过仿真或实验验证设计的正确性,并进行优化。

总结

通过以上分析,我们了解到时序逻辑电路不仅依赖于当前输入信号,还依赖于电路的状态。这使得时序逻辑电路在逻辑功能和电路结构上具有独特的特点。在设计与分析时序逻辑电路时,需要综合考虑状态变量、输入信号及其相互关系,采用系统化的方法进行分析与设计。

208

208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?