1、什么是I2C协议

I2C是由Philips开发的简单的双向两线总线,I2C协议由数据线 SDA 和时钟线 SCL 构成通信线路,既可用于 发送数据,也可接收数据属于半双工协议(即同一时刻,数据单向流动)。此外,I2C也是一种可以多主设备,多从设备的总线协议,通过地址索引,I2C可以使能所需从设备,I2C的出现主要是用来实现不同集成电路组件之间的控制功能,比如通过I2C协议,连接MCU与LCD驱动器,远程I/O口,RAM,EEPROM或数据转换器。

2、I2C、spi、uart的区别

重点解释一下UART,SPI,I2C这三个协议的选通方式。

对于UART来说,正常来说是没有办法满足一个主设备,多个从设备的通信,它的通信方式最为简单,最低只需要一根线即可完成通信,协议本身并不允许外接多个从设备,但是我们也可以通过比如485转接、增加二极管的方式来进行多从设备选择(电路层面的设计内容,不是数字IC需要考虑的内容)。

其次是SPI协议,它有一个专门的NSS端口,默认拉低来选择所需的从设备。

最后是I2C协议,每个主设备和每个从设备都对应一个地址,通信的时候先发送地址信号,若一致,则被选中。

3、I2C的信号线

I2C仅需要两根信号线即可完成通信,除此以外,I2C的信号线需要连接上拉电路。

- 它是一个支持多设备的总线(支持多主机多从机)。

- IIC 总线只使用两条总线线路,一条双向串行数据线(SDA) 一条 串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

- 每个连接到 IIC 总线的设备都有一个独立的地址,主机可以利 用设备独立地址访问不同设备。

- IIC 总线通过上拉电阻接到电源。当 IIC 设备空闲时,设备会输 出高阻态,当所有设备都空闲,都输出高阻态时,由上拉电阻把 IIC 总线拉成高电平。

- IIC 总线具有仲裁机制。

4、多种连接方式

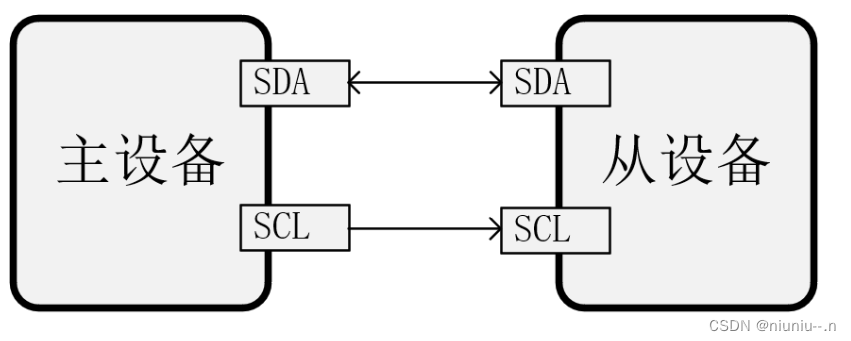

4.1 单主设备,单从设备

4.2 单主设备,多从设备

4.3 多主设备,多从设备

5、数据传输格式

① IIC 协议空闲状态 ② IIC 协议的起始信号 ③ IIC 协议的数据传输(数据读写)状态(应答信号(ACK)) ④ IIC 协议的停止信号

5.1IIC 协议空闲状态

图中标注的①②③④表示 IIC 协议的 4 个状态,分别为“总线空 闲状态”、“起始信号”、“数据读/写状态”和“停止信号”。 图中标注①表示“总线空闲状态”,在此状态下串口时钟信号 SCL 和串行数据信号 SDA 均保持高电平(都为 1),此时无 IIC 设备工作。

5.2IIC 协议的起始信号

图中标注②表示“起始信号”,在 IIC 总线处于“空闲状态”时, 时钟信号线 SCL 为高电平时,数据信号线 SDA 被拉低(由高电平变为 低电平),出现下降沿,表示产生了一个起始信号。 起始信号是由主机(本实验中为 FPGA)主动建立的,在建立该信 号之前 IIC 总线必须处于空闲状态。

5.3IIC 协议的数据传输(数据读写)状态

IIC 通讯设备的通讯模式是主从通讯模式,通讯双方有主从之分。

数据信号线 SDA 更新数据时:在时钟信号线 SCL 为低电平时将数 据信号线 SDA 上的数据进行数据更新。

即数据在时钟信号线 SCL 的上升沿到来之前就必须准备好,并在 在 SCL 下降沿到来之前必须保持稳定

5.4应答信号(ACK)

IIC 总线上的所有数据都是以字节(8bit)传送的,发送端(可以 是主机也可以是从机)每发送一个字节(8bit),就必须在第 9 个 SCL 脉冲期间释放 SDA,由接收端(发送端为主机时,接收端为从机/发 送端为从机时,接收端为主机)反馈一个应答信号。

由于上拉电阻的作用这个时候SDA默认为高电平,从机接管SDA的控制权,假如从机正确的接收了数据,会将SDA拉低,假如没有正确的接收数据,在从设备的控制下,SDA依旧为高电平,因此 应答信号为低电平(为 0)时,称为有效应答位(ACK),表示接 收端成功接收了该字节(8bit);应答信号为高电平(为 1)时,称 为非应答位(NACK),表示接收端接收该字节(8bit)失败。

注:数据接收失败或者数据传输结束都要发送 NACK。 反馈有效应答位(ACK):接收端在第 9 个时钟脉冲之前的低电平期 间将 SDA 拉低,并且确保在该时钟周期的高电平期间保持低电平。

5.5IIC 协议的停止信号

数据读写完成后,时钟信号线 SCL 为高电平时,数据信号线 SDA 被释放(由低电平转为高电平),出现上升沿,表示产生了一个停止 信号,IIC 总线跳转回“总线空闲状态”。 停止信号是由主机(本实验中为 FPGA)主动建立的,建立该信号 之后,IIC 总线将返回空闲状态。

6、I2C可配置变量

6.1 传输模式

- 标准模式(Standard):100kbps

- 快速模式(Fast):400kbps

- 快速模式+(Fast-Plus):1Mbps

- 高速模式(High-speed):3.4Mbps

- 超快模式(Ultra-Fast):5Mbps(单向传输)

提起不同速度的传输模式,读者首先想到的可能是指SCK的频率,这没有错,但是绝不仅限于此,为了获得更高的传输速率,除开芯片设计工程师外,电路的设计人员需要认真思考诸如“负载电容,上拉电阻的大小”等更偏向于电路设计或模拟设计的内容。

6.2 地址位宽

- 标准I2C:七位寻址

- 扩展I2C:十位寻址

每个主设备或者从设备都能对应一个唯一的地址,大多数情况下,7位的地址,已经够用了。但是也可以对其进行扩展,转变为10位地址,多出来的3位地址相当于提供了8倍潜在设备数量,同时,按照NXP2021版的I2C协议规定,10位地址的从设备,和7位地址的从设备,都可以挂在一个总线上,彼此相互兼容。

6.3 设备地址

每个主设备与从设备需要设置互不相同的七位地址或十位地址。

7、I2C的仲裁机制

7.1 SCL同步问题

总线天生带线与逻辑,即总线的几个输入端,任意有一个拉低,总线表现为低电平,全部位高电平时,总线才是高电平,真值表如下所示。

| 设备A | 设备B | 总线逻辑 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

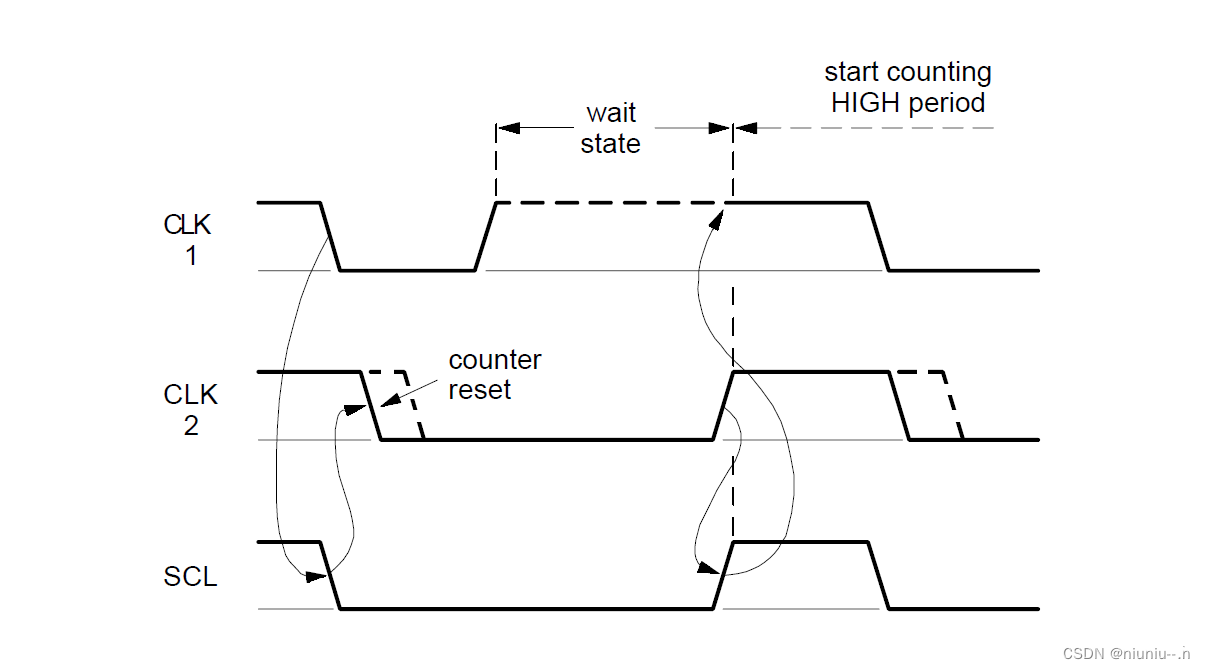

假设有两个主设备都想拉低SCL信号,Master1先拉低 ,Master2后拉低,那么SCL会按照CLK1的时间来拉低自身(线与逻辑的应用),而假如Master1先拉高,Master2后拉高,SCL又会按照CLK2的时间来拉高自身。

因此:当多个节点同时发送时钟信号时,在总线上表现的是统一的时钟信号。这就是SCL的同步原理

7.2 SDA仲裁问题

设想一种多主设备,多从设备的情况

假如在空闲状态时,两个主设备先后想要操控I2C总线(相隔时间很短),I2C岂不是会发生错误(数据紊乱等),如何解决这个问题呢?

我们可以采取仲裁机制,同样应用到总线的线与逻辑,在箭头所指的位置,SCL上升沿到来,对SDA上的数据进行采样,结果为0,与DATA2上的数据0相同,与DATA1上的数据1不同,通过这种比较 Master1退出了对总线的控制,而Master2所发送的数据都是正确的,完成仲裁。

3093

3093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?