1.为什么要进行时序约束

进行时序约束是为了确保设计的电路能够在特定的时钟频率下正常工作。如果不进行时序约束,可能会导致以下问题:

-

时序违规:没有进行时序约束可能会导致电路在实际运行时无法满足时序要求,例如在时钟边沿到来之前数据信号就发生了变化,或者电路在时钟周期内无法完成操作。这可能导致电路的功能错误或不可靠。

-

性能下降:没有进行时序约束可能会导致电路的性能下降。时序约束可以帮助综合工具和布局工具进行优化,以最大限度地提高电路的工作速度和吞吐量。如果没有约束,综合工具和布局工具可能无法充分利用电路的潜力,导致性能下降。

-

设计错误:没有进行时序约束可能会导致设计错误的隐藏。时序约束可以帮助设计人员发现潜在的设计错误,例如信号路径过长、时钟域切换问题等。通过约束路径和时钟域,设计人员可以更好地理解和验证电路的行为,从而减少设计错误的可能性。

首先看一下未进行时序约束:

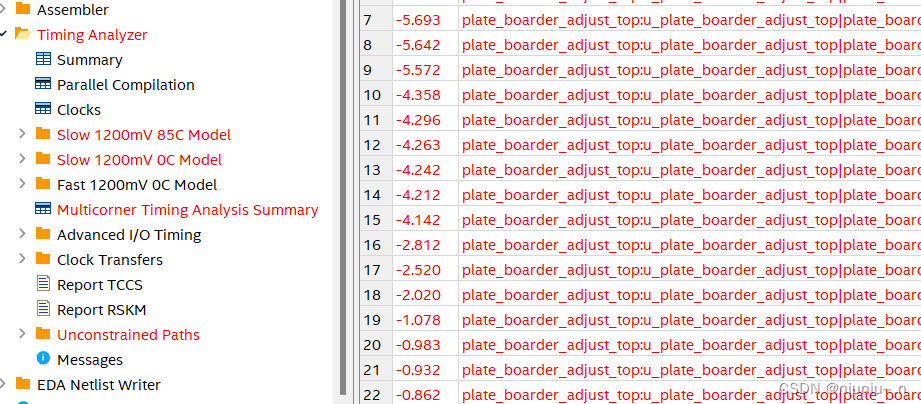

由上图可看出,在没有进行时序约束的时候,工作频率只有50mhz。

2.如何如何计算Fmax值:

名称介绍:

说明(图未截全,可对照软件)

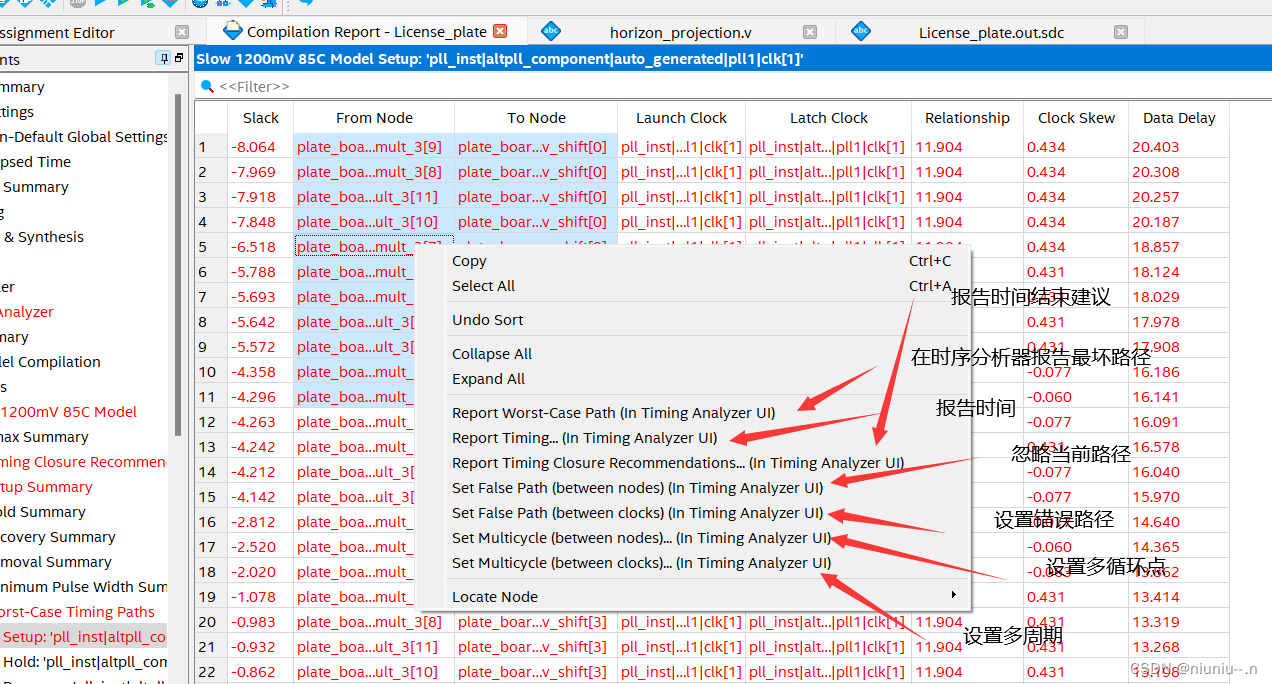

Slack:建立或保持时间余量。

From Node:起点,源寄存器。

To Node: 终点,目标寄存器。

Launch Clock: 源寄存器发射数据的时钟

Latch Clock: 目的寄存器接收数据的时钟

Relationship:Launch Clock edge和 Latch Clock edge 的时间差。

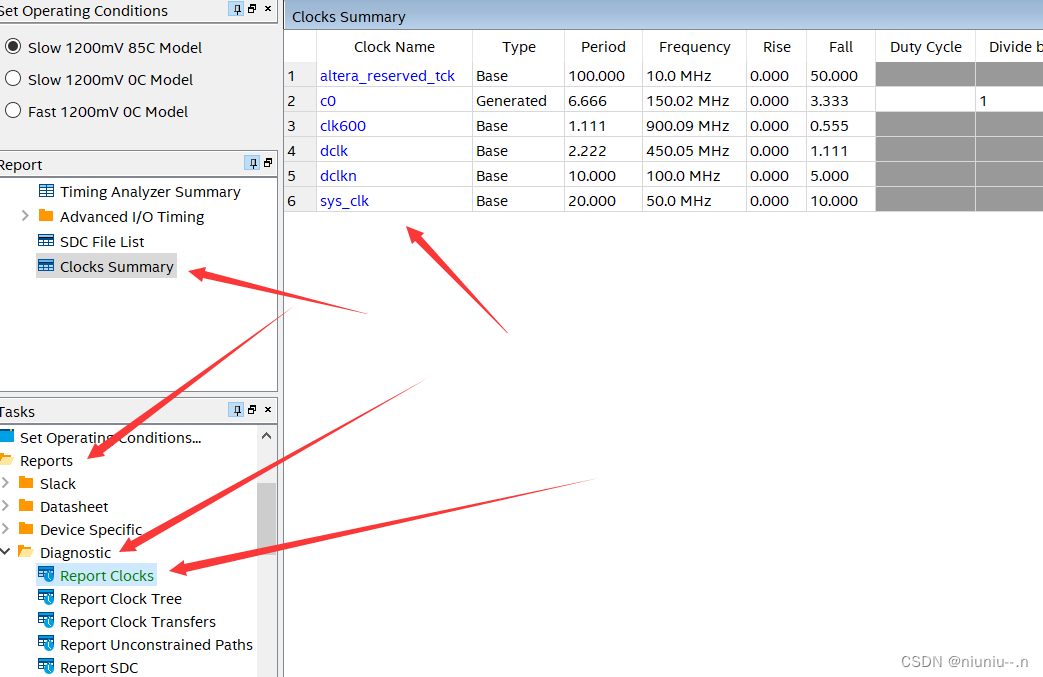

3.时序约束

不讲理论,只介绍如何用quartus进行约束。

1.进入界面

在菜单栏依次点击:Tools->TimeQuest Timing Analyzer或者直接点击 下面这个图标也可

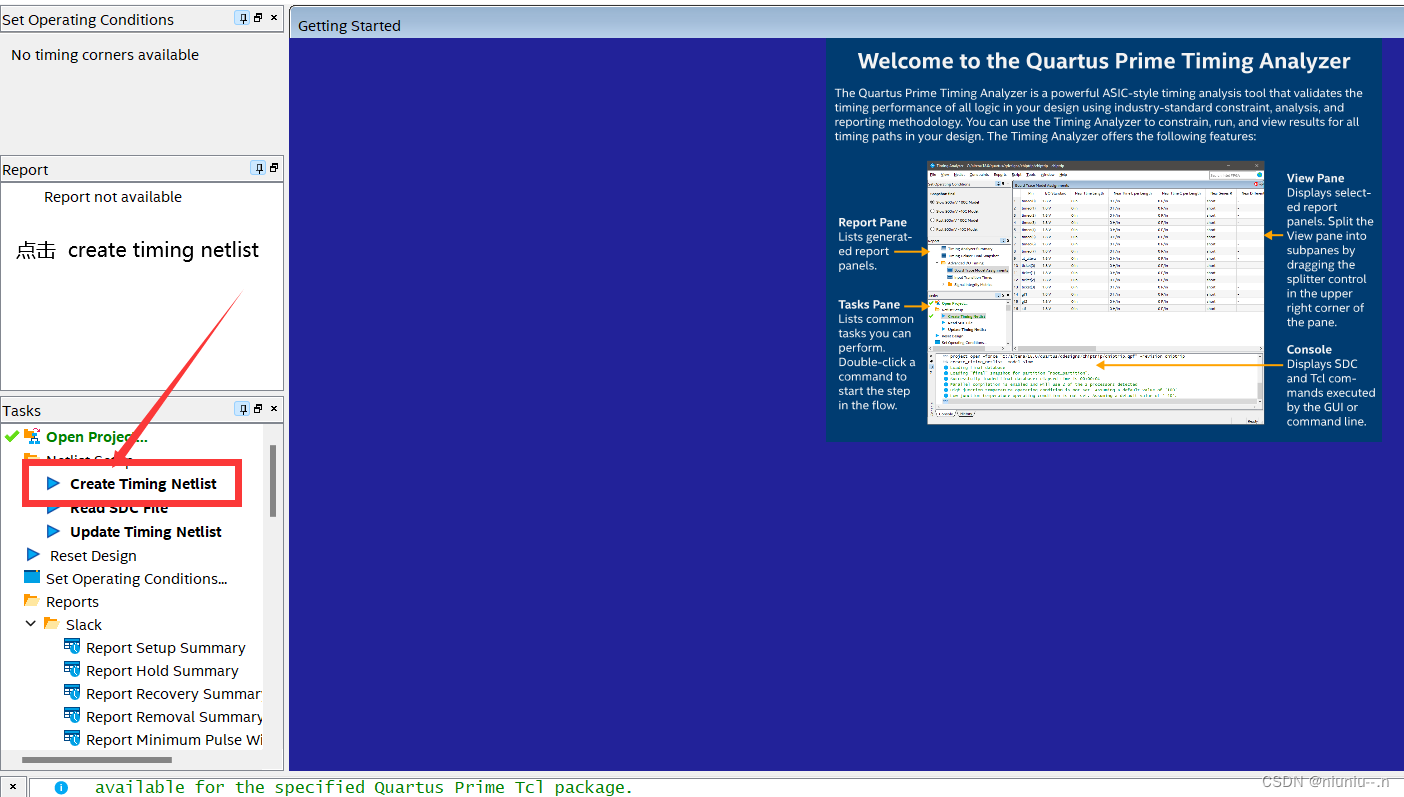

2.创建网表

约束的对象就是网表,网表就是 Quartus 软件经过编译,布局布线后得到的实际电路信息,该电路信息就是对应下载到芯片中后实际在芯片中呈现的电路。直接双击 Create Timing Netlist 选项就可以创建网表。

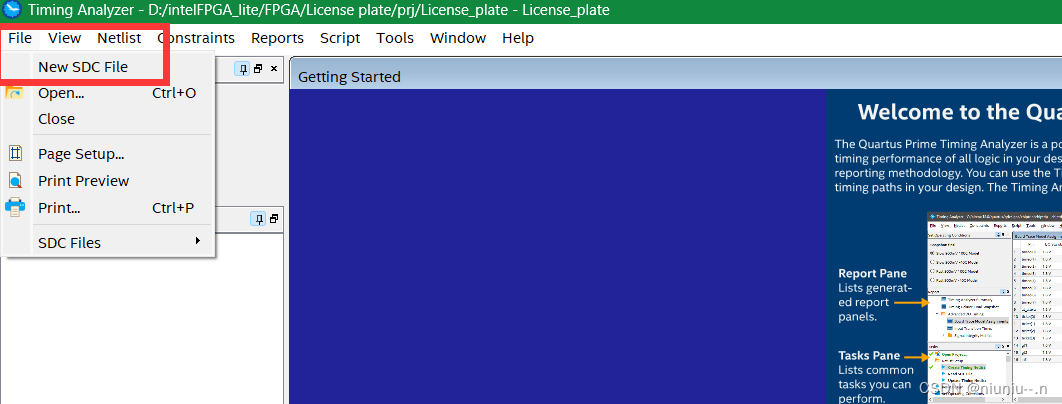

3.读取SDC文件

sdc文件就是时序约束文件,依次点击file-new sdc file即可,sdc文件一般创建在工程文件夹下。

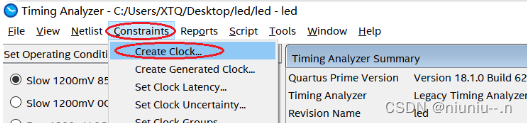

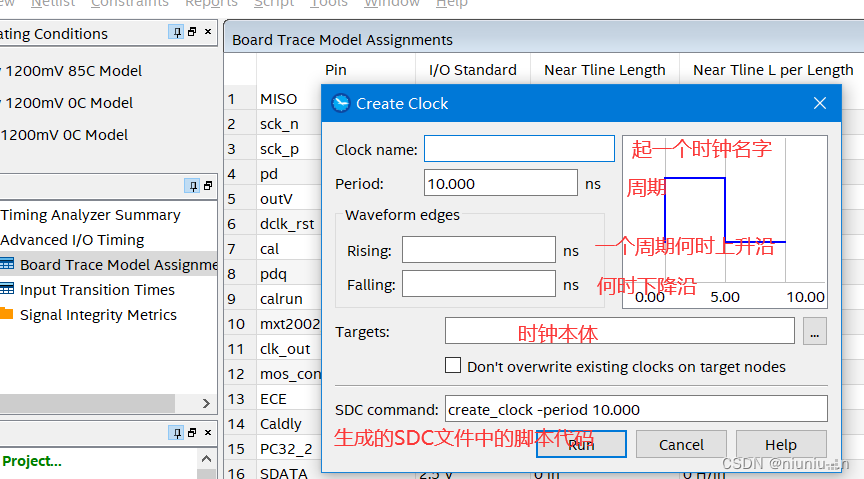

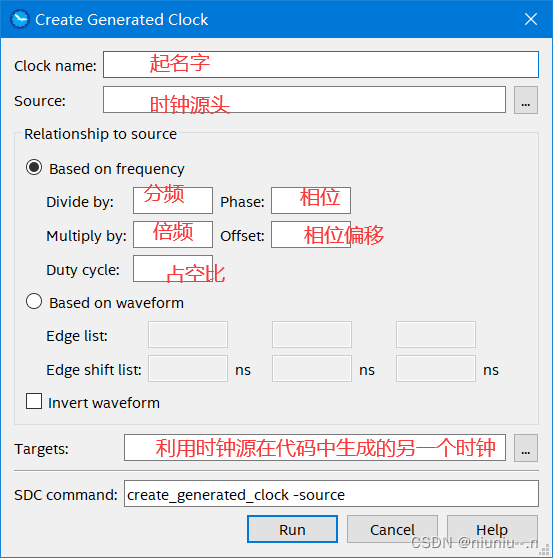

4.创建时钟(Create Clock)

创建时钟约束,就是为当前网表模型指定一个明确的时钟信号。这样时序分析软件就能够基于该时钟参数。

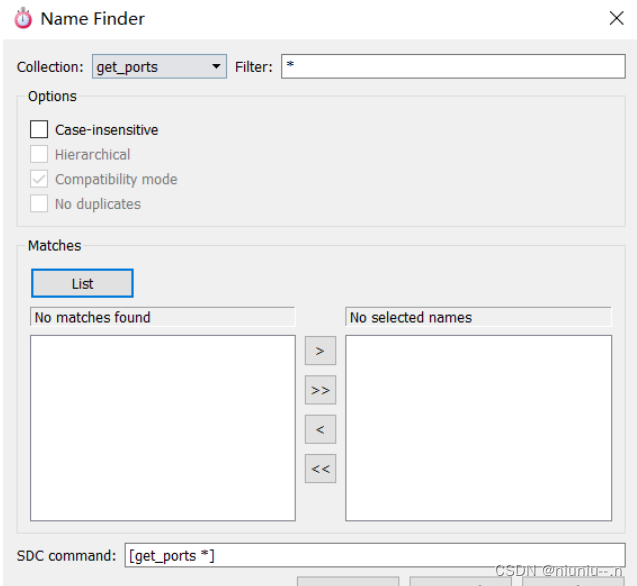

在这个界面筛选时钟以及选择时钟本体,*号表示列举所有此类型信号,可直接输入信号名称

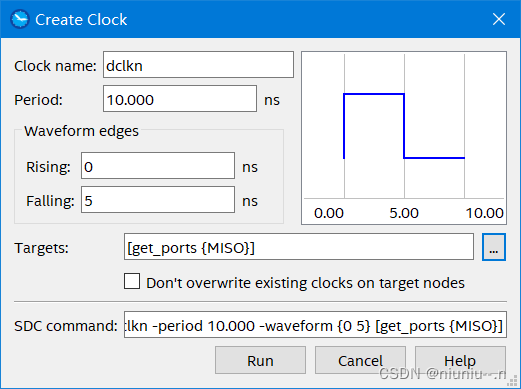

将代码中的 MISO信号重命名为dclkn进行约束,占空比为50%,周期是10ns。(上升沿和下降沿不填默认是50%占空比)

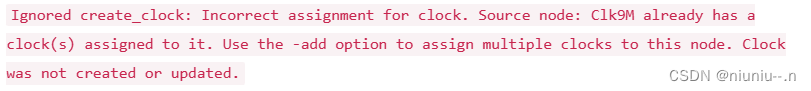

5.约束忽略

如果出现下列状况,就是被忽略了,这时系统默认约束过了那么就不能创建了,只能更改

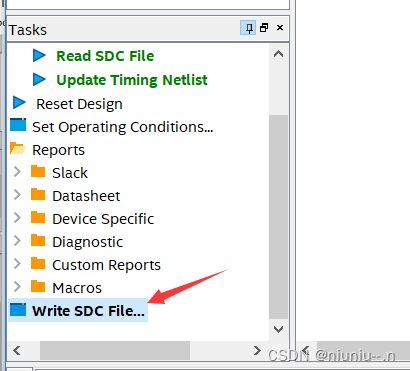

6.写入SDC文件

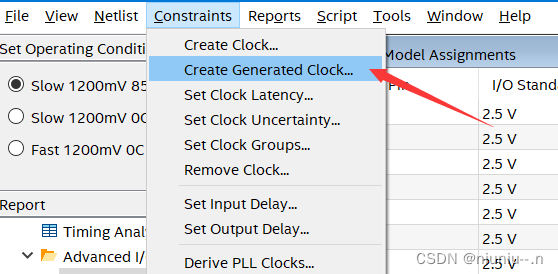

7.其他约束

-

Creat clock 约束外部进入FPGA的时钟,其他IC产生的给FPGA的类时钟信号

-

约束pLL(derive_pll_clocks)

-

时钟多路复用器(clock muxes)

-

涟漪时钟(ripple clocks),FPGA内部寄存器输出的时钟

phase:是偏移多少度

offset:是偏移多少ns

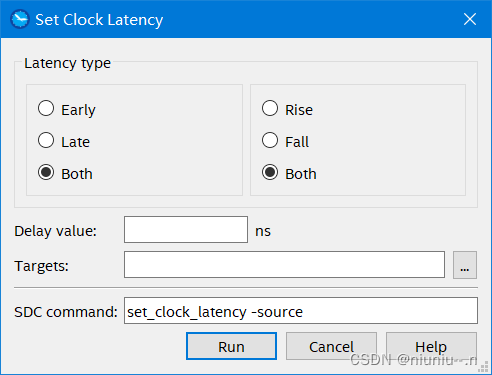

set_clock_latency:对输入到FPGA的时钟及类时钟(其他芯片产生的时钟给FPGA)

late指最大时钟延迟,early指最小时钟延迟

对时钟出现的抖动进行约束,是一个时钟到另一个时钟的约束,用 derive_clock_uncertainty约束命令不需要确定uncertainy的时间

-

Set_clock_groups

把相关的时钟分成一个组,与其它不相关的时钟区分开。 timequest只对这组内的时钟域进行分析,组间的时钟路径将不会分析。 -

set_input_delay

对外部IC输入到FPGA管脚的约束,这个约束命令中的延迟信息需要告诉timequest。

-

set_output_delay

FPGA输出到IC的延迟,与输入延迟相似 -

set false path

不要分析某个路径或某组路径 -

set_multicycle_path

两个寄存器间的数据传输在一个周期内没法完成时,我们可以通过该约束命令来改变他的建立关系值和保持关系值让其满足时序要求。

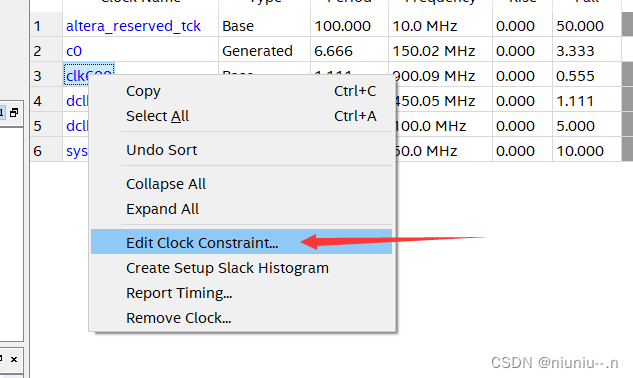

8.快捷方式

在外面设置的快捷方式(右键即可)。

4.约束结果

1.时序满足

通过建立时间,保持时间等观察,已经满足时序。

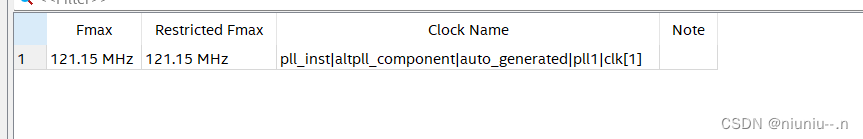

2.进行时序约束后工作频率增加2倍以上

跟最开始没有进行时序约束的时候对比,工作频率上升了接近两倍有余。

3502

3502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?