需求说明:Lattice系统FPGA入门

内容 :FPGA接口模块SerDes讲解

来自 :时间的诗

网站:http://blog.sina.com.cn/s/blog_aec06aac01013m5z.html

2.3接收端均衡器( Rx Equalizer)

2.3.1 线形均衡器(Linear Equalizer)

www.blog.sina.com.cn/fpgatalk

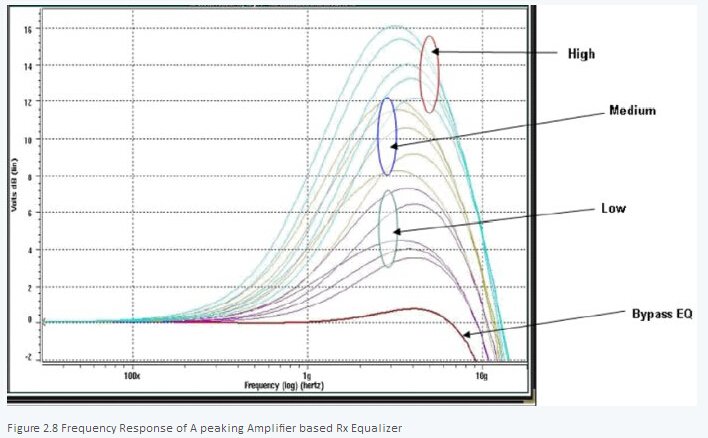

接收端均衡器的目标和发送均衡器是一致的。对于低速(<5Gbps)SerDes,通常采用连续时间域,线性均衡器实现如尖峰放大器(peaking amplifier), 均衡器对高频分量的增益大于对低频分量的增益。图2.8为一个线性均衡器的频域特性。通常工厂会对均衡特性封装为数种级别,可以动态设置,以适应不同的信道特性,如High/Med/Low等。

Figure 2.8 Frequency Response of A peaking Amplifier based Rx Equalizer

2.3.2 DFE均衡器(Decision Feedback Equalizer)

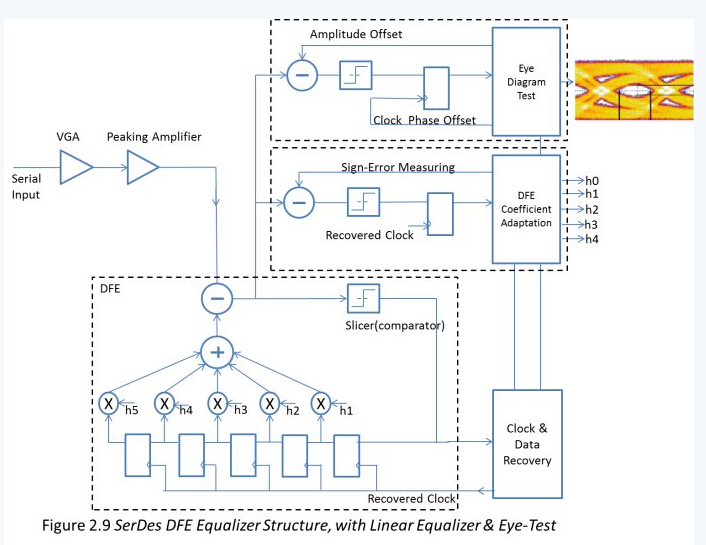

对于高速(>5Gbps)SerDes,由于信号的抖动(如ISI相关的确定性抖动)可能会超过或接近一个符号间隔(UI, Unit Interval), 单单使用线性均衡器不再适用。线性均衡器对噪声和信号一起放大,并没有改善SNR或者说BER。对于高速SerDes,采用一种称作DFE (Decision Feedback Equalizer)的非线性均衡器。DFE通过跟踪过去多个UI的数据(history bits)来预测当前bit的采样门限。DFE只对信号放大,不对噪声放大,可以有效改善SNR。

图2.9演示了一个典型的5阶DFE。接收的串行数据由比较器(slicer)来判决0或者1,然后数据流由一个滤波器来预测码间干扰(ISI),再从输入的原始信号中减掉码间干扰(ISI),从而的到一个干净的信号。为了让DFE均衡器的电路工作在电路线形范围内,串行信号先经过VGA自动控制进入DFE的信号幅度。

为了理解DFE的工作原理,先来看一个10Gbps<

本文介绍了Lattice FPGA中SerDes接口的接收均衡器,包括线性均衡器和DFE均衡器,强调了它们在高速数据传输中的重要性。同时,详细阐述了时钟数据恢复(CDR)的概念,探讨了CDR的结构、工作原理及其在不同应用场景下的选择。

本文介绍了Lattice FPGA中SerDes接口的接收均衡器,包括线性均衡器和DFE均衡器,强调了它们在高速数据传输中的重要性。同时,详细阐述了时钟数据恢复(CDR)的概念,探讨了CDR的结构、工作原理及其在不同应用场景下的选择。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?