HexagonDSP的内存操作

概述

Hexagon处理器配备了load/store架构,数值与逻辑计算均在寄存器上进行操作。清晰定义的load指令可将内存中的操作数存放于寄存器中,store指令可将寄存器中的操作数存放于内存中。有一部分指令(mem-ops)可直接在内存上进行数值与逻辑操作。

地址空间已封装,所有的访问都以线性地址空间为目标,可访问的值可以是指令或者数据。

内存模型

本章介绍Hexagon处理器的内存模型

地址空间

Hexagon处理器拥有一个32位的字节可寻址内存地址空间。整个4G的线性地址空间可由用户指定。同时Hexagon处理器还提供虚拟内存机制。

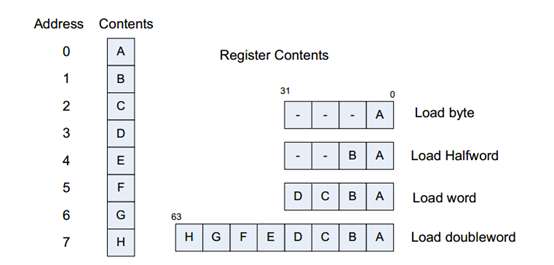

字节序列

Hexagon处理器属于小端机器:内存中的低位地址在寄存器中的最低位,如下图所示:

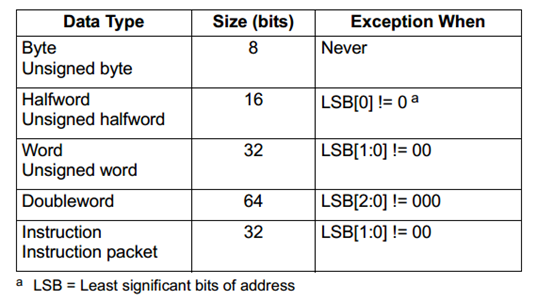

对齐

Hexagon处理器虽然能够进行字节地址的编程,指令以及数据在内存中必须被对齐到特定的地址边界

指令与指令包必须是32位对齐

数据必须对齐至本地访问大小

未对其的指令访问将会导致内存对齐异常

置换内存指令在应用中用来应用未对其的向量数据。Load与store指令仍然是内存对齐的;然而置换指令可以使数据更加轻松地重新安排寄存器

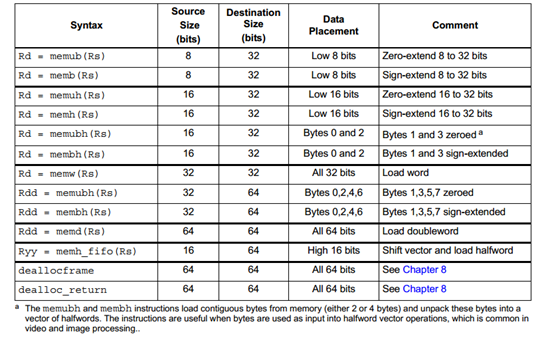

内存的Load指令

内存可以以字节,半字或双字尺寸来导入。数据类型支持有符号与无符号型数据。语法类型为 ,XX用来表示数据类型:

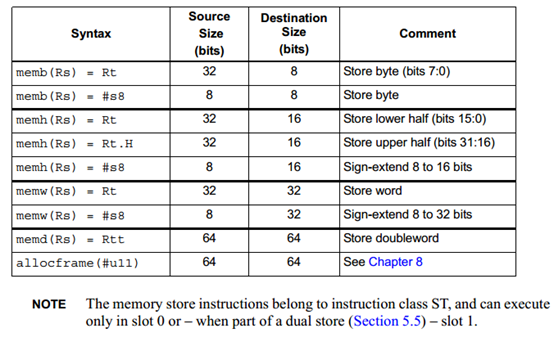

内存stores

内存可以以字节,半字,字或双字尺寸存储。语法运用类似于 ,X意味着数据的类型。下图总结了可支持的store指令:

双存储

两个存储指令可以出现在同一个指令包中。这种指令被称作双存储

{

memw(

本文介绍了HexagonDSP的内存模型,包括32位字节寻址内存地址空间、小端机器字节序、对齐要求以及load/store指令。此外,还讨论了内存的load与store、双存储、新值存储、mem-ops、寻址模式、有条件的操作以及内存缓存机制。Hexagon处理器支持原子操作如LL/SC,用于同步和互斥。

本文介绍了HexagonDSP的内存模型,包括32位字节寻址内存地址空间、小端机器字节序、对齐要求以及load/store指令。此外,还讨论了内存的load与store、双存储、新值存储、mem-ops、寻址模式、有条件的操作以及内存缓存机制。Hexagon处理器支持原子操作如LL/SC,用于同步和互斥。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1307

1307

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?