一、介绍

FPGA逻辑仿真搭建工程编译是一个耗时而麻烦的事情,这里有个工具可以实现一键秒编译仿真,最大限度的缩短编译和仿真的时间

vscode是一个很友好的代码编辑器,因为有代码补全的功能,很大程度的节约写代码的时间

iverilog是一个开源的工具,支持windows和linux平台,命令行操作编译仿真

二、环境安装

1、安装vscode

下载

https://vscode.en.softonic.com/

安装

一直默认就行

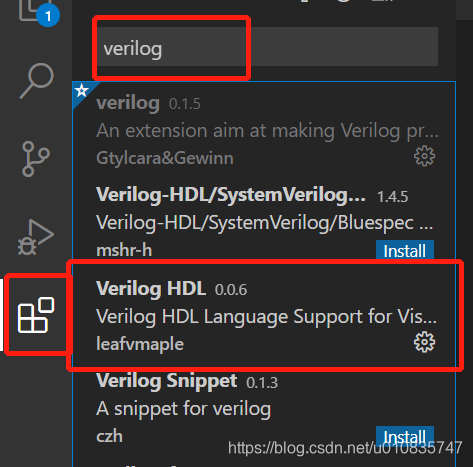

安装verilog支持包

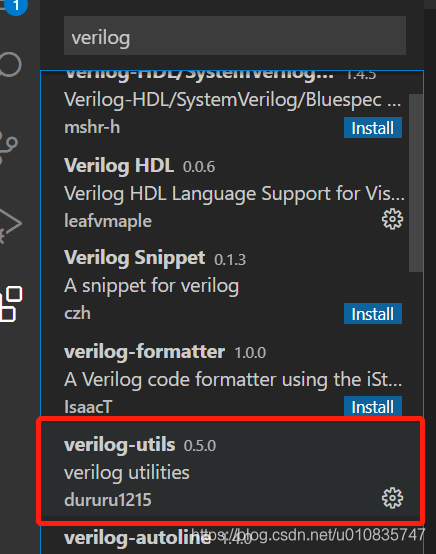

自动例化支持包

支持vscode部分安装完成

2、安装iverilog+GTKWave

下载

链接:https://pan.baidu.com/s/1UjjR9WXM_a3qIroy_06_aQ

提取码:4q2f

两个包是一起的

一键安装就行

注意:要把环境变量添加勾上

三、使用

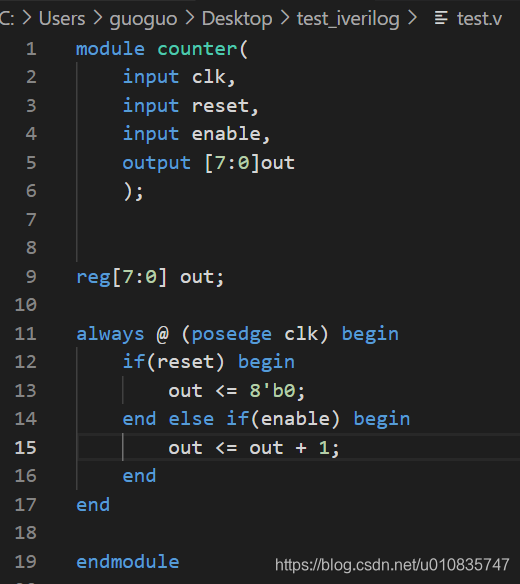

1、编写test.v

module counter(

input clk,

input reset,

input enable,

output [7:0]out

);

reg[7:0] out;

always @ (posedge clk) begin

if(reset) begin

out <= 8'b0;

end else if(enable) begin

out <= out + 1;

end

end

endmodule

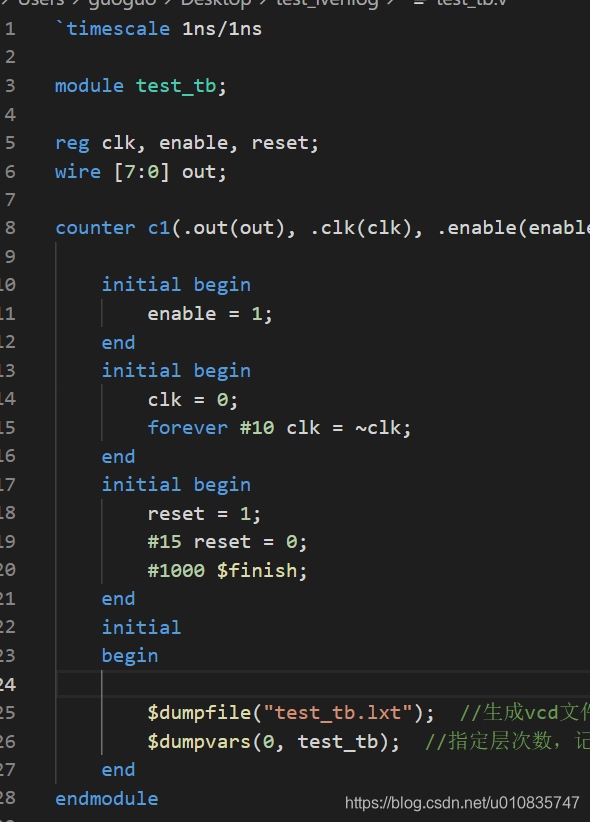

2、编写testbench,test_tb.v

`timescale 1ns/1ns

module test_tb;

reg clk, enable, reset;

wire [7:0] out;

counter c1(.out(out), .clk(clk), .enable(enable), .reset(reset));

initial begin

enable = 1;

end

initial begin

clk = 0;

forever #10 clk = ~clk;

end

initial begin

reset = 1;

#15 reset = 0;

#1000 $finish;

end

initial

begin

$dumpfile("test_tb.lxt"); //生成lxt文件,记录仿真信息

$dumpvars(0, test_tb); //指定层次数,记录信号

end

endmodule

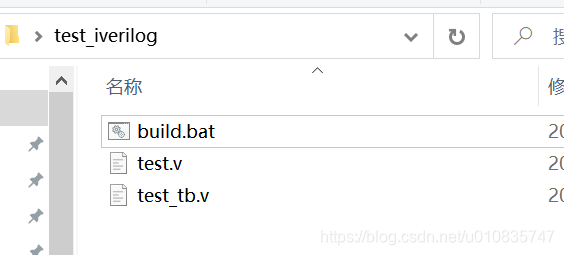

3、编写编译脚本build.bat

iverilog -o tb *v

vvp -n tb -lxt2

gtkwave test_tb.lxt

iverilog -tvhdl -o test.vhd test.v

pause

这个脚本是通用的,以后直接复制过去就行,不用重复编写

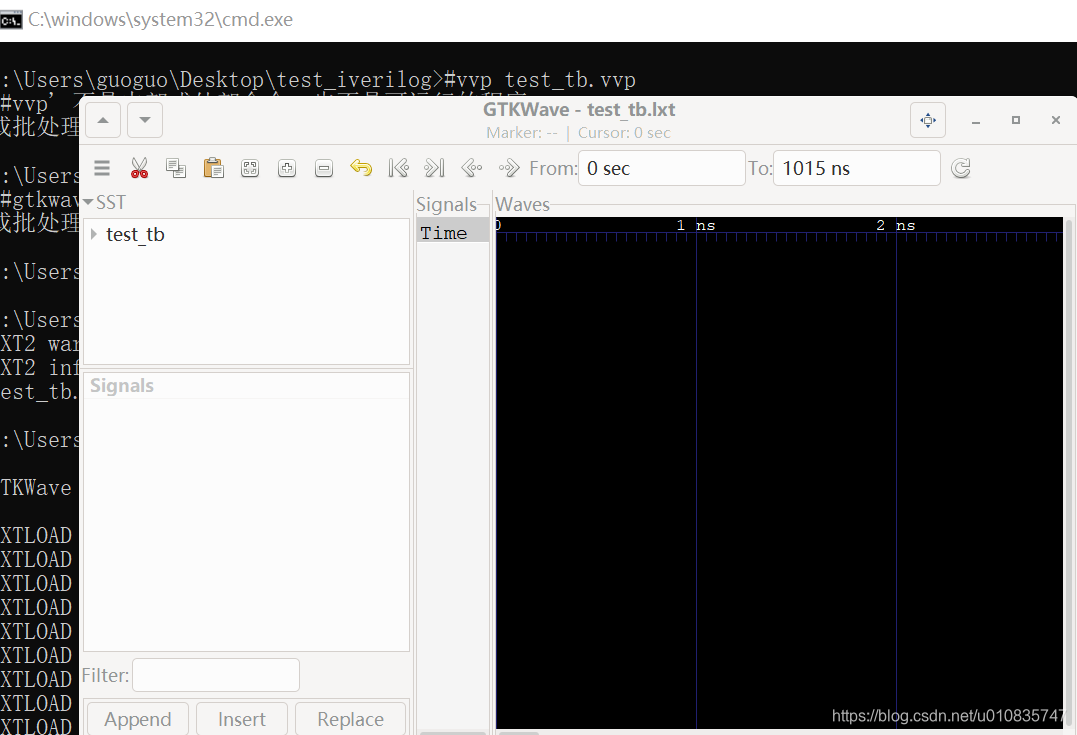

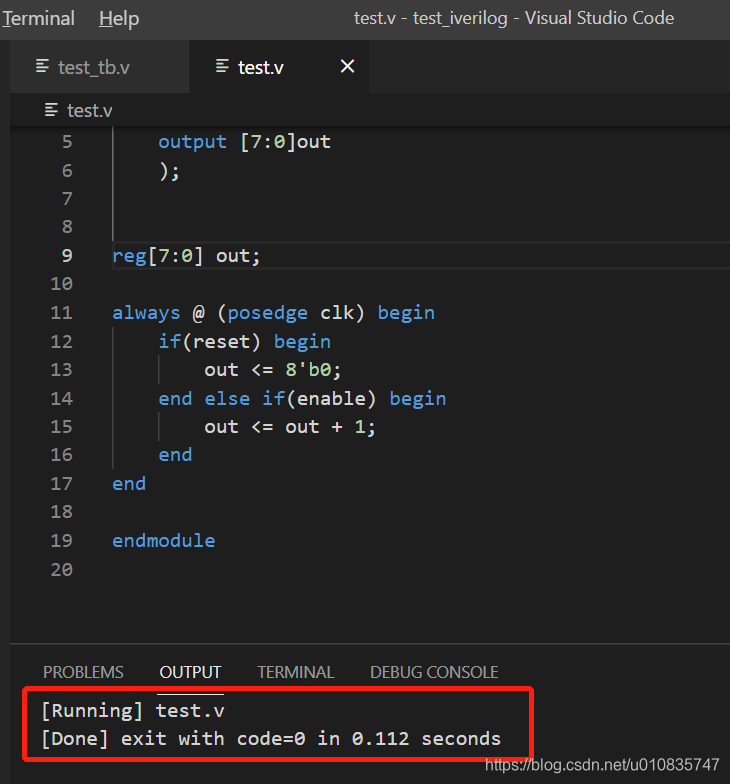

4、编译仿真

双击build.sh

编译+进入仿真界面不过秒级的时间

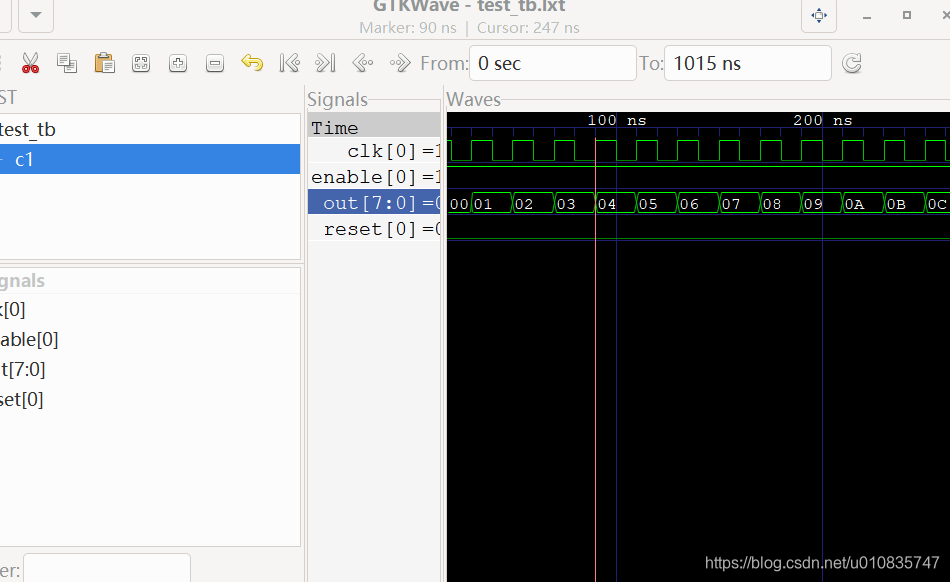

结果

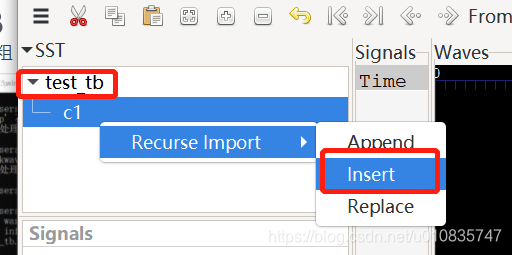

添加波形

按住ctrl滚动鼠标可以放大缩小

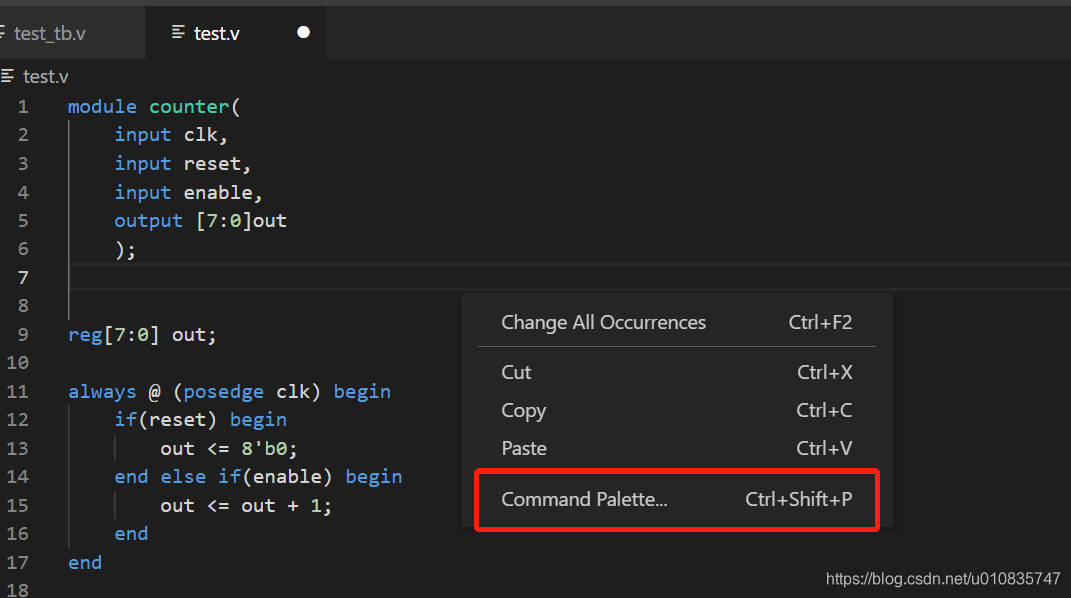

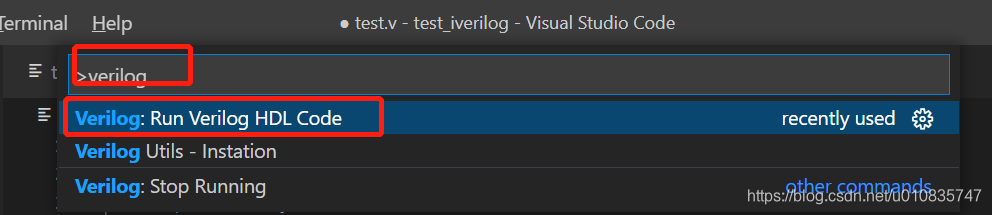

5、语法错误检查

右键点击要检查的文件

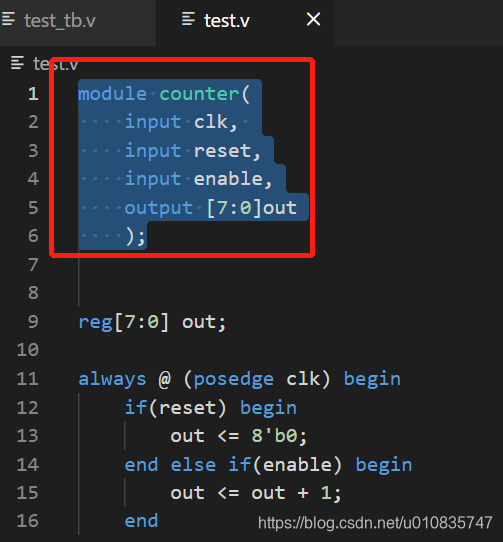

6、自动例化

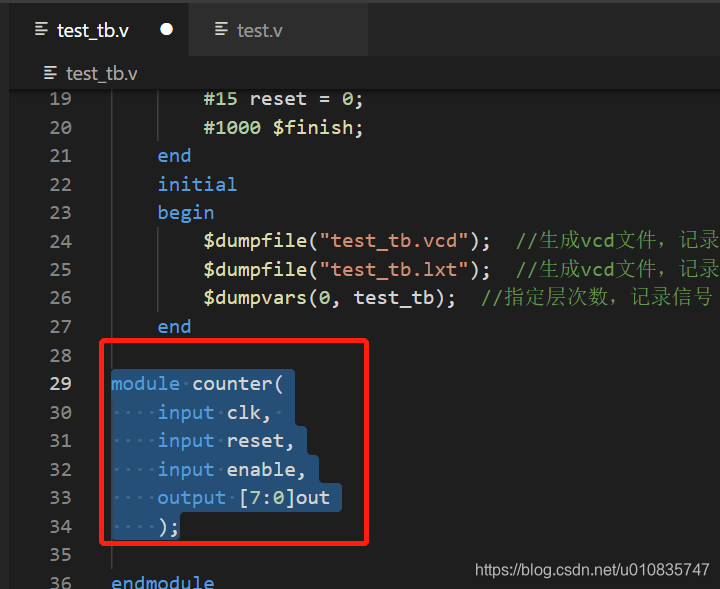

复制需要例化的模块

粘贴到要例化的地方

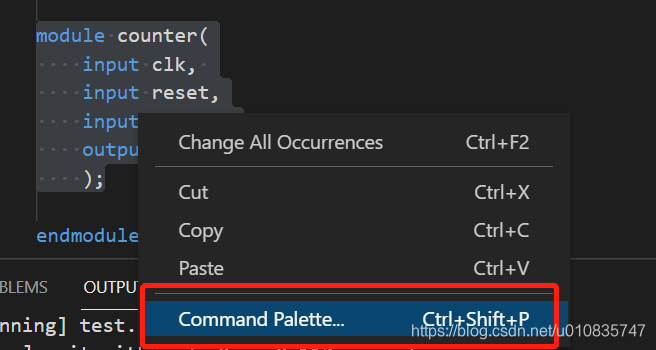

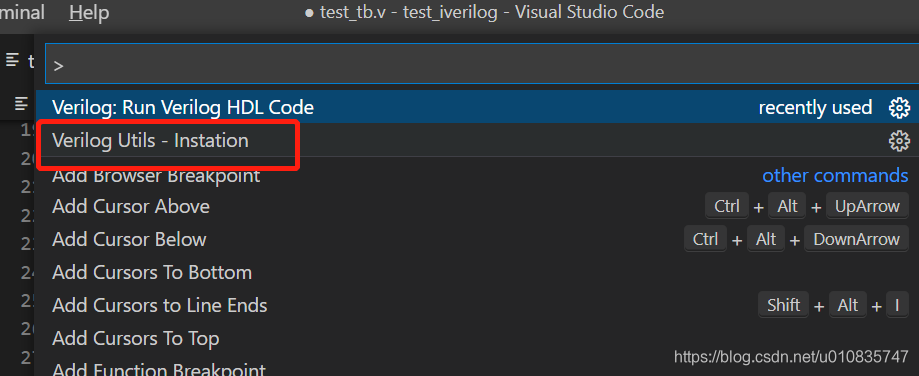

右键选择命令

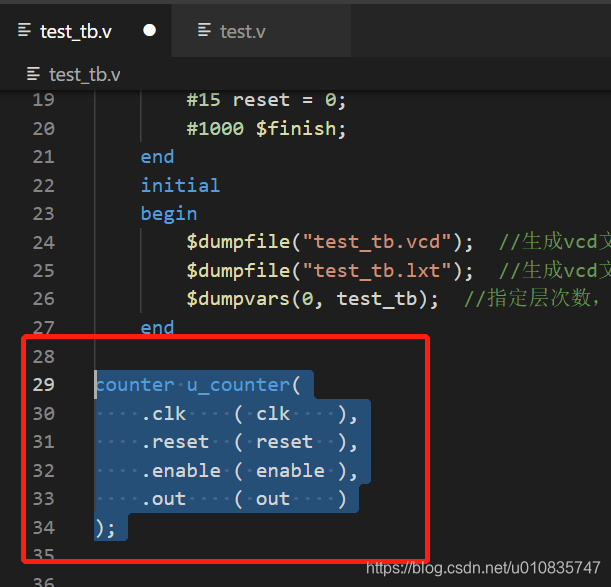

然后看到就自动例化好了

877

877

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?