2、rocket-riscv

3、optimsoc (openrisc)

4、西部数据开源riscv

https://github.com/chipsalliance/Cores-SweRV

西数SweRV是一种32位顺序执行架构,双路超标量设计,9级流水线,支持SMT同步多线程

第一个版本Swe Core EH1采用台积电28nm工艺制造,运行频率高达1.8GHz,模拟性能可达4.9 CoreMark/MHz,略高于ARM A15。

SweRV Core EH2基本架构不变,工艺升级为台积电16nm FinFET造,以获得性能、功耗、面积的最佳平衡,模拟性能提升29%达到6.3 CoreMark/MHz,内核面积缩小39%仅为0.067平方毫米。

https://news.mydrivers.com/1/662/662375.htm

5、openpiton

6、opensparct1

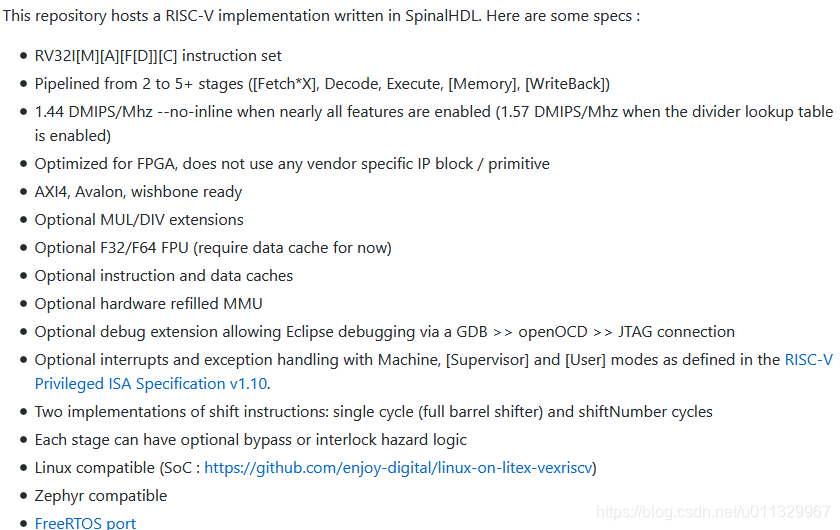

7、VexRiscv

https://github.com/SpinalHDL/VexRiscv

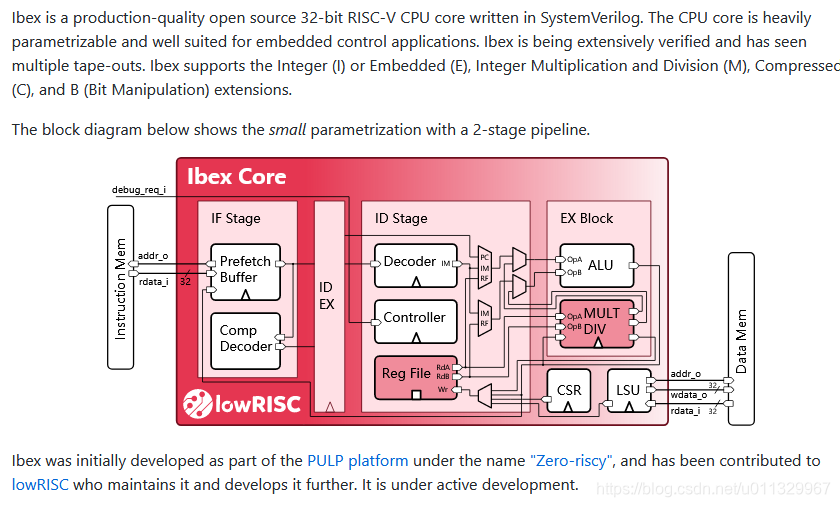

8、Ibex RISC-V Core

https://github.com/lowRISC/ibex

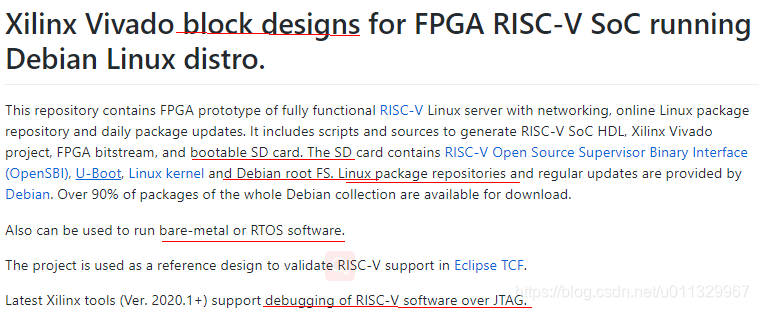

9,vivado risc-v (基于rocket-chip)

https://github.com/eugene-tarassov/vivado-risc-v

10、香山

中科院大学教授、中科院计算所研究员包云岗公布了国产开源高性能RISC-V处理器核心——香山。

https://mp.weixin.qq.com/s/9JTeaZr-PAaVTXjGanso3w

11,openpiton

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?