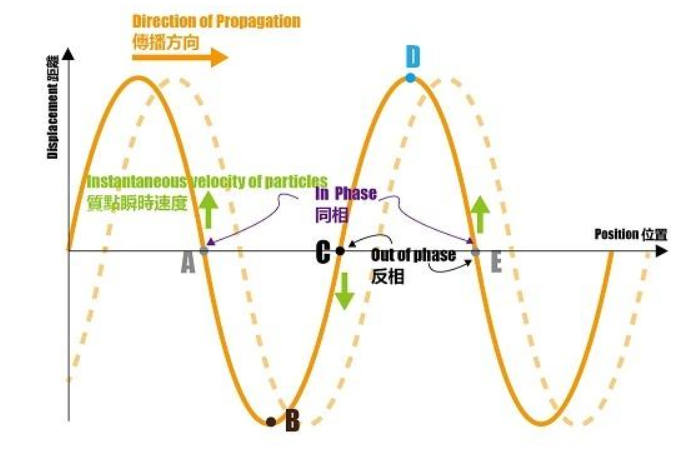

相位是对于一个波,特定的时刻在它循环中的位置:一种它是否在波峰、波谷或它们之间的某点的标度。相位描述信号波形变化的度量,通常以度 (角度)作为单位,也称作相角。 当信号波形以周期的方式变化,波形循环一周即为360° 。

简谐运动中的相位差

如果两个简谐运动的频率相等,其初相位分别是φ1,φ2。当φ2>φ1时,他们的相位差是△φ=(ωt+φ2)-(ωt+φ1)=φ2-φ1,此时我们常说2的相位比1超前△φ。

如果没有相位噪声,那么振荡器的整个功率都应集中在频率f=fo处。但相位噪声的出现将振荡器的一部分功率扩展到相邻的频率中去,产生了边带。在离中心频率一定合理距离的偏移频率处,边带功率滚降到1/fm,fm是该频率偏离中心频率的差值。

1 相位在哪里?

百度百科的“相位”释义归类电学和工程学。但实际上相位概念应该包含在生活的方方面面,信息光学、波动光学、计算成像、电磁学、电力学、声学、信号处理、图像处理、雷达信号处理,以及物理学中的简谐振动、阻尼振动、受迫振动等等都有涉及。

在简谐运动中,相位表示振动物体当前的状态或位置。它告诉振动物体相对于振动的起始点在何处。

在交流电中,电压和电流是随时间变化的,它们可以用正弦函数表示。相位则用来描述这些正弦函数的起始位置。相位的单位可以是弧度、角度、径向频率或周期。

2 相位是什么?

相位是描述波动或振动的性质的量。它表示在给定时间点上,波动或振动的状态相对于某个参考点的偏移量或位置。

3 光学中的“相位”

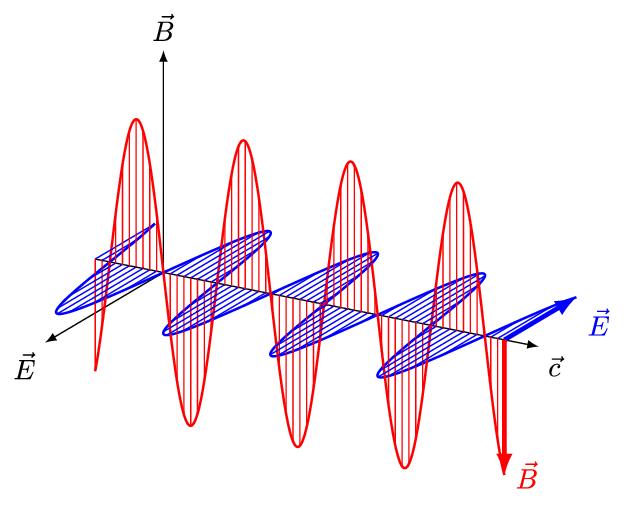

(1) 正如我们所知,光是一种电磁波。可以将光波看作是在空间中传播的电磁波,其相位表示了电场或磁场的振动状态。电场矢量和磁场矢量,相位一致,传播速率相同,同频传输。需要知道的是我们人眼感光,主要是电矢量的功劳。

(2) 第二个和相位的应当是O光和E光,这两种光是人为定义的,相位相差pi/2的特殊偏振光,实际上使用双折射率晶体可以获得偏振态垂直的两种线偏振光即为O光和E光。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?