摘要

设计工艺协同优化 (DTCO) 是同时优化设计和工艺以提高性能、能效、芯片利用率和制造成本/良率的过程。由于 7nm 节点以外的物理限制导致器件缩放速度减慢,DTCO 成为在先进工艺节点中继续进行晶体管密度缩放的重要使能方法。通过 DTCO,我们能够使用模块级 PPA(性能、功耗、面积)分析来评估技术、设计规则和单元架构,这极大地帮助半导体晶圆厂通过大量的架构创新来降低成本并缩短上市时间。

DTCO 要评估的参数包括设计规则(例如,栅极多晶间距 gate poly pitch、M1 间距 M1 pitch、侧到顶间距规则side-to-top spacing rule、过孔外壳规则via-enclosure rule)、单元架构(例如,单排single-row或多行multi-row高度、2D 或 1D M1、金属方向的偏好)和工艺(例如,Fin-FET、Nanosheet-FET、ComplementaryFET),这些参数统称为 DTCO 参数。

一个完整的 DTCO 应该扮演两个角色:(1) 分析 DTCO 参数以全面了解 DTCO 参数如何相互作用并影响设计实施,以及 (2) 优化 DTCO 参数以确定 DTCO 参数值的最佳组合,从而产生具有最佳 PPA 的设计实施。为了提高效率,基于 ML (机器学习) 的建模对于 DTCO 参数分析和优化至关重要。

DTCO 有效性的证据可以在工业界 [1] 和学术界 [2] 中找到,其中台积电应用 DTCO 将 HPC(Arm 处理器)在 N3 节点上的时钟频率提高了 9%,而功率预算没有增加 [1],而 IMEC 在 2019 年声称,随着工艺节点的进步,DTCO 和 STCO(系统技术协同优化)将显着提高芯片性能 [2]。(在 EDA 上下文中,完整的 DTCO 参数探索过程的示例可以在 [3] 中找到。

物理设计挑战

在EDA视角,特别是物理设计,对 DTCO 使能的相关问题研究正在进行中,而一些问题仍然没有进展。其中,两个基本问题是 (1) 自动生成单元布局和 (2) 对新工艺技术进行快速准确的标准单元和物理设计评估,在下文中,我们将更精确地描述这两个主题。

标准单元综合

由于设计团队通过使用原始逻辑门/块的标准单元来生成设计实现,这些单元应遵循流程团队提供的 DTCO 参数值输入集,因此在单元面积、延迟、功耗和引脚连接性pin access方面生成高质量的标准单元非常重要。

SP&R [4] 是单元综合的创新工作之一,它试图通过将它们公式化为 SMT(满足性模理论)问题实例来同时解决晶体管布局和单元内布线来产生最佳布局。但是,由于它相当缓慢,因此需要进行深入的研究调查。随着 cell 上 pin 密度的增加,提高 pin access是一个热门问题,这会导致芯片布线中 routing 违例的数量大幅增加。一种补救措施是在 MOL(线中)层中使用称为 LISD 和 LIG(a.w.a. CA 和 CB)的局部导线。此外,对于大细胞,细胞的形状往往是多样化的;一个单元格可以采用多行高或单行高的形式,甚至可以采用 6 轨高或 8 轨高等形式。这种单元形状多样化,包括 MBFF(多位触发器)单元的形状多样化,为提高芯片电源效率和性能提供了很大的潜力。(可以参考与 MBFF 相关的 DTCO 倡议工作 [5]。然而,从物理设计的角度来看,由于单元高度的混合使用,放置合法化要复杂得多。此外,合成多行高度的单元非常具有挑战性,因为晶体管放置问题的 1D 晶体管封装变成了 2D 封装问题。(一项倡议工作可以在 [6] 中找到。最后,由于金属和栅极策略间距之间的缩放差异,有必要进一步阐述布线友好的单元引脚模式生成以及物理设计中的网络布线。

新技术评估

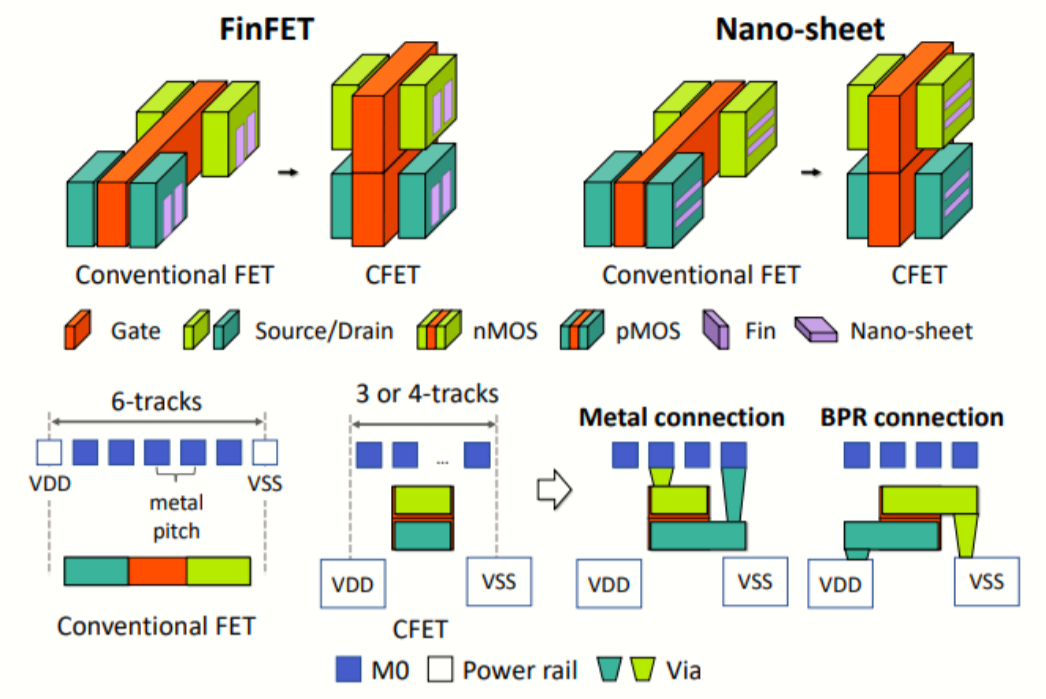

值得注意的下一代技术包括 CFET(互补 FET)晶体管和背面互连。CFET 晶体管是通过将 NMOS 晶体管堆叠在 PMOS 晶体管之上构建的,反之亦然。(见下图 [7]。这种设备技术可以将单元高度降低一半。但是,cell pin 的可访问性很差。因此,两个具有挑战性的问题是我们如何生成 CFET 单元以确保可接受的引脚可访问性以及怎样有效使用背面金属来缓解物理绕线时pin不可访问的问题。

背面金属 [8] 是在晶圆背面制造的金属线。这项技术为缓解实现高晶体管密度芯片(例如基于 CFET 的标准单元)的布线拥塞提供了绝佳的机会。背面金属可以以多种方式使用。它们可以用作 BPR(埋地电源轨),从而可以在背面安装 PDN(供电网络),从而大大简化 CDN(时钟传输网络)的金属使用和前端的信号路由。背面金属可用作信号网络以及 ECO 路由的 CDN 或路由。但是,EDA 社区应该解决两点:一是背面金属的使用不是免费的。对于 CDN 和信号,需要将背面导线连接到正面的单元 I/O 引脚,而对于 PDN,需要一个长过孔将 BPR 连接到上层的 MOSFET,它们不仅占用相当大的空间,而且需要很长时间延迟。应仔细考虑这些大开销,以充分发挥背面金属的优势。另一点是 backside metals 也可以用作 in-cell routing 中的 route。然而,单元布局综合如何有效地利用它们,以及它如何与物理设计协作,物理设计也希望将背面金属用于 BPR、CDN 和/或信号路由,这两个问题目前都尚未解决。

个人观点:DTCO是一个系统级的设计空间探索问题。需要有实力的工艺厂商和设计厂商合作,大陆目前只有海思和SMIC有希望在DTCO有突破,高校有机会在DTCO相关的模型和点方法等小方向上切入

原文:Invited: Physical Design Challenges for Design Technology Co-optimization

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?