AD7606特性及功能简介

AD7606/AD7606-6/AD7606-4[4]为 16 位同步采样模数数据采集系统(DAS),分别有 8、 6、 4 个采集通道。片上集成模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器、 16 位电荷再分配逐次逼近型 ADC 内核、数字滤波器、 2.5V 基准电压源及缓冲、 高速串行和并行接口。 AD7606 采用 5V 单电源供电,不再需要正负双电源,并支持真正±10V 或±5V 的双极性信号输。 所有的通道均能以高达 200 kSPS 的速率进行采样,同时输入端箝位保护电路可以承受最高达±16.5V 的电压。

传统的逐次逼近(SAR)型 ADC,由于其采样电容的设计,模拟输入前端一般需要运算放大器(简称运放,Operation Amplifier)来实现内部采样电容的驱动,正因此电容的存在, 其等效输入阻抗与采样频率相关,而且在一些高采样率的应用中,使得前端驱动运放的选择变得十分苛刻。但在 AD7606 内部的信号调理电路中,已经包含了低噪声、高输入阻抗的信号调理电路,其等效输入阻抗完全独立于采样率且固定为 1Mohm。同时输入端集成了具有 40 dB 抗混叠抑制特性的滤波器,更是简化了前端设计,不再需要外部驱动和滤波电路。因此,二次互感器输出的信号无需再经过运放来缓冲就可以直接接入 AD7606。

AD7606 内部集成了 2.5V 带隙电压基准和基准缓冲电路,其温度系数典型值为±10ppm/℃。设计应用中,选用内置基准或外部基准,将取决于系统的要求。多片 ADC 的设计中,如果需求高绝对精度, 则应采用高初始精度和低温度系数的外部基准,以消除不同器件内置基准之间的差异而带来的误差。 推荐选用初始精度 0.04%,温度系数 3ppm/℃的 ADR421B。如果需求多片 ADC 通道之间的数值匹配,可设置第一片 AD7606工作在内置基准模式,其余 AD7606 为外部基准模式,然后通过第一片 AD7606 的内置基准输出供给其余AD7606。 这样, 在不加外部基准的情况下即可保证多个 AD7606 通道间数据的匹配性,但此时系统的绝对精度取决于内置基准的性能。

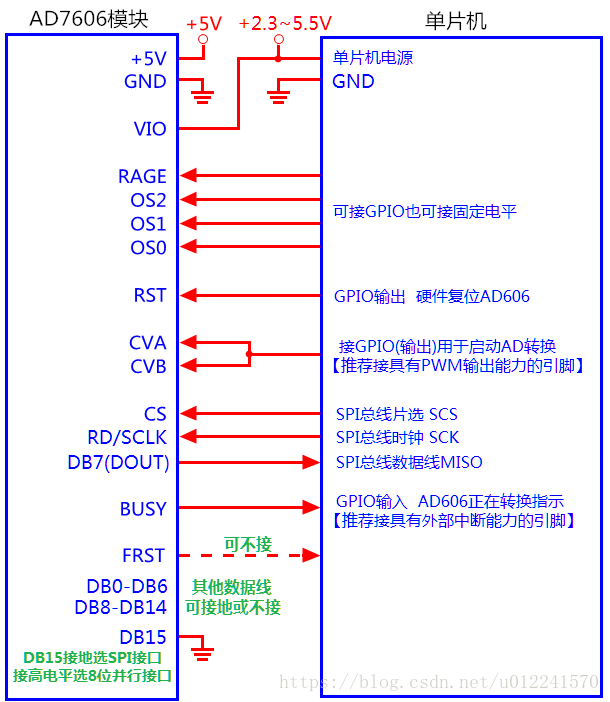

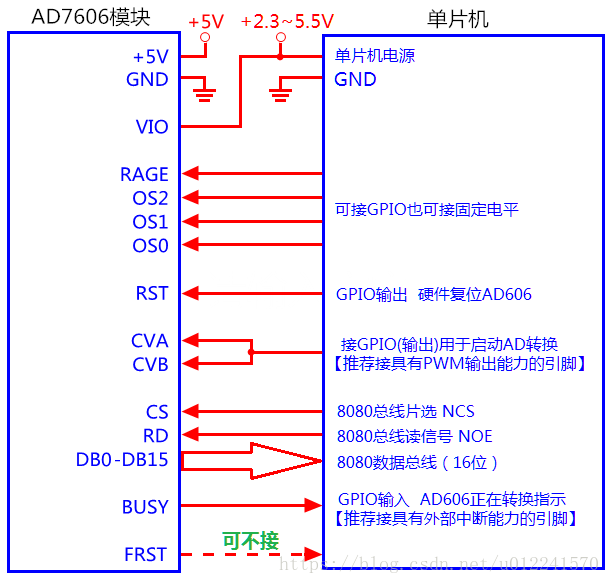

AD7606 的数字接口可以配置在并行或串行模式。数字接口的电平 Vdrive 为 2.3V~5.25V,可以跟当前任何主流的 CPU/DSP 连接。需要注意的是,当配置 AD7606 工作在串行接口模式时,数据总线的 DB[15:9]和 DB[6:0]管脚需要做接地处理。

AD7606 提供了过采样和数字滤波功能。通过管脚 OS[2:0]可以设置过采样倍数(OSR)为 x2, x4, x8, x16,x32, x64。过采样打开后,内部的过采样控制电路和 1 阶 Sinc 数字滤波器会自动被使能,同时-3dB 带宽也会相应的改变。

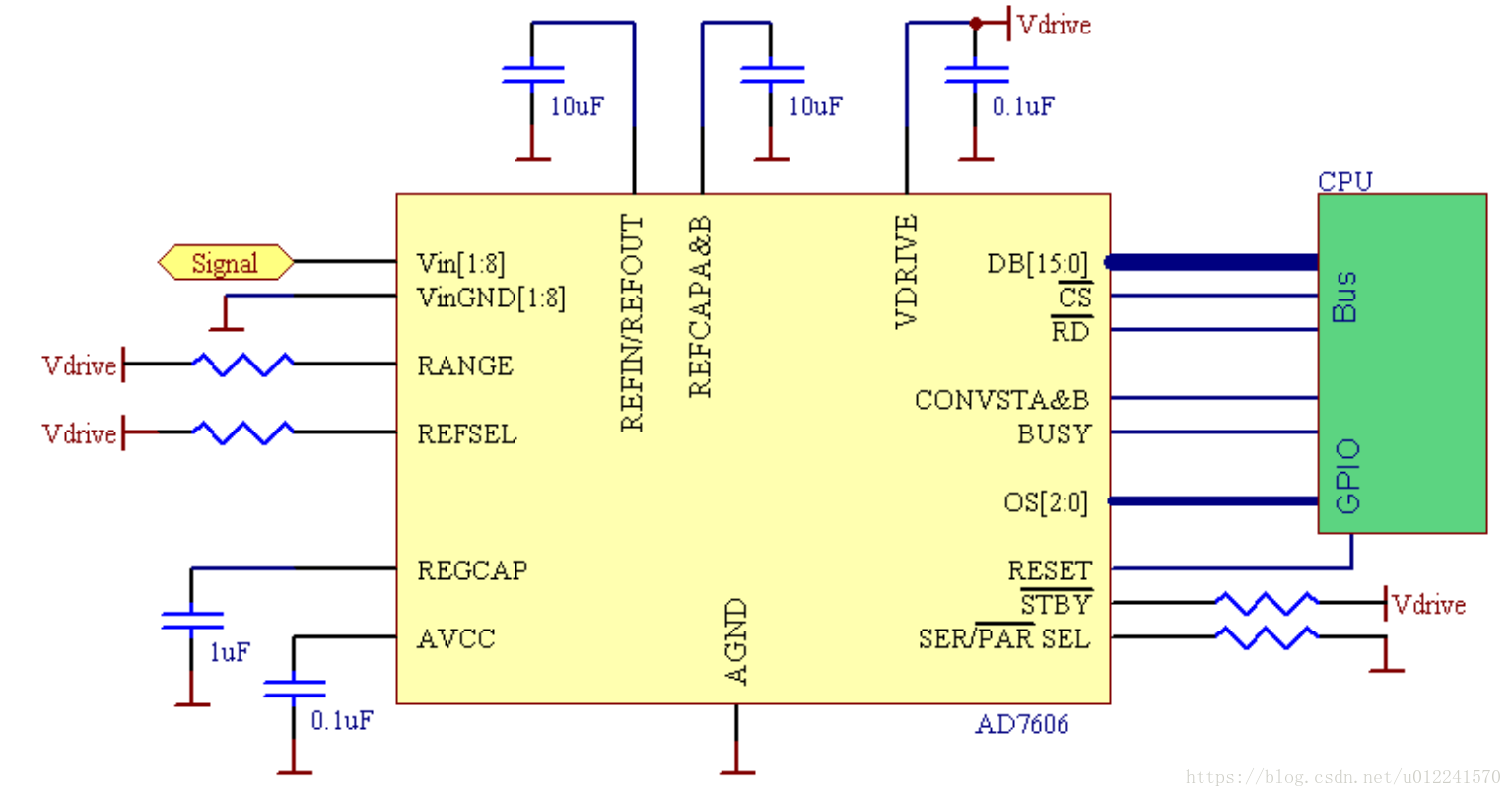

ADC 一般需要模拟电源和数字电源。大多数的系统都会有 5V 数字电源,却不一定具有 5V 模拟电源。此时如果模拟电路和数字电路共用同一个 5V 电源,有害的数字噪声可能会耦合到模拟电路并降低 ADC 的性能,通常应该避免这样的设计。如果不可避免,需要将 5V 的数字电源进行很好的滤波后再供给模拟电路用。 AD7606 的去耦设计十分简洁,仅需要 9 个电容,其中包括 2 个 10uF, 2 个 1uF, 5 个 0.1uF。

AD7606 外围电路参考设计:

AD7606串行接口接线图

AD7606并行接口接线图

AD7606是一款16位同步采样的模数转换器,支持8、6或4个采集通道,适用于±10V或±5V的双极性信号输入。该器件集成了多种功能,如模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器等。内置2.5V带隙电压基准,支持过采样和数字滤波功能,可配置并行或串行数字接口。

AD7606是一款16位同步采样的模数转换器,支持8、6或4个采集通道,适用于±10V或±5V的双极性信号输入。该器件集成了多种功能,如模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器等。内置2.5V带隙电压基准,支持过采样和数字滤波功能,可配置并行或串行数字接口。

3874

3874

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?