最近在做寄存器测试,发现UVM寄存器模型还挺有意思,在此记录学习调试的一些过程

一、UVM寄存器模型是什么?

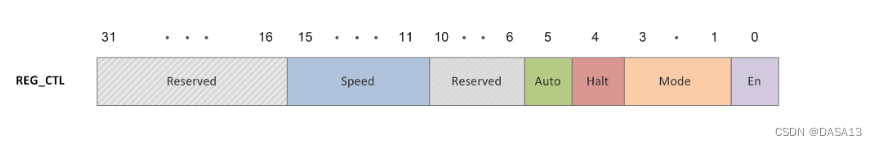

首先理解一下寄存器的结构,如下图所示,一个寄存器通常是32bit,这32bit由一个或多个域段组成,不同的域段又有各自的位宽和读写属性,写属性即每个域段的属性包括只读,只写,可读可写等等特性。

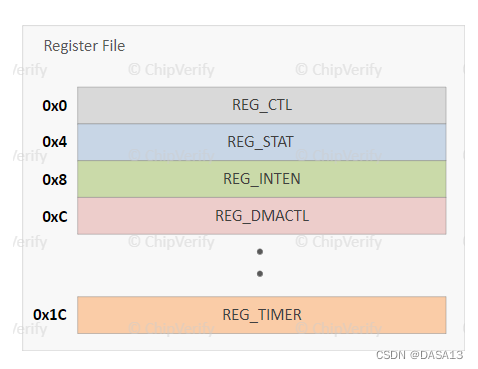

同时每个寄存器又有各自的地址,一般是按字节偏移,因为比如如果寄存器的位宽是32bit,则1个寄存器占据4字节的空间,所以寄存器间的地址间隔就是0x04h

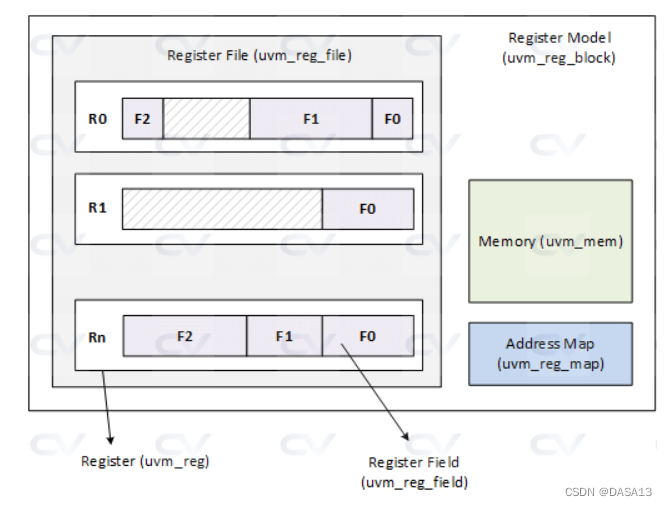

寄存器模型就是提供了一个结构和标准化的方式去建模并验证设计中的寄存器及memory

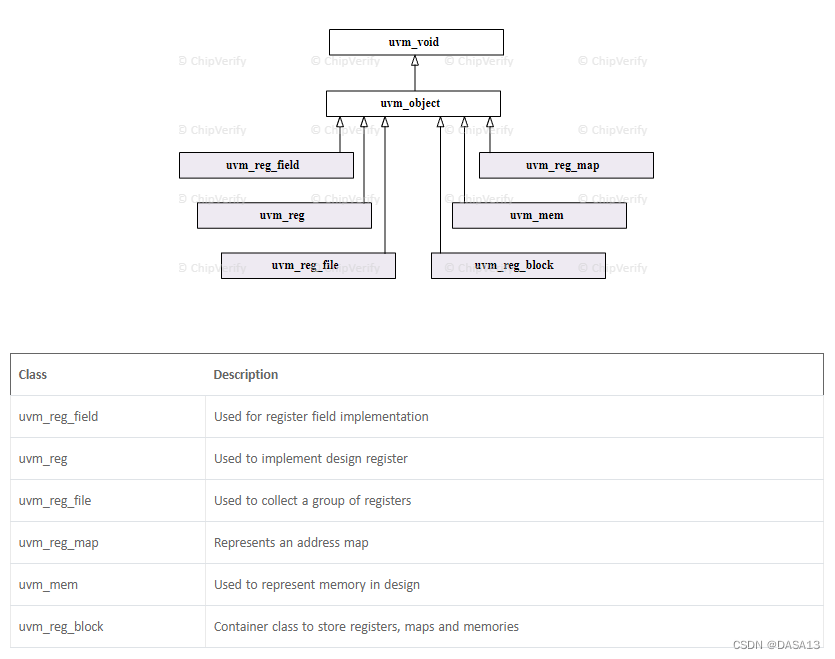

UVM寄存器模型包含的类

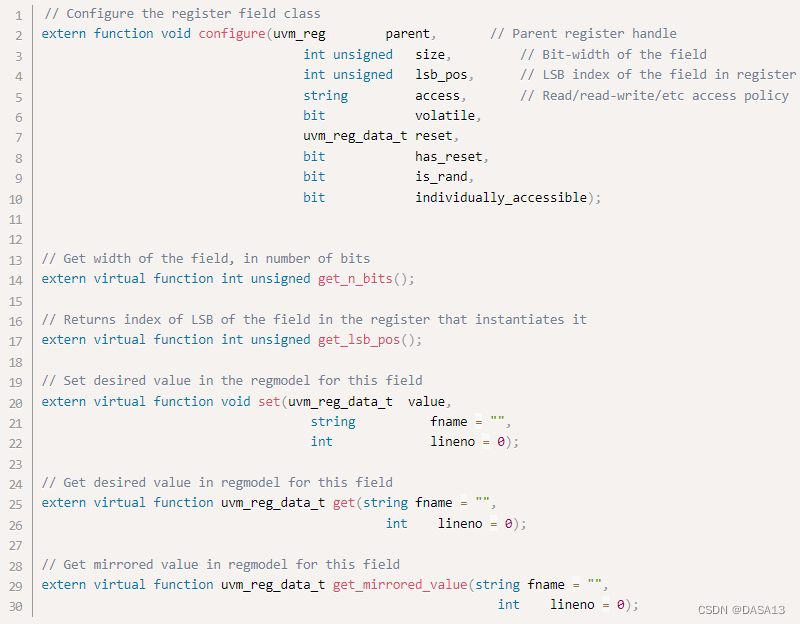

uvm_reg_field包含的function有:

configure:用于配置当前域段的的位宽,读写属性、复位值等

get_n_bits:获取当前域段的位宽

get_lsb_pos:获取当前域段的最低bit位

set:设置当前域段的期望值

get:获取当前域段的镜像值

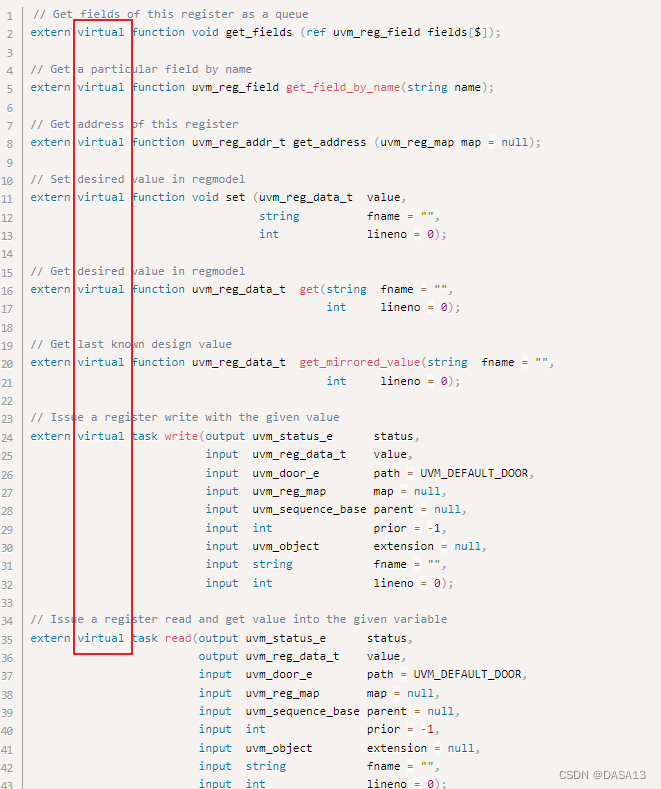

在uvm_reg中也定义很多function,如:

get_fields:获取寄存器的域段

uvm_reg_filed:根据域段名字(字符串)获取uvm_reg_field变量

get_address:获取寄存器地址

set:设置寄存器期望值

get:获取寄存器期望值

get_mirrored_value:获取镜像值

write/read:读写寄存器

以上function都是虚函数,也就意味着用户可以根据待测寄存器的特别进行重定义,比如有些寄存器的读写属性是寄存器模型中没有的,则可以通过扩展uvm_reg或uvm_reg_field类来重定义寄存器模型中相关function的方式实现想要的读写属性。

寄存器模型的读写属性有以下21种,但根据不同项目的需求,以下属性难以涵盖所有可能的场景:

1. RO:只读属性,只能从外部读取值,无法写入。用于表示仅由硬件产生或自动生成的寄存器。

2. WO:只写属性,只能从外部写入值,无法读取。用于表示仅由软件写入的寄存器。

3. RW:可读写属性,可以从外部读取和写入值。这是最常见的属性类型。

4. RC:只读清除属性,只能从外部读取值,但是在读取后,该位会被自动清除为0。用于表示需要清除的标志寄存器,但不允许软件写入该寄存器。

5. RS:只读设置属性,与RC类型相似,但在读取后会将该位自动设置为1。用于表示需要设置的标志寄存器,但不允许软件写入该寄存器。

6. W1C:可写一次且清除属性,只能从外部写入值,但在写入后,该位会被自动清除为0。用于表示需要清除的标志寄存器。

7. W1S:可写一次且设置属性,与W1C类型相似,但在写入后会将该位自动设置为1。用于表示需要设置的标志寄存器。

8. RW1C:可读写一次且清除属性,可以从外部读取和写入,但是在读取后,该位会被自动清除为0。用于表示需要清除的标志寄存器。

9. RW1S:可读写一次且设置属性,与RW1C类型相似,但在写入后会将该位自动设置为1。用于表示需要设置的标志寄存器。

10. W1T:可写一次且翻转(TOGGLE)属性,只能从外部写入值,但是在写入后,该位会自动翻转(从0变为1或从1变为0)。用于表示需要翻转的标志寄存器。

11. RW1T:可读写一次且翻转属性,可以从外部读取和写入,但是在读取后,该位会被自动清除为0。在写入时,如果该位的值为1,则该位会被自动翻转。用于表示需要翻转的标志寄存器。

12. WO1C:只写一次且清除属性,只能从外部写入值,但在写入后,该位会被自动清除为0。用于表示需要清除的标志寄存器,但不允许软件写入该寄存器。

13. WO1S:只写一次且设置属性,与WO1C类型相似,但在写入后会将该位自动设置为1。用于表示需要设置的标志寄存器,但不允许软件写入该寄存器。

14. WC:只写清除属性,只能从外部写入值,写入时该位会被清零。用于表示需要清除的标志寄存器,但不允许软件读取该寄存器。

15. WS:只写设置属性,与WC类型相似,但在写入后会将该位自动设置为1。用于表示需要设置的标志寄存器,但不允许软件读取该寄存器。

16. RCLR:可读清除属性,可以从外部读取和写入值,但在读取后,该位会被自动清除为0。在写入时,该位会被清零。用于表示需要清除的标志寄存器。

17. RSET:可读设置属性,与RCLR类型相似,但在写入时会将该位设置为1。用于表示需要设置的标志寄存器。

18. WOC:只写一次清除属性,只能从外部写入值,但在写入后,该位会被自动清除为0。用于表示需要清除的标志寄存器,但不允许软件读取该寄存器。

19. WOS:只写一次设置属性,与WOC类型相似,但在写入后会将该位自动设置为1。用于表示需要设置的标志寄存器,但不允许软件读取该寄存器。

20. WC1T:只写清除一次且翻转属性,只能从外部写入值,但是在写入后,该位会自动翻转且被清零。用于表示需要清除和翻转的标志寄存器,但不允许软件读取该寄存器。

21. WS1T:只写设置一次且翻转属性,与WC1T类型相似,但在写入后会将该位自动设置为1。用于表示需要设置和翻转的标志寄存器,但不允许软件读取该寄存器。

1077

1077

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?