具体内容可参考下文。

CXL 寄存器介绍 (1) - 寄存器分类_MangoPapa的博客-CSDN博客

补充:

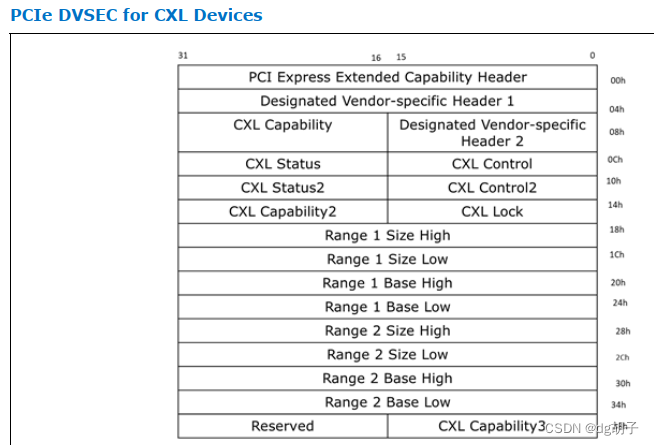

cxl configuration space register

:pcie空间中以DVSEC capability进行实现,实现相关的cxl寄存器。DVSEC:pcie定义的一种vendor extend capability。在pcie空间中基地址偏移0x700+.

上图定义pcie定义的cxl device相关dvsec示意图。

cxl device 在host向device空间映射时最多可以映射两块device physical address。vendor-specific header1为1E98h。range register最小为256MB;配置中需要和HDM decoder(如果使能)的值一致,HDM decoder用于内存交织进行使用,即有多个cxl RP连接到一个cxl bridge。

cxl地址范围: Memory_Base[63:28] <= address < Memory_Base[63:28]+Memory_Size[63:28]

类似于pcie bar空间的范围。具体详见spec中8.1章节。

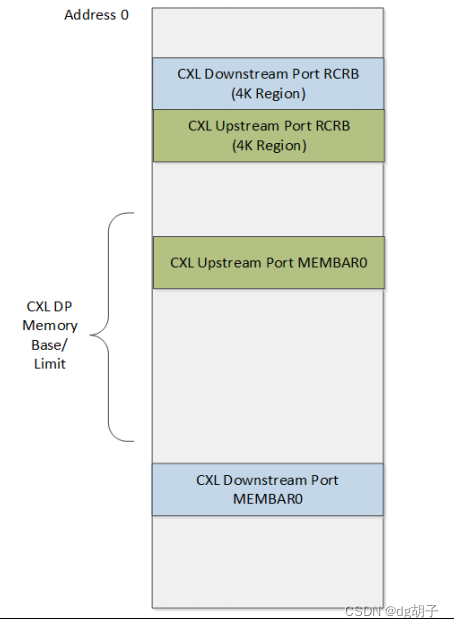

memory map register

cxl内存映射寄存器位于6个区域中。用于不能通过pcie配置空间进行发现的设备(文章中RCH,RCD均为cxl 1.1的host和device设备)。cxl 1.1使用pcie RCRB实现。其中RCH下游和RCD上游端口分别实现一个membar0区域(component registers),用于host配置cxl subsystem component。软件使用cxl.io内存读取和写入来访问内存映射寄存器。其中cxl USP membar0必须放在cxl DP memory limit空间中(类似于pcie type1 类型limit空间)

cxl spec可在官网进行下载:

1038

1038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?