使用软件: Vivado

DDS信号发生器

基本原理

DDS基本原理

[百度] DDS信号发生器采用直接数字频率合成(Direct Digital Synthesis,简称DDS)技术,把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。

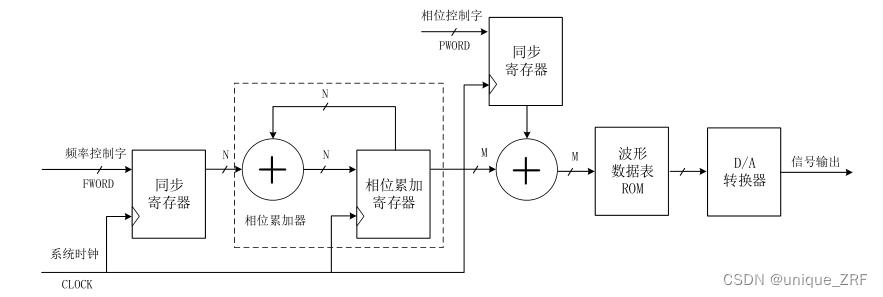

DDS基本结构图:

由图可以看出,DDS 主要由相位累加器、相位调制器、波形数据表以及 D/A转换器构成。

其中相位累加器由 N 位加法器与 N 位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是DDS 输出的信号频率,相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出数据送到 D/A 转换器,由 D/A 转换器将数字信号转换成模拟信号输出。

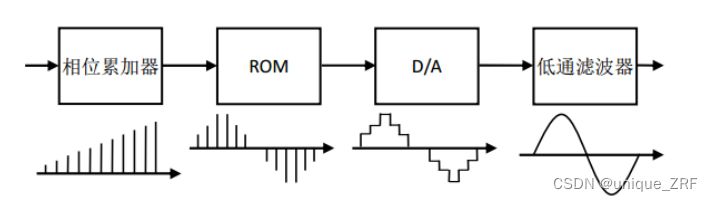

DDS信号流程示意图如下:

这里相位累加器位数为 N 位(N 的取值范围实际应用中一般为 24~32),相

当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为1/2N

若DDS的时钟频率为Fcl,频率控制字fword=B,则输出频率Fout=BxFclk/2N

因此理论上由以上三个参数就可以得出任意的Fout输出频率。且可得出频率分辨率由时钟频率和累加器的位数决定的结论。当参考时钟频率越高,累加器位数越高,输出频率分辨率就越高。

为了合理控制ROM的容量,此处选取ROM查询的地址时,可以采用截断式,即只取32位累加器的高M位。这里相位寄存器输出的位数一般取10~16位。

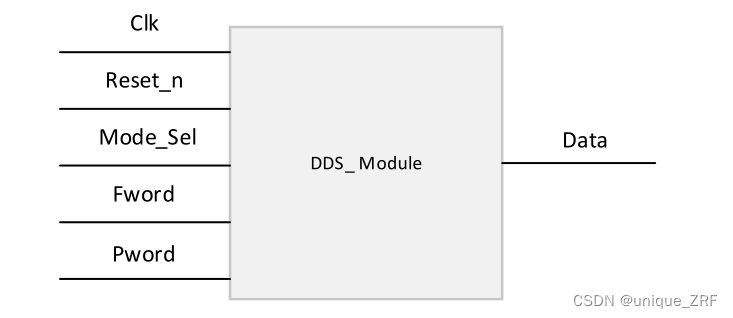

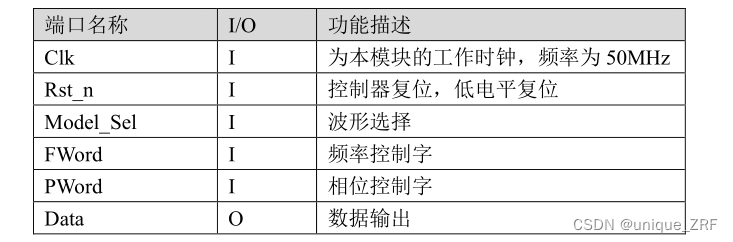

DDS模块

在本设计中参考时钟Fclk 频率为50 MHz,相位累加器位数 N 取32 位,频率控制字位数 M 取 12 位。经过以上的分析,可以得出 DDS 模块的端口模块如下图所示:

端口功能描述:

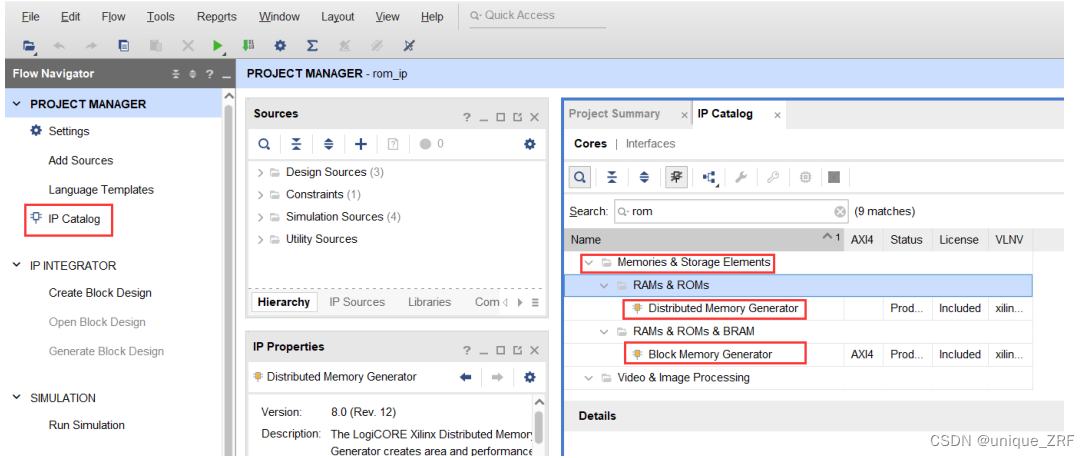

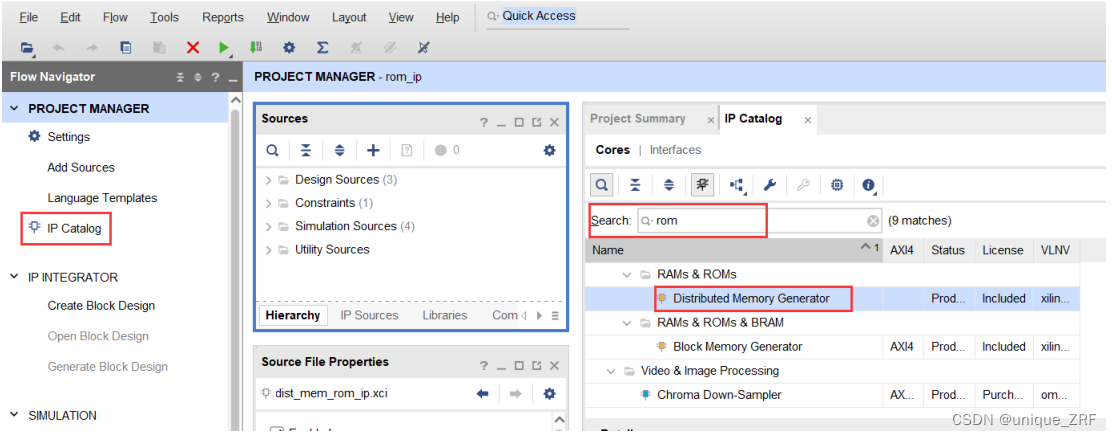

ROM IP的使用

单击 IP Catalog,在右边窗口 Search 位置输入rom,在Memories &Storage Elements 下可以看到有两个与 ROM 相关的 IP,一个是 Distributed Memory Generator,另一个是Block Memory Generator,先简单说说两个的差别,两者最主要的差别是生成的 Core所占用的 FPGA 资源不一样,从 Distributed Memory Generator 生成的 ROM/RAM Core 占用的资源是 LUT(查找表,查找表本质就是一个小的 RAM);从 Block Memory Generator 生成的 ROM/RAM Core 占用的资源是 Block Memory(嵌入式的硬件 RAM)

在 IP Catalog 窗口选择 Distributed Memory Generator 并双击。

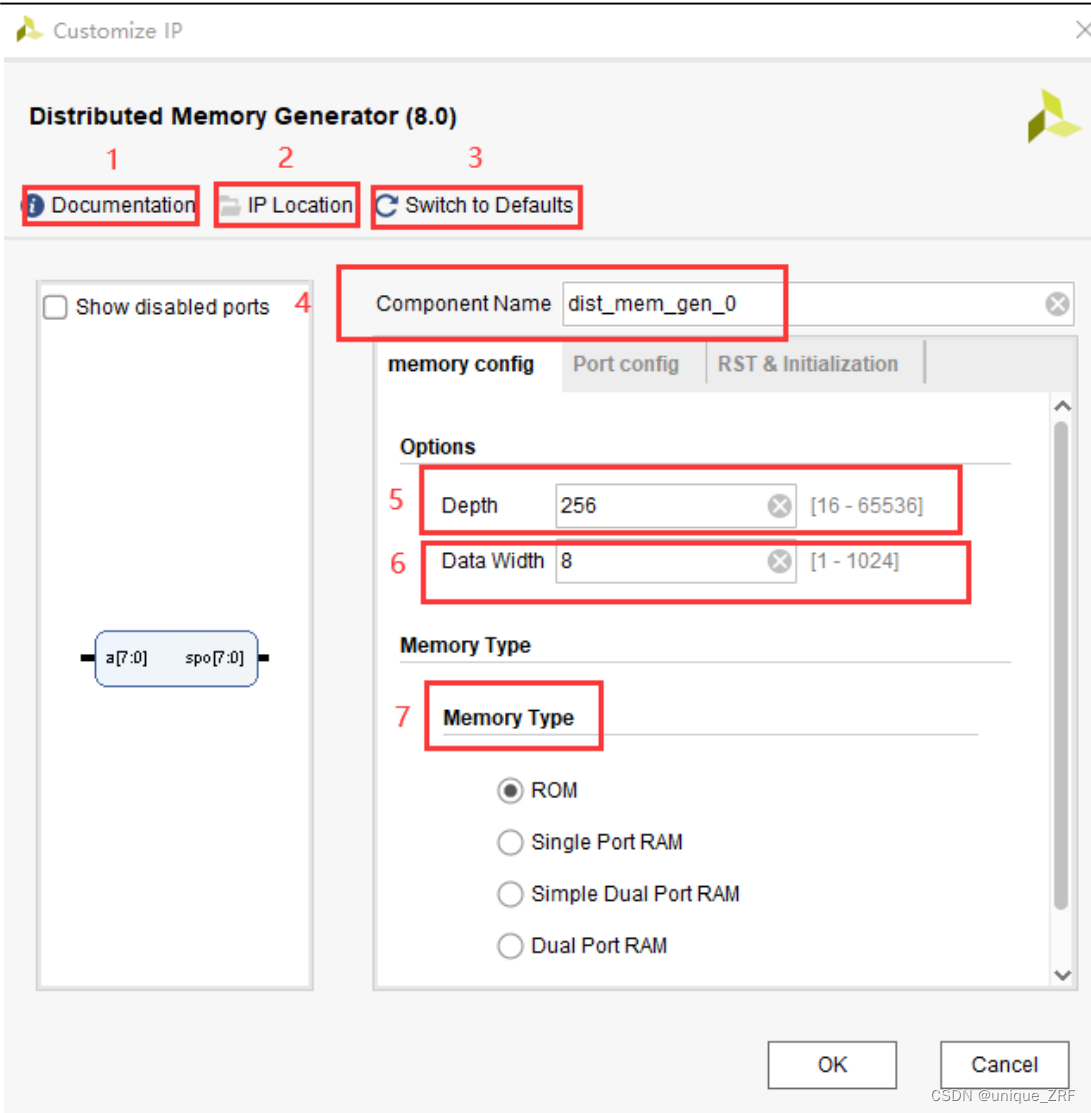

进入IP配置界面,如下。

进入IP配置界面,如下。

(1)Documentation:IP 相关文档入口,点击后出现如下内容

(2)IP Location:生成 IP 的存放路径,可以通过点击 … 设置更换存放路径,默认是存放在工程路径下的 bin_counter.srcs\ sources_1\ ip,我这里就保持默认。

(3)Switch to Default:点击后所有的设置恢复到默认值

(4)Component Name:设置生成 IP Core 的名称,我这里将名字设置为 dist_mem_rom_ip;

(5)Depth:设置 ROM 深度,我这里设置 256;

(6)Data Width:设置数据位宽,我这里设置 8;

(7)Memory Type:选择存储类型,这里选择 ROM

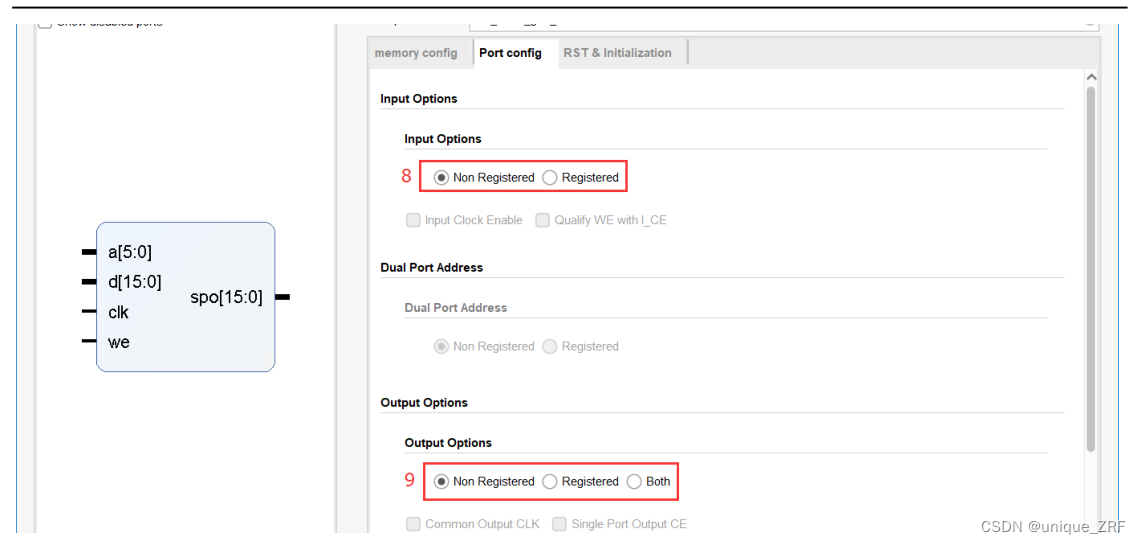

(8)Input Options:设置是否对输入的地址增加一级寄存器,这里设置选择 Registered,对输入的地址增加一级寄存器(也可以选择 Non Registered,不增加寄存器)。

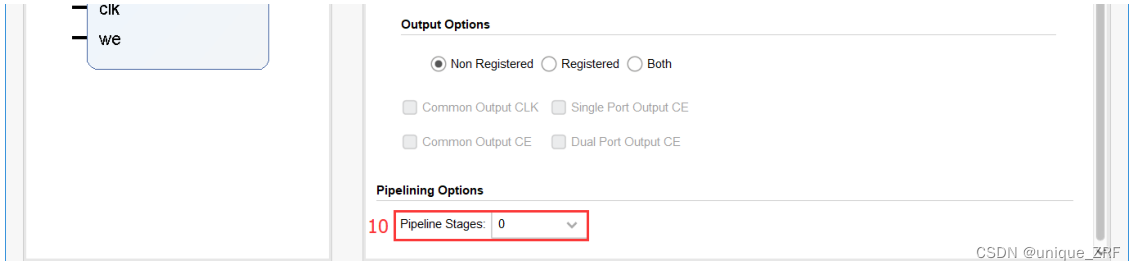

(9)Output Option:设置是否对输出的地址增加一级寄存器,这里设置选择 Both,对输出数据信号 spo 和增加一级寄存器后的输出数据信号 qspo 都从端口引出。下面还有个Single Port Output CE 可选配,当勾选后,ROM Core 就会多出一个 qspo_ce 的端口,这个信号是用来控制使能输出寄存器的时钟。这里没有用这个功能,不勾选该项。

(10)Pipeline Stages:流水线级数,在生成 ROM 模式下,不可配。

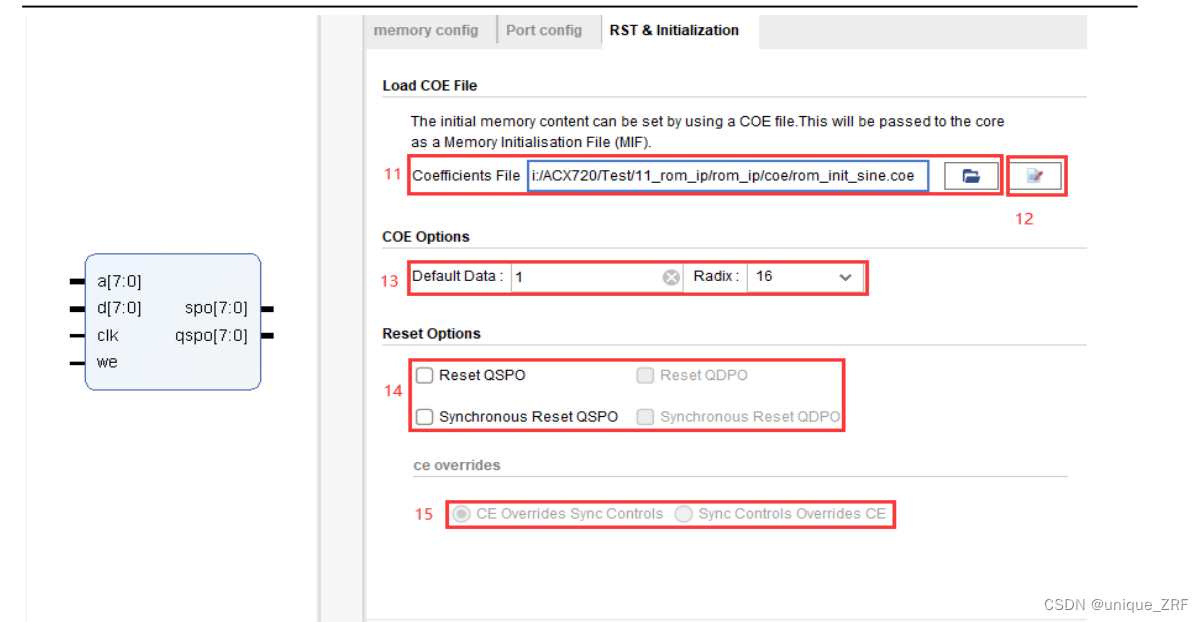

(11)添加 COE 文件位置,可以通过选择路径添加已有的 COE文件,软件会通过 COE 文件生成 ROM 初始化文件 MIF 文件。关于如何创建 COE 文件看下一步骤。

(12) 编辑按钮,当(11)中未加载 COE 文件时,点击这里按钮,会弹出提示框,点击YES 可进入到创建 COE 文件的流程,这里点击 YES。

(13)COE Options:设置 ROM 中初始化数据没有覆盖的区域的数值,比如 ROM 深度 256,添加的 COE 文件中仅初始化了200 个数据,这里就是统一设置剩下的 56 个数据的数值。

(14)Reset

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6162

6162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?