应用案例系统

样例系统包括:

AXI bus master: 一个DMAC,两个ARM处理器

一个AXI互联模块,两个AMBA协议桥组件

PrimeCell slaves: 一个动态内存控制器DMC,一个静态内存控制器SMC,一个timer,一个GPIO,一个通用异步收发器UART

AXI互联模块使每个bus master能够访问slaves。ARM处理器能够访问DMAC的APB接口,通过使用合适的AXI to APB桥实现。

DMAC特性

| 用于灵活编程DMA传输的指令集 |

| 一个AXI master接口,用于执行DMA传输 |

| 双APB slave接口,设计给安全态和非安全态,用于访问DMAC内部寄存器 |

| 支持TrusZone技术 |

| 支持多种传输类型: memory to memory memory to peripheral peripheral to memory scatter-gather |

| 可配置的RTL,使得DMAC能够按照应用需要优化 |

| 每个DMA channel都有可编程的安全状态 |

| 使用中断输出信号来通知不同DMA事件的发生 |

DMAC可配置特性

| AXI 数据总线宽度 |

| active AXI读事务的数量 |

| active AXI写事务的数量 |

| 同时active的DMA channel数量 |

| 内部数据buffer的深度 |

| 指令缓存的行数,以及一行包含多少word |

| 读指令队列的深度 |

| 写指令队列的深度 |

| 外设请求接口的数量 |

| 中断输出信号的数量 |

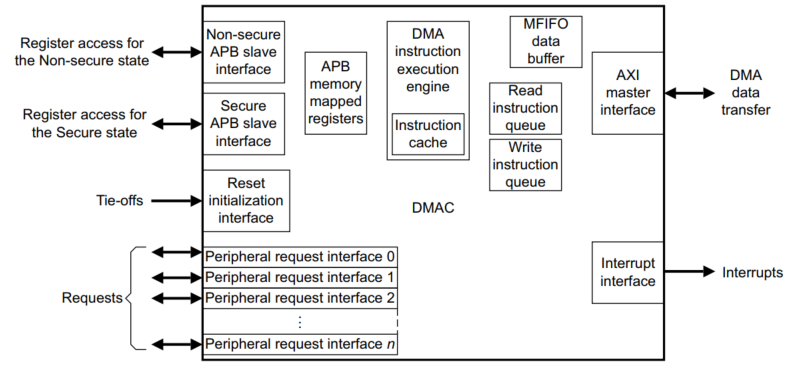

功能概览

DMAC包含一个指令处理模块,可以执行代码控制DMA传输。程序代码存放在一块系统内存上,DMAC可以使用AXI接口访问代码。DMAC内部有一个cache缓存指令,其行长和深度都可配。

最大可配置8个DMA channel,每个channel可以支持DMA操作的单独并发线程。另外还有一个单独单独DMA管理线程,可以用来初始化DMA channel线程。每个AXI时钟周期DMAC执行一条指令。

DMAC使用可变长指令(1-6 bytes)。每个DMA channel有一个独立的PC寄存器。当一个线程要从一个地址中取指时,cache执行查找。cache hit时cache立即返回数据,否则线程会停住,DMAC使用AXI接口做cache line fill。如果指令大于4 bytes或超过了cachel line的最后位置,cache会执行多个cache访问来获取指令。

双APB接口,一个用于secure状态,一个用于Non-secure状态。可以使用APB接口访问状态寄存器,也可以直接在DMAC里执行指令。

PL330 DMAC驱动不同之处

PL330 的DMAC驱动和普通的DMAC驱动的不同的地方主要是:

1) PL330 DMAC有自己的特殊指令集,1-6个字节不定长,主要包括

DMAMOV/DMALD/DMAST/DMAGO

2) PL330 DMAC驱动需要:

申请一块指令buffer,在buffer里面存放DMAC的指令数据,完成DMA功能。

执行 DMAGO 指令,让channel的 pc指针指向指令buffer,从 buffer 取值执行。

(DMAGO 指令的本身的执行,是通过写 S5PV210 芯片的 DBGCMD/DBGINST0/DBGINST1 这3个寄存器实现的)

1084

1084

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?