这个专栏要干的事:学习PCIE理论知识,学会PCIE IP/VIP的使用。可以达到上手做项目,而不是空有理论

适合谁看:正在学习PCIE 设计验证,但学的过于零散。想有对比的系统的学习。

低价收费的目的:抵制胡乱传播转载现象。

版本控制:便于增加内容以及勘误

| 版本 | 说明 |

| 初始版本 |

1、8B10B/128B130B编码方式

1.1、8b10b

为了保持直流平衡,设计原8b的每种值,都使用两种编码(正负极性),根据上次发送的最后一个符号的失调来选择其中一个编码,因此需要512个编码。

然而,许多中性失调编码具有相同的值(例如D28.5),因此并非所有512个编码都被使用。

因此,超过一半的可能编码没有被使用,如果接收方看到这些编码,将被视为非法。

D10.3的含义是8B的高三位为d3,低5位为d10。8b码即为:011 01010。

10b编码后的0和1分3种:4个0/6个1,6个0/4个1,5个0/5个1。

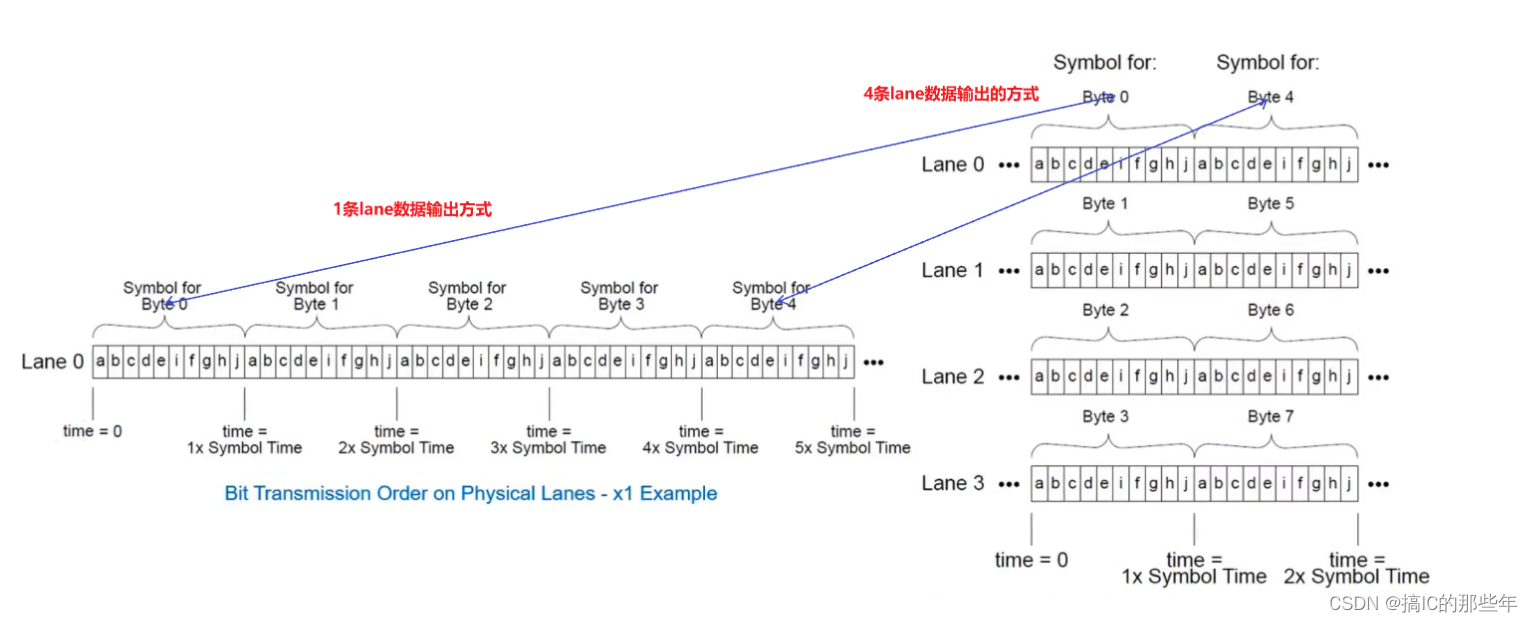

10b编码经过并转串之后是低bit先出。如果lane数量不止1条,数据会先布满所有lane。

1.2、128b/130b

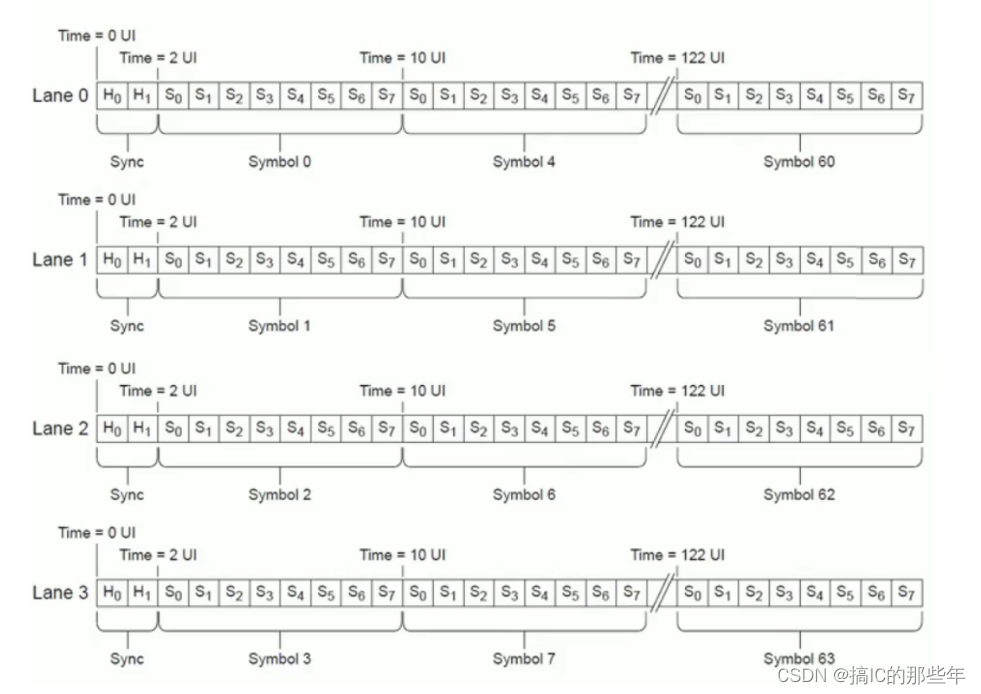

130bit=128bit symbol + 2bit sync head

这样的130bit称为一个block。其中1symbol=8bit,也就是说在1条lane上接收1个head+16个symbol,也就是接收了1个block。

这样的block有两种类型,分为data block和ordered set block (OS block)

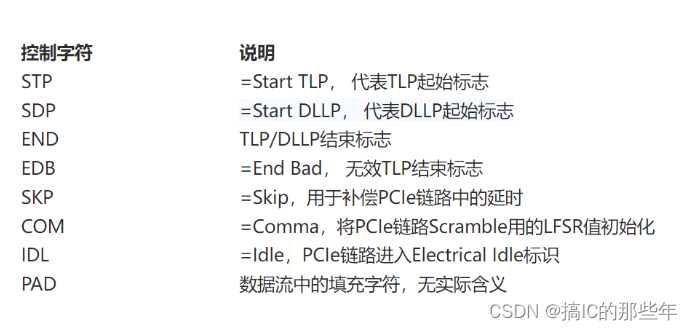

2、控制Symbol

2.1、8b10b

2.2、128b130b

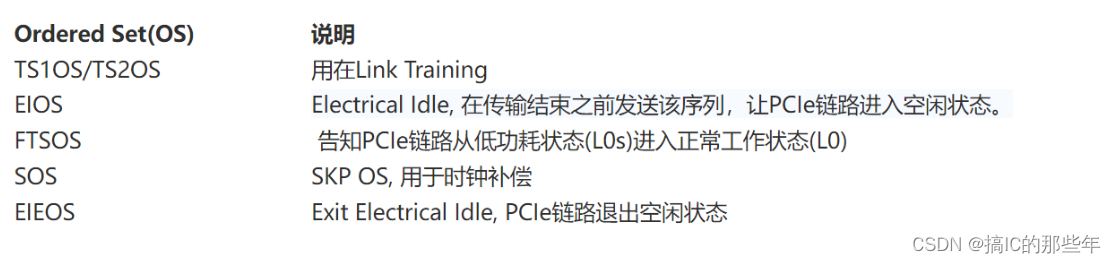

3、OrderSet

OrderSet 有序集,它不是TLP/DLLP,是用于链路训练,或者是链路电源管理等。

8b10b和128b120b下拥有的OrderSet基本相同,也都是16个Symbol组成。只不过由于编码方式不同,导致表现上会不一样。

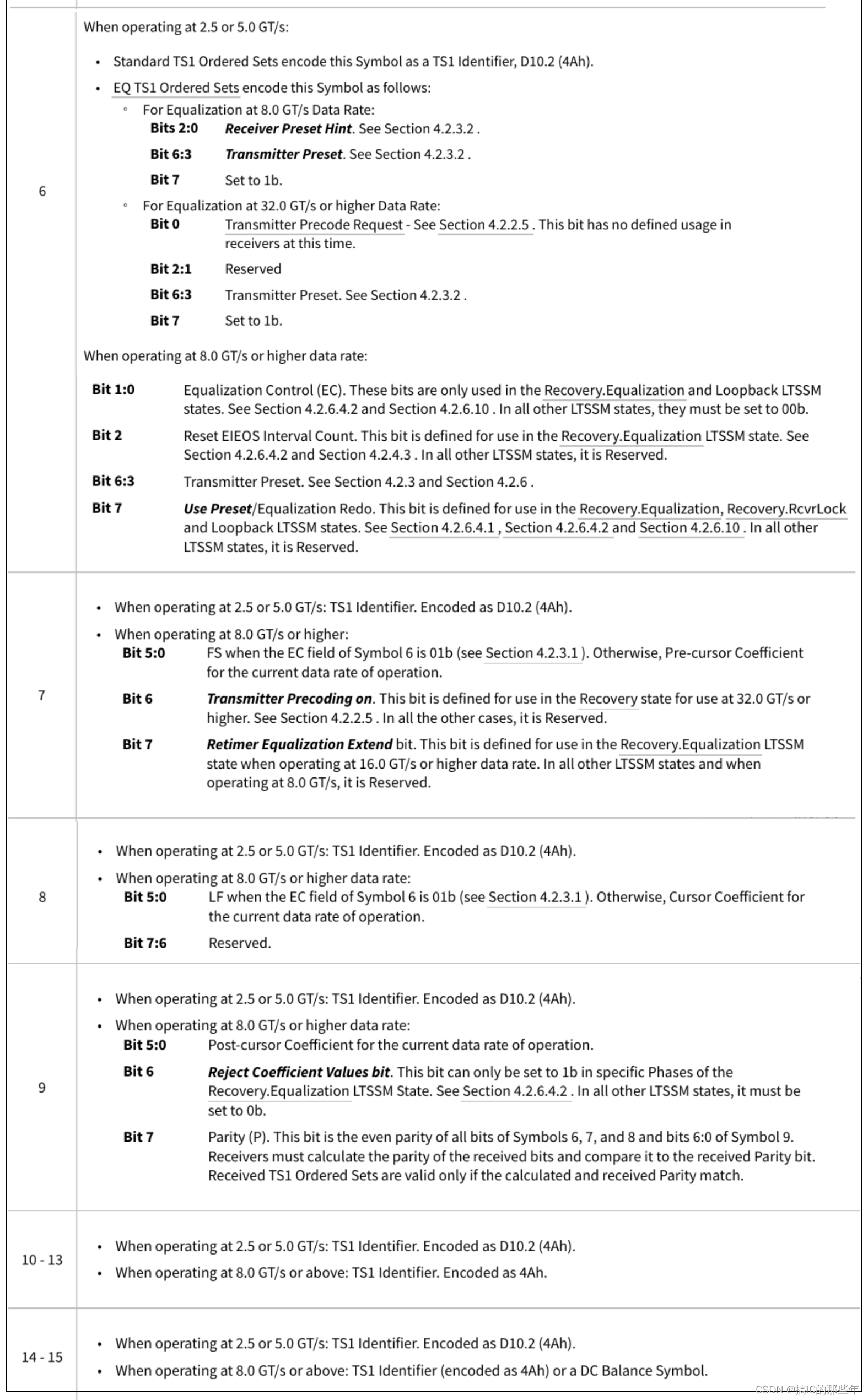

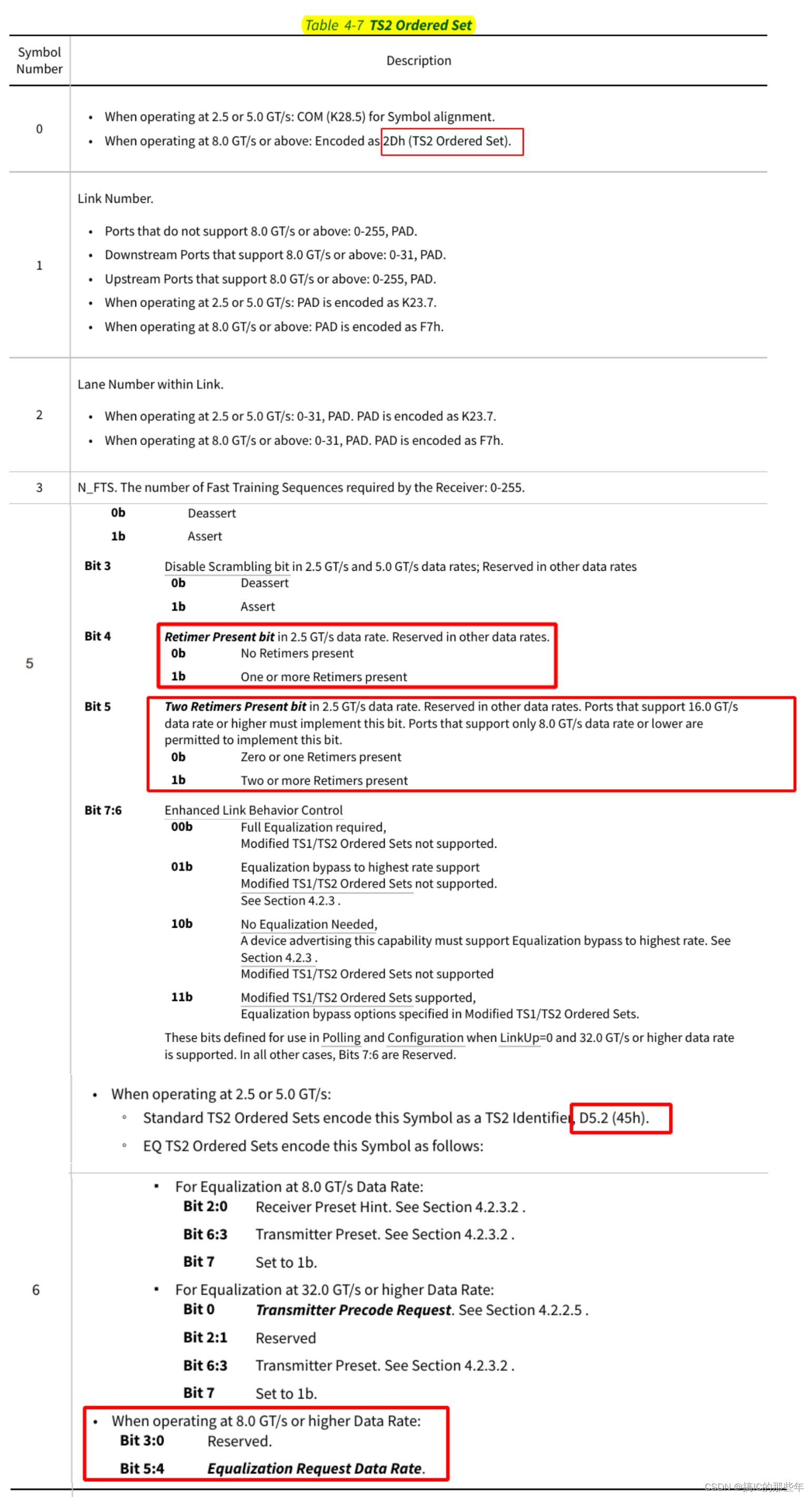

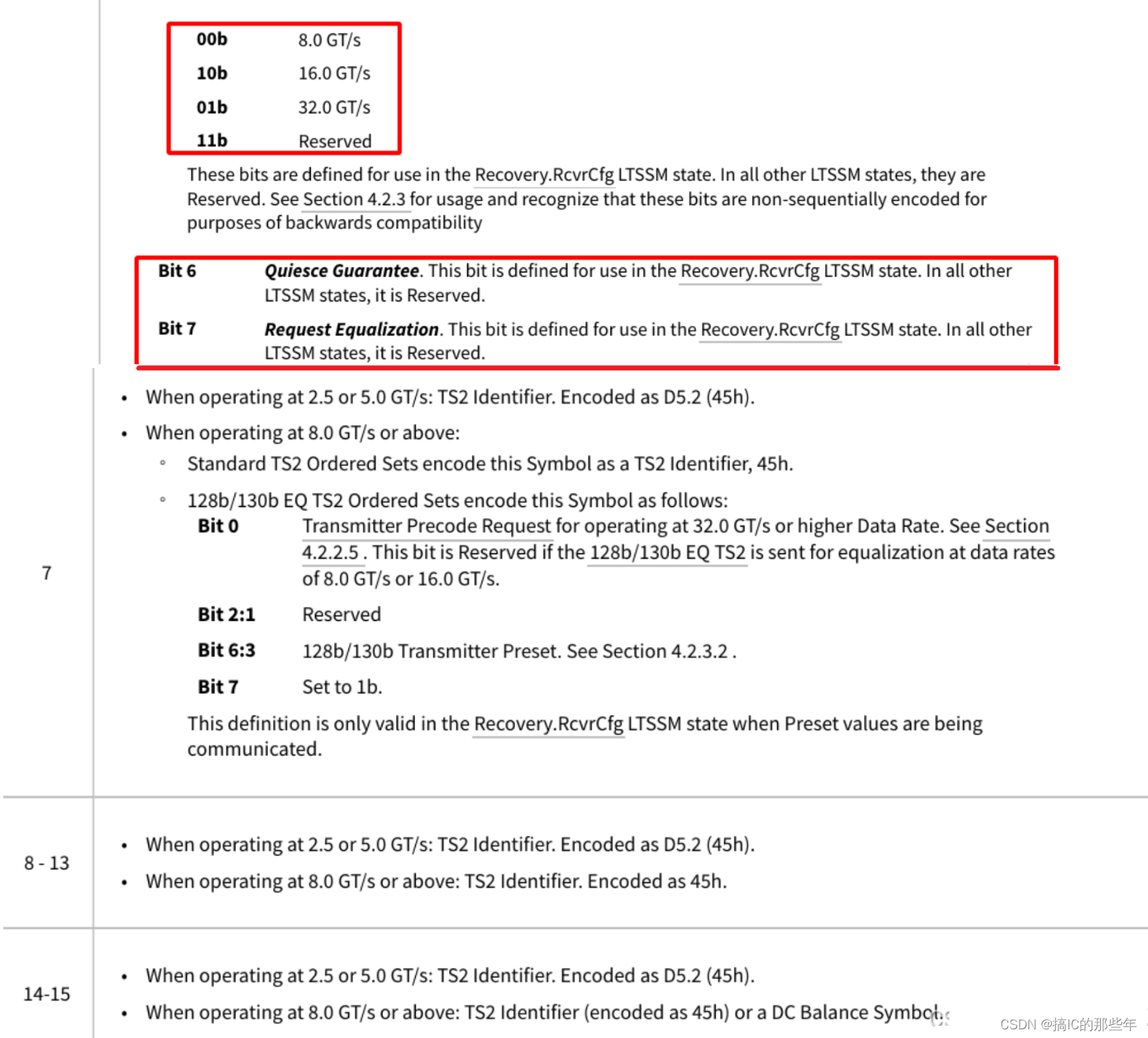

4、OrderSet-TS1/TS2

训练序列TS,用于初始化位对齐( initializing bit alignment)、符号对齐(Symbol alignmen)和交换物理层参数( exchange Physical Layer parameters)的有序集组成。当数据速率为 2.5 GT/s 或 5.0 GT/s 时,Ordered Sets 永远不会被加扰,而是始终采用 8b/10b 编码。 当数据速率为 8.0 GT/s 或更高时,使用 128b/130b 编码,需要对其进行加扰。

在进行建链的时候,RP和EP 互相发送TS1、TS2序列 ,来确定两端的情况,每个序列由16个Symbol 组成每个 Symbol 有着不同的含义。

在物理层的LTSSM状态机中,TS1序列和TS2序列的使用发方法不同,TS1、TS2由16个字符(Symbol)组成;TS1序列作用是检测PCIEe 链路的配置信息,而TS2序列确认TS1序列的检测结果。

使用 8b/10b 编码时,仅当 Symbol 6 与前一个 TS1 或 TS2 有序集Symbol 6 匹配,对于128/130b 则是TS1或TS2 Symbol 6-9 与之前的Symbol 6-9 相匹配。 比如说polling下,TS序列会发1024 个 有8个连续的 发这么多的原因是害怕有误码。

下面两张图片列出了在8b10b(2.5/5GT),128b130b(8GT↑)下,TS1/TS2的内容区别。

5、DLLP和TLP标识

为DLLP和TLP增加标识的目的是方便找到DLLP和TLP的边界

5.1、8b10b

增加Start/End Symbol 即:STP/SDP/END

以一个物理层发送TLP为例:一个TLP在通过物理层时,首先要加上物理层的前后缀STP和END的控制字符,无需加扰;

数据链路层前缀、TLP和数据链路层后缀都属于数据字符,需要加扰,并由物理层发向PCIe链路。

5.2、128b/130b

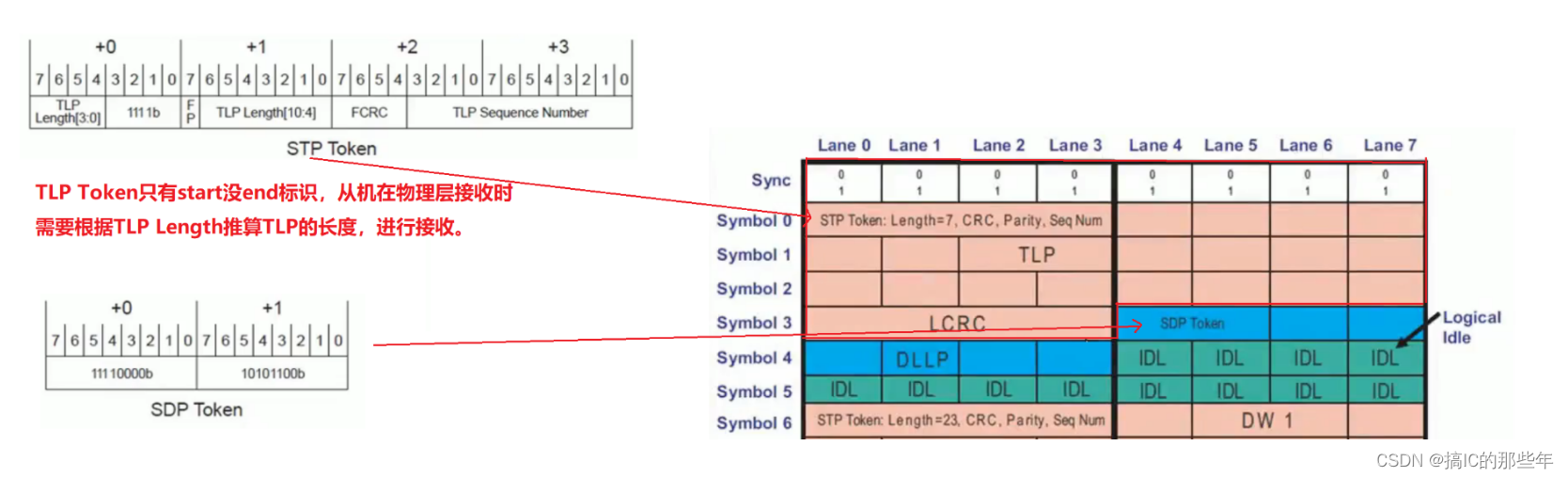

在128B/130B时,使用Token代替了8b/10b时的symbol。且没有end标识,取而代之的是start标识中的length。

6、Gen12/Gen34数据在lane上的规则

6.1、8b10b

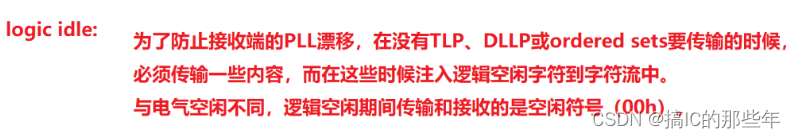

如果PCIe链路从Logical Idle之后开始数据流的传输时,STP和SDP必须放在Lane0;如果不是从Logical Idle之后开始数据流传输,STP和SDP可以放在Lane0,4,8等;

在PCIe x2链路中,END/EDB放在Lane1,其他链路中放在Lane3,7,11等;

一个数据包结束之后,其他的数据包还没Ready, 这个时候需要PAD字符补位到最后一个Lane;

当数据包传输结束,所有Lane发送Logical Idle字符“idle(00)”;

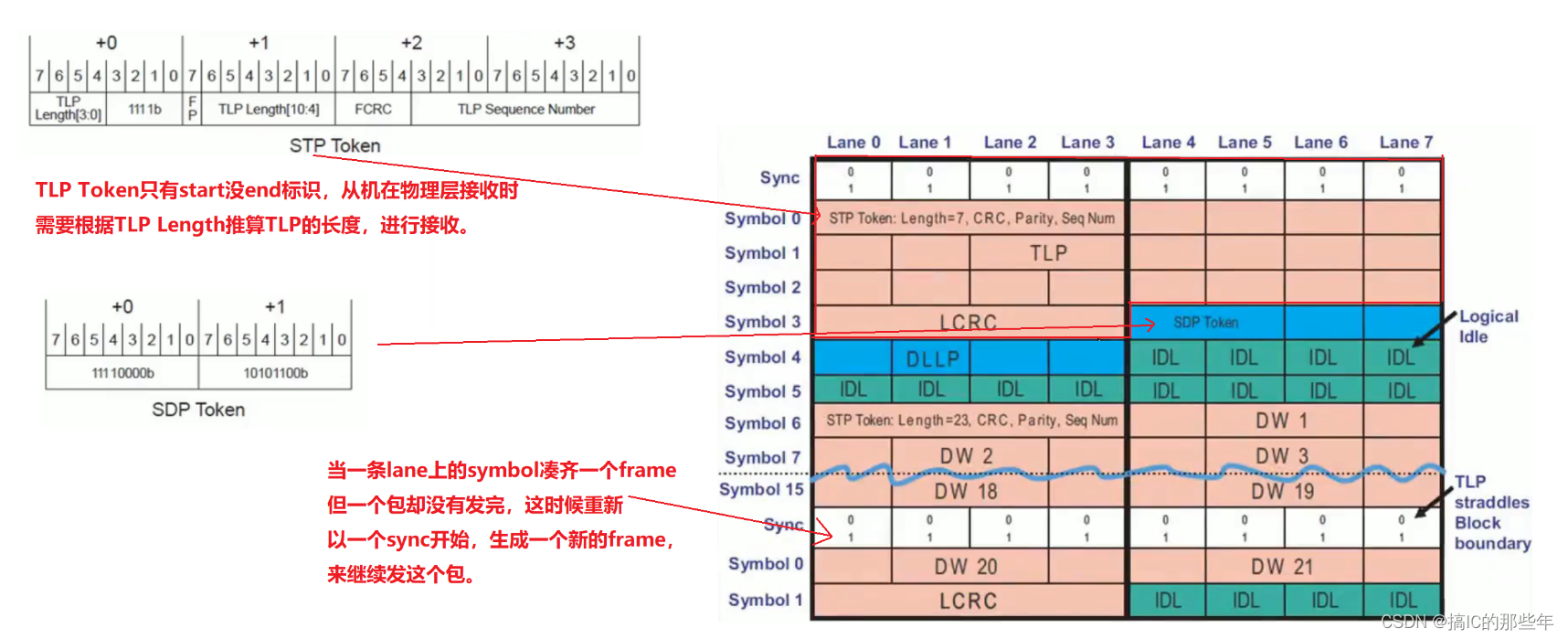

6.2、128b130b

1、STP在IDL后,必须从lane0开始。(见第一个block的symbol6)

2、TLP可以跨越block,而不用再次发送STP Token,(见第一个block的symbol6,发起了STP Token,开始了TLP传输,直至第一个block的symbol15,该TLP并没有传完,需要切到下一个block,下一个block则直接发送剩余数据,不用新起STP Token。)

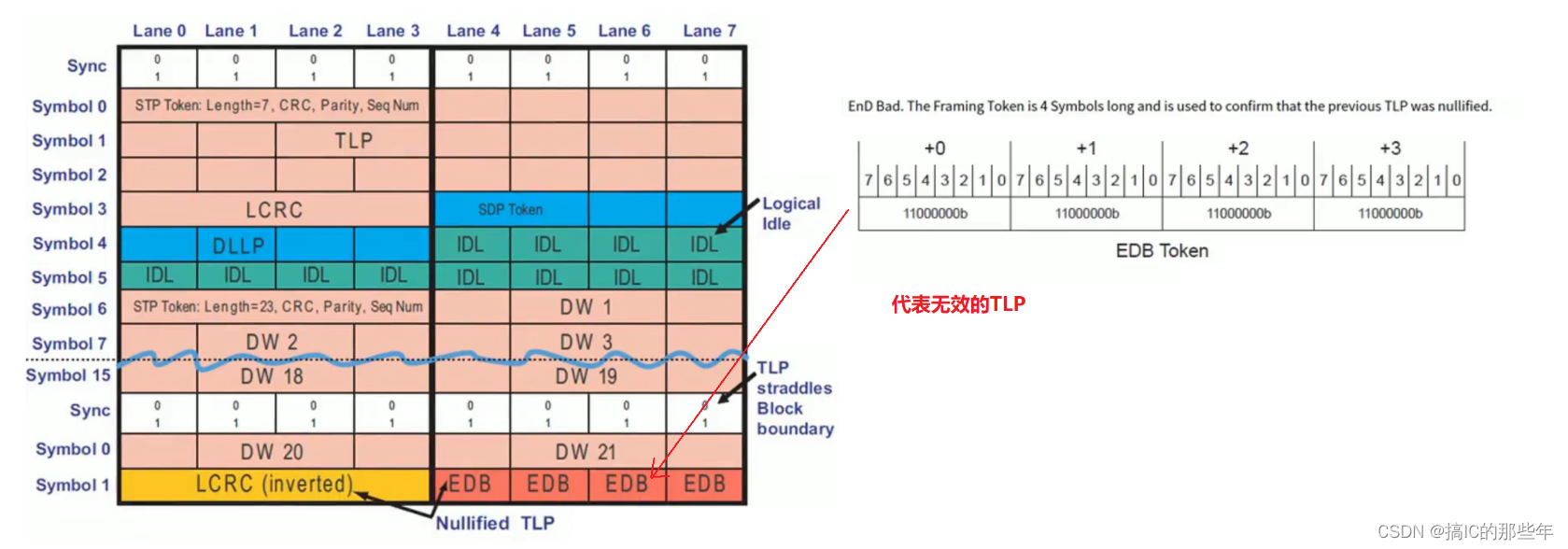

3、EDB坏包,我们假设第一个block的Symbol6是个坏包,那么TLP末端就会加上EDB Token,表明此TLP已无效。

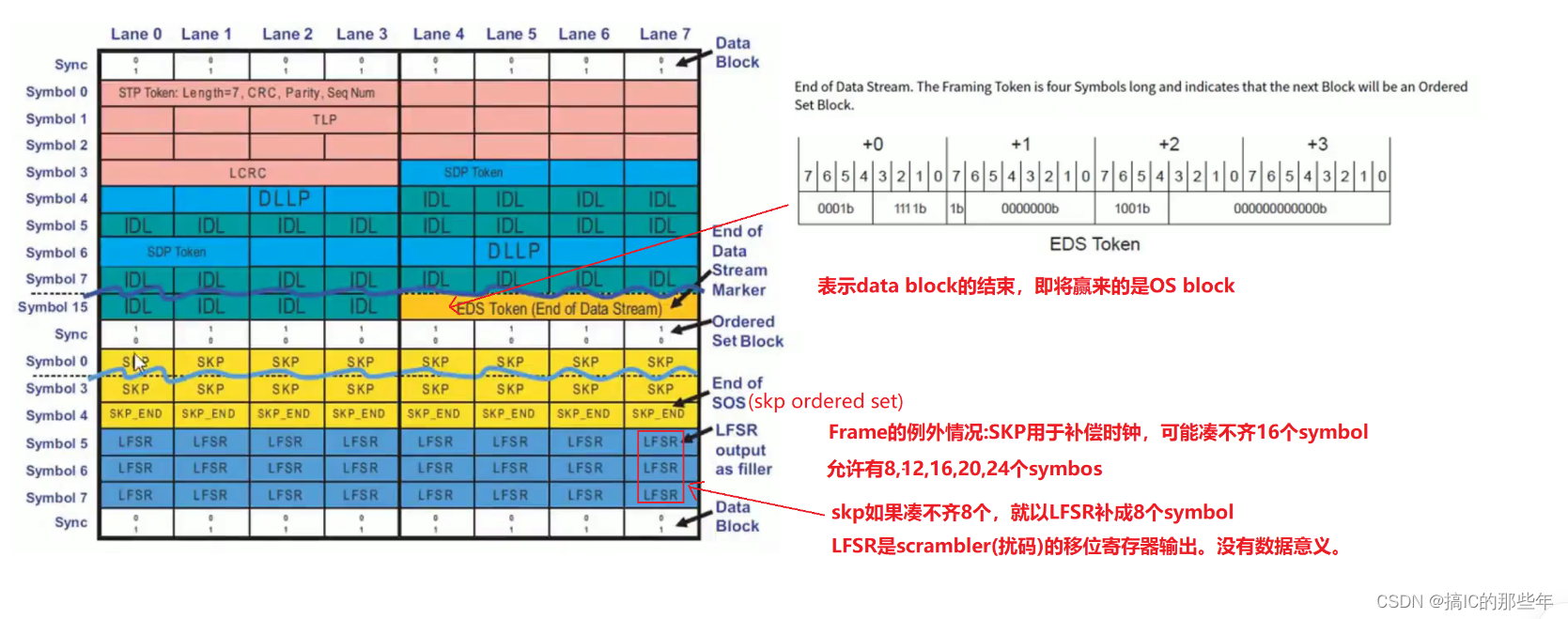

4、EDS:分割Data block和OS block。EDS代表一个Datablock的结束,接下来的是OSblock。

5、关于SKP OS(SOS),SOS允许一个block不足16或多于个symbol。可以有8,12,16,20,24个。如果凑不齐最小值8的话,就要用LFSR补全,LFSR是扰码移位寄存器的直接输出没有数据意义。

968

968

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?