摘要:PCIE——第 8 章——PCIe 总线的链路训练与电源管理

目录

第 8 章 PCIe 总线的链路训练与电源管理

8. 1 PCIe 链路训练简介

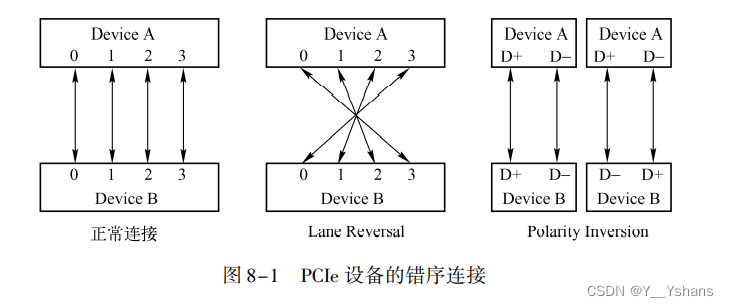

PCIe 总线进行链路训练的主要目的是初始化 PCIe 链路的物理层、 端口配置信息、 相应的链路状态, 并了解链路对端的拓扑结构, 以便 PCIe 链路两端的设备进行数据通信。

PCIe 总线提供这些连接方式的主要目的是为了方便 PCB 走线, 因为差分信号要求在 PCB 中等长而且等距。

所谓的Lane,是指一组差分信号的组合,包括发送和接收。一个发送方向的差分信号包括TX+和TX-两条线,接收亦然。所以一条lane有四条物理连线。发送和接收是同时进行的,故为全双工。

所谓的Link,是指两个PCIe部件的链接,通常是由端口和lane组成。(通常有多条lane)比如我们有一个X2的链路,意思是指这条链路是两条lane组成,一共8条物理连线。链路上传送的是编码之后的数据,比如Gen1/Gen2所采用的8b/10b编码,Gen3之后改成了128b/130b编码。Link初始化以及link建立过程(或者称之为链路训练,Link Training)是在设备上电或者链路重新建立链接是发生的。

8. 1. 1 链路训练使用的字符序列

PCIe 总线进行链路训练时, 需要发送一些特殊的字符序列 (Ordered⁃Sets),有的书籍也将这 些 Ordered⁃Sets 称为 PLP, 即物理层报文。

● Training Sequence 1 和 2, 简称为 TS1 和 TS2 序列。 这两种 PLP 在链路训练的多个状态 机中使用, 下文将进一步介绍这两种字符序列。

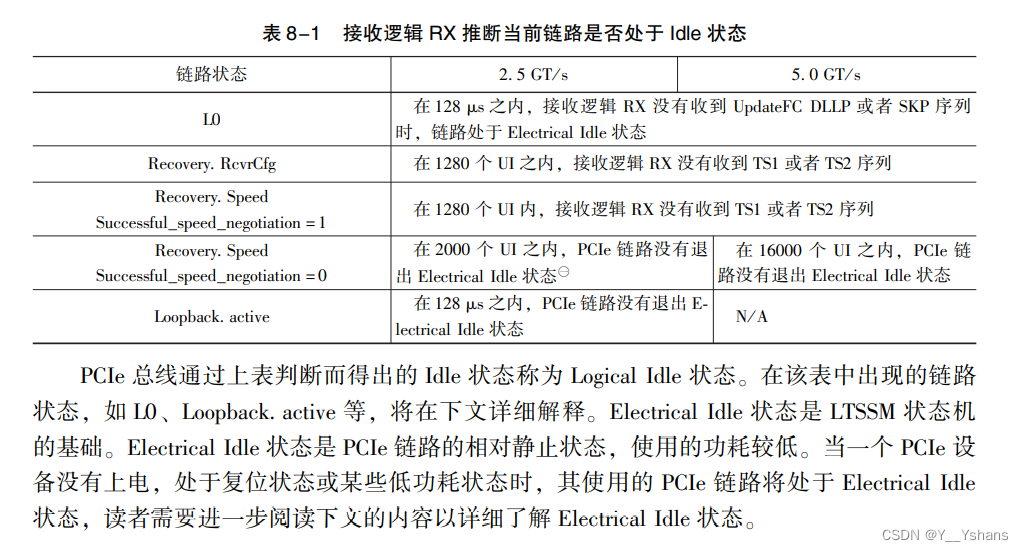

● Idle 序列。 在正常情况下, 发送端进入 Electrical Idle 状态时, 将首先向对端发送若干 Idle 序列, 才能进入。 Electrical Idle 状态是 PCIe 链路的一个低功耗状态, 第 8. 1. 2 节 将详细介绍该状态。

● Fast Training Sequence, 简称为 FTS。 该字符序列协助接收逻辑获得 Bit / Symbol Lock, 接收逻辑需要获得多个 FTS 后, 才能确定 Bit / Symbol Lock。

● SKIP 序列。 该字符序列的主要作用是进行时钟补偿。

8. 1. 2 Electrical Idle 状态

8. 1. 3 Receiver Detect 识别逻辑

Reciever Detect 识别逻辑的主要作用是检测对端的接收逻辑 RX 是否正常工作, Receiver Detect 识别逻辑是发送逻辑 TX 的一部分。

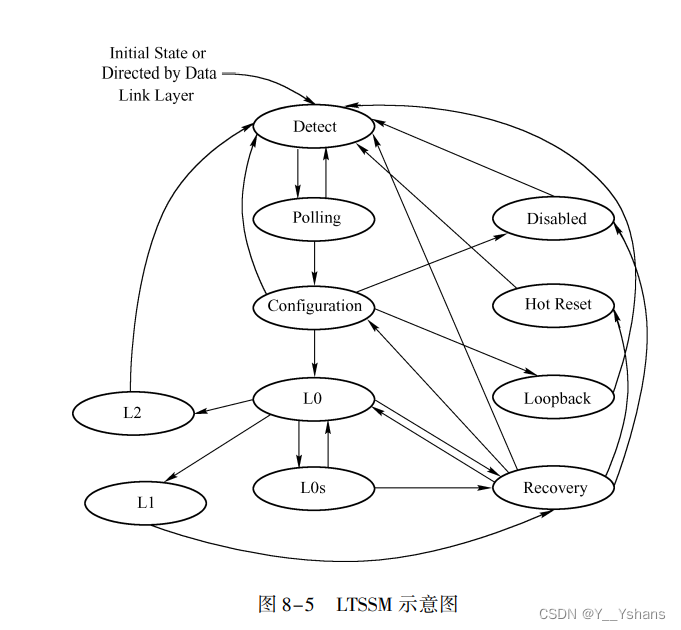

8. 2 LTSSM 状态机

PCIe 总线在进行链路训练时, 将使用 LTSSM 状态机。

● Detect 状态。 当 PCIe 链路被复位或者数据链路层通过填写某些寄存器后, LTSSM 将 进入该状态。 该状态也是 LTSSM 的初始状态。 当 PCIe 链路处于该状态时, 发送逻辑 TX 并不知道对端接收逻辑 RX 的存在, 因此需要使用 Receiver Detect 识别逻辑判断对 端接收逻辑 RX 是否可以正常工作, 之后才能进入其他状态。

Detect 状态由 Detect.Quiet、 Detect.Active 两个子状态组成。P231

● Polling 状态。 当 PCIe 链路进入该状态时, 将向对端发送 TS1 和 TS2 序列, 并接收对 端的 TS1 和 TS2 序列, 以确定 Bit / Symbol Lock、 Lane 的极性。 PCIe 链路处于该状态 时, 将进行 Loopback 测试, 确定当前使用的 PCIe 链路可以正常工作。

Polling 状态由 Polling.Active、 Polling.Compliance 和 Polling.Configuration 子状态组 成。P232

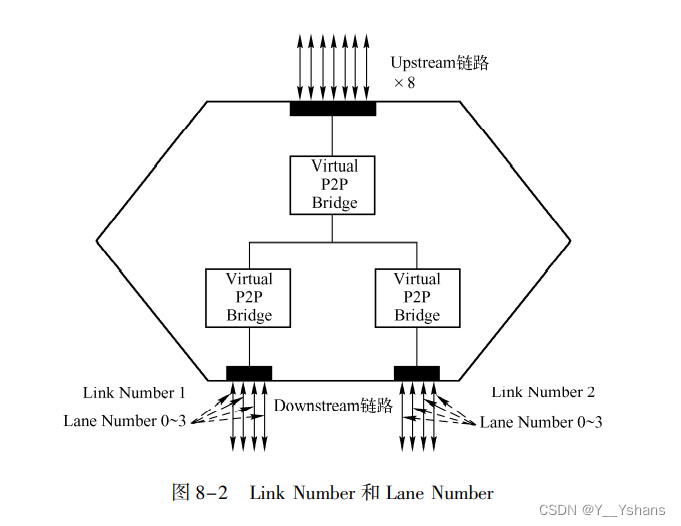

● Configuration 状态。 当 PCIe 链路进入该状态时, 将确定 PCIe 链路的宽度、 Link Number、 Lane reversal、 Polarity inversion 和 Lane⁃to⁃Lane 的延时。 该状态是 LTSSM 状态机最重要 的状态。 值得注意的是 PCIe 链路在进行初始化时, 链路两端统一使用 2. 5GT / s 的数据 传送率, 直到进入 L0 状态。

Configuratoin 状态是 LTSSM 的重要状态, 该状态完成 PCIe 链路的主要配置工作, 包括 Link Number 和 Lane Number 的协商, 并使 PCIe 链路进入正常工作状态 L0。P235

● L0 状态。 PCIe 链路的正常工作状态。 PCIe 链路可以正常发送和接收 TLP、 DLLP 和 PLP。 PCIe 链路可以从该状态进入 Recovery 状态, 以改变数据传送率。

● Recovery 状态。 PCIe 链路需要进行链路重训练时需要进入该状态。 该状态是 LTSSM 状态机的重要状态。

● L0s、 L1 和 L2 状态。 PCIe 链路的低功耗状态, 其中 PCIe 链路处于 L0s 状态时, 使用 的功耗相对较高, 而处于 L2 状态时, 使用的功耗最低。 ● Disabled 状态。 系统软件可以通过设置寄存器, 使 PCIe

● Disabled 状态。 系统软件可以通过设置寄存器, 使 PCIe 链路进入 Disabled 状态。 当 PCIe 链路的对端设备被拔出时, LTSSM 也需要进入该状态。

● Loopback 状态。 PCIe 链路进入该状态时, 发送端口将转发其接收端口接收到的数据, PCIe 测试仪器可以利用该状态进行数据测试。

● Hot Reset 状态。 当处理器系统进行 Hot Reset 操作时, PCIe 链路将进入 Recovery 状态, 然后进入 Hot Reset 状态进行 PCIe 链路的重训练。

LTSSM 的各个状态将在下文详细介绍, 本章将重点介绍 Detect、 Polling、 Configuration、 L0 和 Recovery 状态, 囿于篇幅并不对 Disabled、 Loopback 和 Hot Reset 状态进行详细说明, 对这些状态有兴趣的读者可以参阅 PCIe 总线规范, 以获得进一步信息。

PCIe 设备的物理层进行复位后, LTSSM 状态机首先沿着 “ Detect” → “ Polling” → “Configuration” → “L0” 的路径进入到正常工作状态 “L0” , 这也是链路训练的正常工作路 径, 也是最重要的一条路径。

8. 2. 5 LTSSM 的其他状态

如图 8 - 5 所示, 在 LTSSM 中还含有 Disabled、 Host Reset、 Loopback、 Recovery、 L0、 L1、 L2 和 L0s 状态。 其中 L0、 L1、 L2 和 L0s 与 PCIe 的电源管理相关, 在第 8. 3 节将详细 介绍这些状态的转换关系。 PCIe 链路还可以从 Configuration 和 Recovery 状态进入 Disabled 状态。 当系统软件需要关 闭 PCIe 链路时, 可以通过设置 Link Control 寄存器的 Link Disabled 位, 使 PCIe 链路进入 Dis⁃ abled 状态。 物理层进入 Disabled 状态时, 将禁止 PCIe 链路的使用, 然后视情况进入 PCIe 链路的初始状态 Detect, 重新进行 PCIe 链路的训练工作。 而 Loopback 状态是一种调试状态, PCIe 总线测试仪器可以使 PCIe 链路的对端设备进入 该状态, 然后对 PCIe 链路进行测试。 Hot Reset 状态从 Recovery 状态进入, 当系统软件对 PCIe 链路进行 Hot Reset 操作时, PCIe 链路将进入该状态, 然后进入 PCIe 链路的初始状态 Detect。

8. 3 PCIe 总线的 ASPM

PCIe 总线的电源管理包含 ASPM 和软件电源管理两方面内容。 所谓 ASPM 是指 PCIe 链 路在没有系统软件参与的情况下, 由 PCIe 链路自发进行的电源管理方式。 而软件电源管理 指 PCI PM 机制, PCIe 总线的软件电源管理与 PCI 总线兼容。

8. 3. 1 与电源管理相关的链路状态

PCIe 总线定义了一系列与电源管理相关的链路状态。

● L0 状态。 PCIe 设备的正常工作状态。

● L0s 状态。 PCIe 设备处于低功耗状态。 系统软件不能控制 L0 状态和 L0s 状态间的迁 移过程, 这两个状态的迁移只能由 ASPM 控制。

● L1 状态。 PCIe 设备使用的功耗低于处于 L0s 状态时的功耗。

● L2 / L3 Ready 状态。 PCI 设备进入 L2 或者 L3 状态之前使用的过渡状态。

● L2 状态。 PCIe 设备仅使用辅助电源工作, 主电源已经被关闭。 在 PCIe 总线中 L1 和 L2 状态是可选的。

● L3 状态。 该状态也被称为 “ Link off” 状态, 此时 PCIe 设备使用的 Vcc 电源已经被 关闭。

● LDn 状态。 该状态是一个 “伪” 状态, PCIe 链路处于 L2、 L3 状态时, 需要通过 LDn 状态之后才能进入 L0 状态。 该状态由 LTSSM 状态机的 Detect、 Polling 和 Configuration 等状态组成。 这些与电源管理相关的状态机迁移模型如图 8-11 所示。

P244

8. 4 PCI PM 机制

PCIe 总线与 PCI 总线使用的 PCI - PM 管理机制兼容。

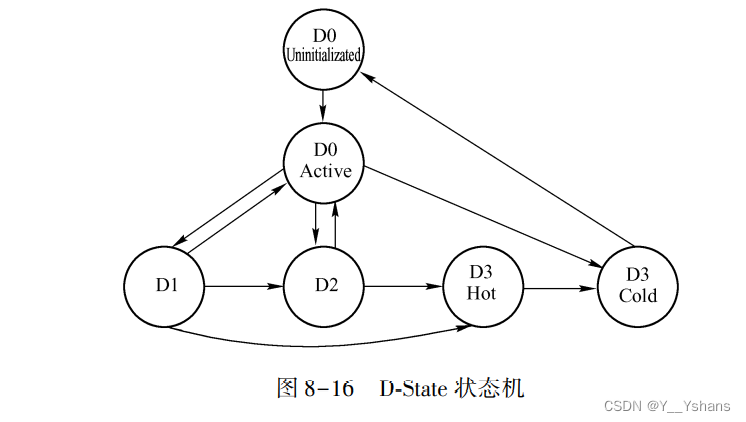

系统软件通过修改 PMCSR 寄存器的 Power State 字段, 可以使 PCIe 设备进入不同的节能 状态 D⁃State, 如 D0、 D1、 D2 和 D3 状态。 其中 D0 是正常工作状态, 功耗最高, 而 D1、 D2 和 D3 为低功耗状态。 其中 D1 的休眠等级最低, 功耗相对较高, 而 D3 的休眠等级最高, 功 耗相对较低。 D - State 的状态转换关系如图 8-16 所示。

8. 5 小结

本章重点介绍 PCIe 总线的 LTSSM 状态机, 该状态机的迁移模型较为复杂。 本章仅介绍 了该状态机的基本工作路径, 对此部分有兴趣的读者可以阅读 PCIe 总线规范, 进一步了解 相关内容。 LTSSM 状态机在 PCIe 总线规范中处于核心地位, 深入理解该状态机的运转模型, 有利 于底层软件工程师深入理解 PCIe 设备的工作状态, 从而开发出质量较高的程序。 本章还使用一定篇幅介绍了 PCIe 总线的电源管理模型。 目前电源管理已经成为计算机 体系结构的热点。 一个合理的电源管理模型需要软硬件的共同参与, 但是硬件设计仍然决定 了电源管理模型的节电效率。

参考文章:

PCI_Express_体系结构导读——王齐

99

99

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?