一 本章节主讲知识点

1.1 Polarity Inversion 极性反转

1.2 Lane Reversal 通道翻转

二 本章节原文翻译

2.1 极性反转

原文摘录:

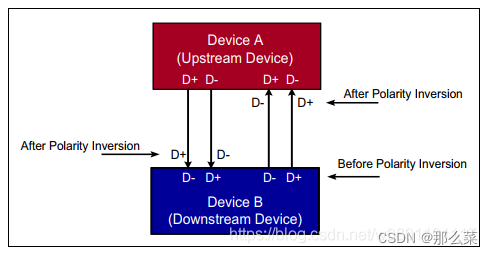

PCIe 协议规定,必须支持该特性。该特性的目标是为了简化 PCB 的布线。每个 lane 都包含一组发送(Tx)和接收(Rx),而 Tx 和 Rx 分别包含两根差分信号线(D+ 和 D-)。Polarity Inversion 的作用就是把某个设备的 D+ 变成 D-,D- 变成 D+。

开启 Polarity Inversion 之后的效果如下图所示:如果没有该特性,那么PCB 布线的时候,必须进过穿孔的方式,解决交叉线的问题,穿孔布局会对信号质量带来验证影响。

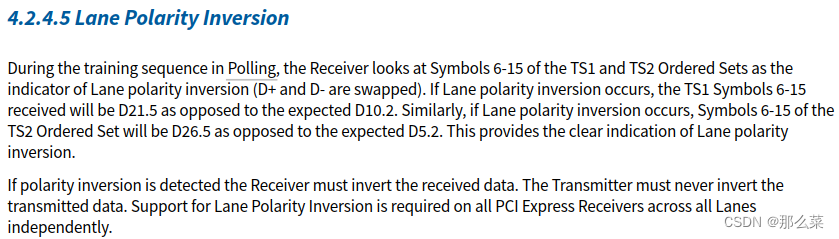

为了实现D+和D-正负极检测,接收逻辑Rx需要查看接收到的TS1或TS2中的Symbol 6~15(这里注意:接收RX逻辑检查接收到的TS1/TS2中Symbol 6~15, 这块功能实现可以放在PHY,也可以放在MAC 控制器):如果在TS1中接收到的是D21.5而不是D10.2,或者在TS2中接收到的是D26.5而不是D5.2,那么该Lane的极性就被反转了,必须被纠正。

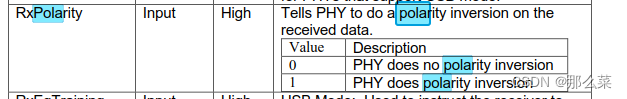

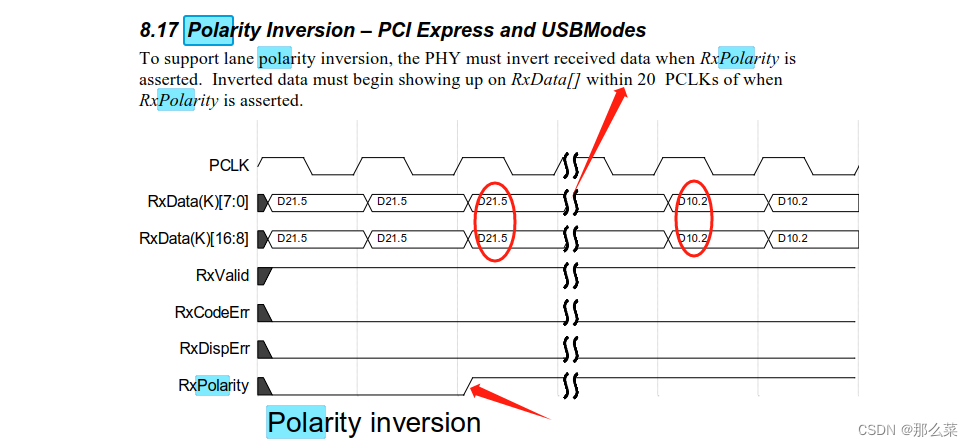

下图展示了,一种基于PIPE 接口实现MAC和PHY互联的接口图,可见:PIPE 接口提供一根信号线 RxPolarity , 来控制PHY 实现接收数据的翻转。

RxPolarity 信号拉高之后,20个PCLK 周期之后,PHY送给MAC的数据,必须是经过极性反转之后的数据。

话到此,简单总结并理解:发送D+和接收D+具有约定一致的模拟电路电气特性,发送D-和接收D-也具有约定一致的模拟电路电气特性。如果不按照D+对接D+ ,D-对接D-, 那么接收数据将会错误。

极性反转就是应对这种场合需求的。

2.2 通道翻转

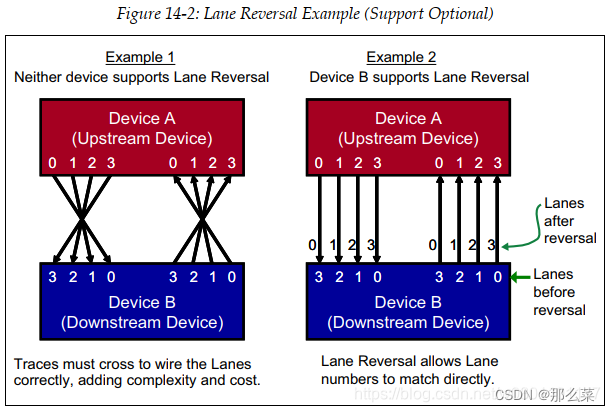

我们知道,PCIE设备通常是包含多个 lane 的设备,都是从 lane 0 开始顺序编号。一般情况下,两个 PCIe 设备相连时都是 lane 0 接 lane 0,lane 1 接 lane 1,以此类推。但是,有些场景中,为了简化 PCB 的布线,需要从逻辑上反转 lane 的编号,从而避免在 PCB 交错布线。只要一个设备支持 Lane Reversal 就可以。首先,一个设备在内部反转 lane 的编号,然后在链路训练时会检测到 lane 编号被反转。鉴于 Lane Reversal 并不是 PCIe 协议规定必须支持的特性,所以硬件设计人员在设计板级电路时需要确认 PCIe 发送设备或者接收设备的其中一个支持 Lane Reversal 特性之后才能按照非交错方式布线。

下图展示了 Lane Reversal 的效果:

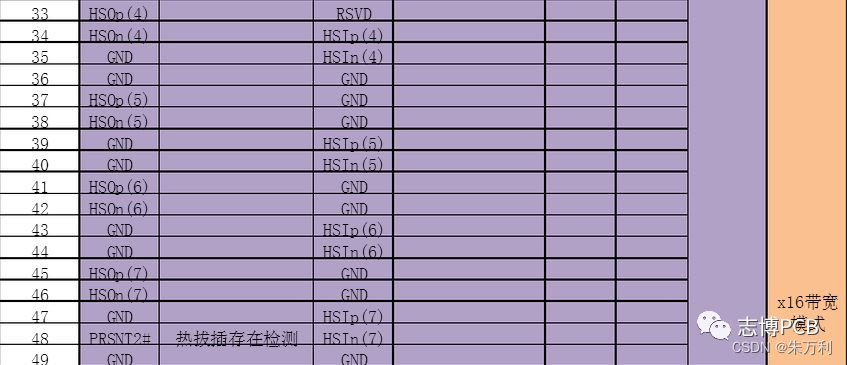

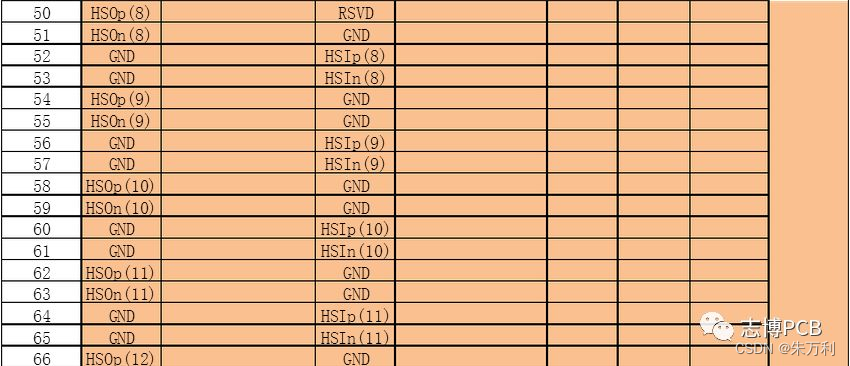

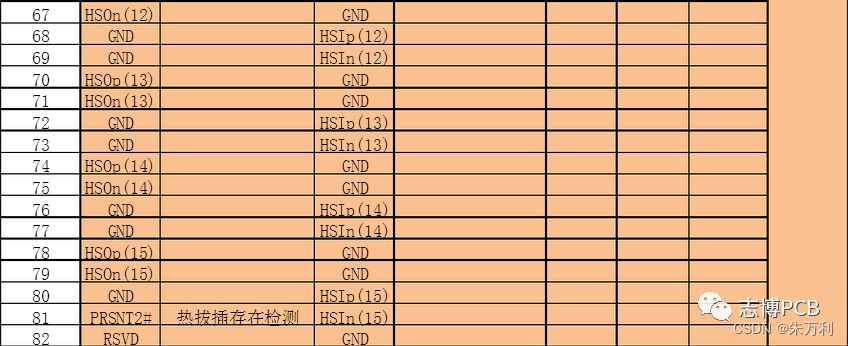

那我们看看实际金手指的信号排布是怎么样的。下图展示了PCIEx1/2/4/8/16 金手指AB两面管脚的分布名称。

可以发现,差分通道的顺序排布,也:通道0,通道1,通道2,以此类推。但是实际PCB 布线的时候,因为种种原因,两个互联通道不肯能完全按照同一个方向进行布局放置。对于这种情况,我们就需要使用PCIE 的 通道翻转特性。

三 本章节关联知识点

3.1 差分信号

由于PCI-E传输的信号是差分信号,所以这里有必要讲解一下差分线的定义:

相位信号和单端信号对比:传统的单端信号通过相对于地线的电势差的高低来传递,所以只需要一根地线就可以,传递几路信号只需要相应数量的信号线就可以了;而差分信号使用一根公共地线(电势为0),传输一路信号时,需要两根信号线,一根相对于地线的电压是正的(电势为正),另一根电压为负的(电势为负),绝对值相同(相位相差180度),用两根信号线的电势差高低来传递信号,只不过传递两个信号,假如一根信号线为3.3V,另一根信号线就是-3.3V,地线是0。这种看似浪费线的传输方式其实有很多优势:第一,因为地线是可以控制的,所以不会因为线长带来的压降而导致地线的差异,进而可以降低传输的电压来降低功耗(早期的AGP 2X的工作电压高达5V,而现在的PCI-E已经低于1.5V了);第二,因为电磁干扰对差分信号两根信号线的影响几乎相同,即使有干扰,高电势依然相对于低电势高,而单端信号则可能因为干扰而将低电势变成高电势,导致传输错误,因此差分信号抗干扰性强。现在,大多数高速串行接口都采用了差分信号,比如USB3.0/3.1、PCI-E、HDMI、以太网等。

————————————————

292

292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?