问题描述:

运行【File】-》【Launch SDK】,进度条前进一点就闪退了

思路:

①可能是后台残余sdk进程,重启即可

②可能是某处的sdk缓存导致的问题,需要清除缓存

问题解决:

方法一:

重启电脑,重启SDK

方法二:

①将【工程.sdk】重命名为【任意其他名称】,相当于清除缓存

②导出硬件

【File】-》【Export】-》【Export Hardware】

③运行sdk

【File】-》【Launch SDK】

//此步vivado会自动新建【工程.sdk】目录

④复制

进入刚才重命名的sdk文件夹,复制工程内容到新的【工程.sdk】

⑤导入

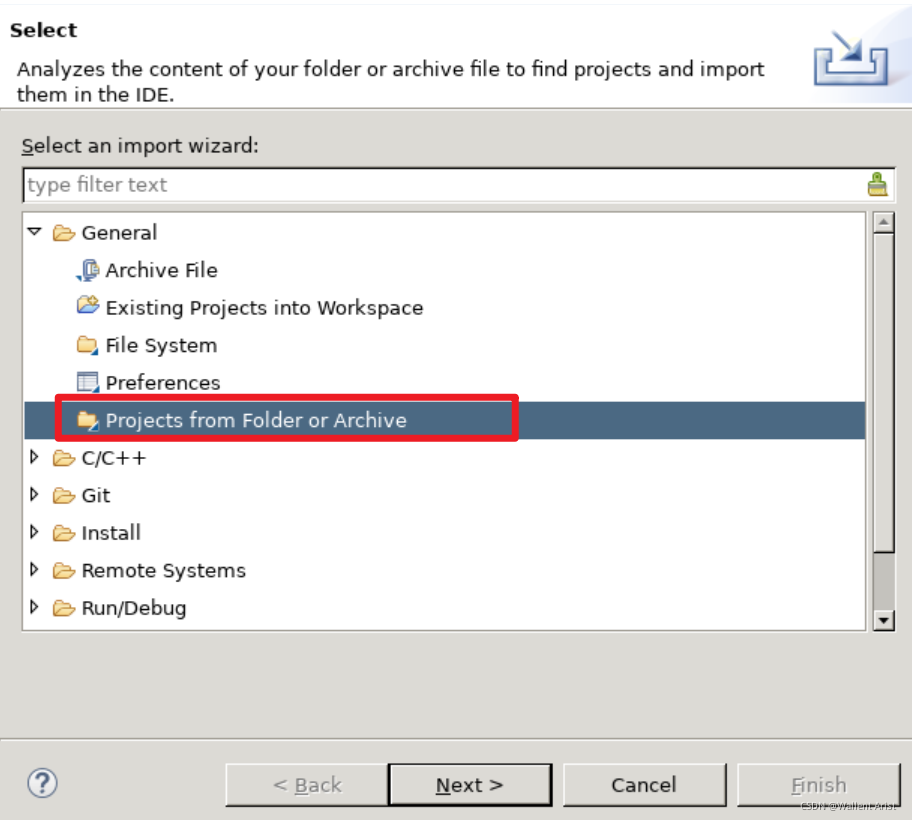

- 【File】-》【Import】-》【General】-》【 Projects from Folder or Archive】

- 选择【工程.sdk】目录,导入需要的文件夹或源码

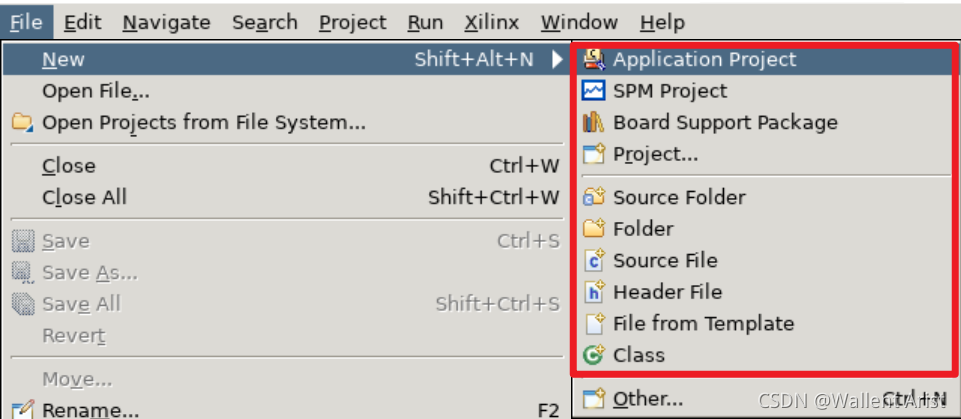

⑥重建工程 - 对于fsbl及bsp等,因为重新导入硬件,故建议新建,名称需要跟之前一致

- 【File】-》【New】-》【Application Project】

- 【File】-》【New】-》【Board Support Package】

⑦重编译

工程【右键】-》【Clean Project】

6854

6854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?