1.1 Introduction

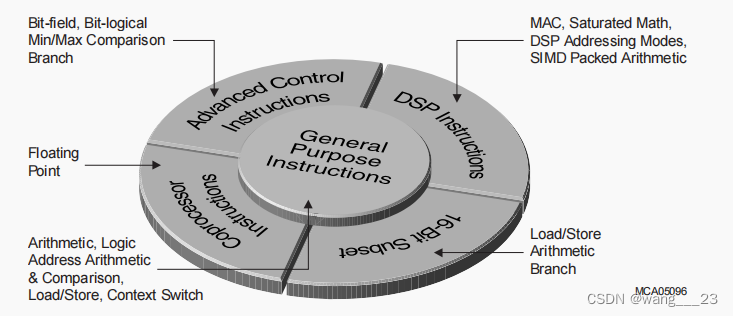

TriCore是第一个针对实时嵌入式系统优化的统一的单核32位微控制器- dsp架构。TriCore指令集架构(ISA)结合了微控制器的实时能力,DSP的计算能力以及RISC加载/存储架构的高性能/价格特征,在一个紧凑的可重新编程核心中。

ISA支持统一的32位地址空间,具有可选的虚拟寻址和内存映射I/O。该体系结构允许广泛的实现,范围从标量到超标量,并且能够与不同的系统体系结构进行交互,包括多处理。实现和系统级别的这种灵活性允许在任何时间点在性能和成本之间进行不同的权衡。

该架构支持16位和32位指令格式。所有指令都是32位格式。16位指令是32位指令的一个子集,选择它们是因为它们的使用频率。这些指令显著减少了代码空间,降低了内存需求、系统和功耗。实时响应在很大程度上取决于中断延迟和上下文切换时间。高性能架构通过避免长多周期指令和提供灵活的硬件支持的中断方案来最大限度地减少中断延迟。该体系结构还支持快速上下文切换。

1.1.1 Feature Summary

TriCore指令集架构(ISA)的主要特点是:

32位架构

4GBytes的地址空间

16位和32位指令用于减少代码大小

在一个周期内执行的大部分指令

分支指令(使用分支预测)

低中断延迟与快速自动上下文切换使用宽路径片上存储器

专用接口特定于应用程序的协处理器,允许添加定制指令

零开销循环能力

双,单时钟周期,16x16位乘累加单元(可选饱和)

可选浮点单元(FPU)和内存管理单元(MMU)

广泛的位处理能力

单指令多数据(SIMD)打包数据操作(2 × 16位或4 × 8位操作数)

灵活的中断优先级方案

字节和位寻址

数据存储器和CPU寄存器的小端字节排序

内存保护

调试支持

1.2 Programming Model

1.2.1 Architectural Registers

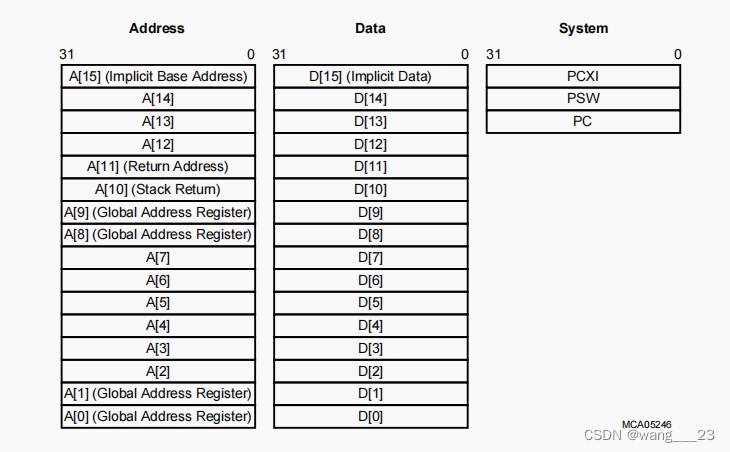

结构寄存器包括:

32通用寄存器(GPRs)

程序计数器(PC)

两个32位寄存器包含状态标志、先前执行信息和保护信息(PCX -先前上下文信息寄存器和 PSW -程序状态字)

PCXI, PSW和PC寄存器对于存储和恢复任务上下文的过程至关重要。

32个通用寄存器(GPRs)分为16个32位数据寄存器(D[0]到D[15])和16个32位地址寄存器(A[0]到A[15])。

四个通用寄存器亦有特别功能:

D[15]被用作隐式数据寄存器

A[10]是堆栈指针(SP)寄存器

A[11]是返回地址(RA)寄存器

A[15]是隐式地址寄存器

寄存器[0H - 7H]被称为“下寄存器”,寄存器[8H- FH]被称为“上寄存器”。寄存器A[0]、A[1]、A[8]、A[9]定义为系统全局寄存器。它们不包括在上层或下层上下文中,也不会跨调用或中断保存和恢复。它们通常被操作系统用来减少系统开销。除了通用寄存器(GPRS)外,核心寄存器还由一定数量的核心特殊功能寄存器(CSFRS)组成。

1.2.2 Data Types

该指令集支持以下操作:

布尔

位串

字节

带符号的分数

地址

有符号/无符号整数

IEEE-754单精度浮点

大多数指令处理特定的数据类型,而其他指令可用于操作多个数据类型。

1.2.3 Memory Model

该架构可以访问高达4GBytes(地址宽度为32位)的统一程序和I/O内存。地址空间被划分为16个区域或段[0H-FH],每个256 MBytes。地址的前四位选择特定的段。

1.2.4 Addressing Modes

寻址模式允许加载和存储指令有效地访问数据结构中的简单数据元素,如记录、随机和顺序访问的数组、堆栈和循环缓冲区。

TriCore架构支持七种寻址模式。简单的数据元素有8位、16位、32位和64位宽。这些寻址模式支持C/ c++程序的有效编译,易于访问外设寄存器和典型DSP数据结构的有效实现(用于滤波器的圆形缓冲区和用于快速傅里叶变换的位反转索引)。

硬件不直接支持的寻址模式可以通过短指令序列合成。

1.3 Tasks and Contexts

任务是一个独立的控制线程。有两种类型:软件管理任务(SMTs)和中断服务例程(ISRs)。

SMTs是通过实时内核或操作系统的服务创建的,并在调度软件的控制下进行调度。ISRs是由硬件响应中断而分派的。ISRs是处理器在接收到中断时直接调用的代码。SMTs有时被称为用户任务,假设它们在用户模式下执行。

根据任务的功能,为每个任务分配了自己的模式:

User-0模式:用于不访问外部设备的任务。该模式不能启用或禁用中断。

User-1模式:用于访问普通、未受保护的外设的任务。通常,这将是对串行端口的读或写访问,对定时器和大多数I/O状态寄存器的读访问。该模式下的任务可能会在短时间内禁用中断。(此模式的默认行为可能被系统控制寄存器覆盖)。

Supervisor模式:允许对系统寄存器和所有外围设备进行读写访问。该模式下的任务可能会禁用中断。

单个模式的启用或禁用主要通过处理器状态字(PSW)中的1/0模式位。

一组状态元素与任何任务相关联,这些元素统称为任务的上下文。上下文是处理器定义关联任务的状态并允许其继续执行所需的一切。这包括任务使用的CPU通用寄存器、任务的程序计数器(PC)及其程序状态信息(PCXI和PSW)。该体系结构通过硬件有效地管理和维护任务的上下文。上下文又被细分为上层上下文和下层上下文。

上下文保存区域

该体系结构使用固定大小的上下文保存区域(CSA)的链表。CSA由16个字的内存存储组成,按16个字的边界对齐。每个CSA只能包含一个上层或下层上下文。CSA通过链接字连接在一起。该架构比传统的微处理器和微控制器更快地保存和恢复上下文。具有宽数据路径的独特内存子系统设计允许该架构在处理器寄存器和片上存储器之间执行快速数据传输。当事件或指令导致程序执行中断时,就会发生上下文切换。然后,CPU需要在继续执行程序之前解析此事件。

导致程序执行中断的事件和指令有:

中断或服务请求

陷阱(TRAP)

函数调用

1.4 Interrupt System

该架构的一个关键特点是其强大而灵活的中断系统。中断系统是围绕可编程服务请求节点(srn)构建的。

服务请求被定义为中断请求或DMA(直接内存访问)请求。服务请求可能来自片上外设、外部硬件或软件。

传统的体系结构通常需要很长时间来处理中断请求,并且通常通过从数据内存中的向量表加载新的程序状态(Program Status, PS)来处理。在TriCore体系结构中,服务请求跳转到代码内存中的向量以减少响应时间。ISR的入口代码是代码块向量中的一个块。每个代码块为一个中断源提供一个入口。

1.4.1 Interrupt Priority

服务请求有优先级,优先级允许嵌套中断。

优先级的规则是:

服务请求可以中断低优先级

中断的服务具有相同优先级的中断源不能相互中断

中断控制单元(Interrupt Control Unit, ICU)根据优先级号决定哪个源将赢得仲裁。

所有的业务请求都被分配了优先级号(SRPNs)。每个ISR都有自己的优先级号。不同的服务请求必须分配不同的优先级号。

中断源的最大数目为255。可编程选项的范围从一个优先级255个源,到255个优先级,每个源一个。

假定中断号是按照中断优先级的线性顺序分配的。这是可行的,因为中断号不是硬连接到单个源,而是由上电引导序列期间执行的软件分配的。

1.5 Trap System

trap是由于诸如不可屏蔽中断(NMI)、指令异常或非法访问等事件而产生的。TriCore架构包含八个陷阱类,这些陷阱进一步分为同步或异步、硬件或软件。每个trap都被分配了一个trap识别号(TIN),用于识别其类中的trap原因。陷阱处理程序的入口代码由代码块向量组成。每个代码块为一个陷阱提供一个条目。当捕获到一个陷阱时,TIN被放入数据寄存器d[15]中。

陷阱类是:

内存管理单元(MMU)

内部保护

指令错误

上下文管理

系统总线和外设

断言的陷阱

系统调用

不可屏蔽中断(NMI)

1.6 Protection System

TriCore支持的领域之一是安全关键型嵌入式应用程序。该架构的特点是一个保护系统,旨在保护核心系统功能免受不太关键的应用程序任务中软件错误的影响,并防止未经授权的任务访问关键的系统外围设备。

保护系统也便于调试。它检测和捕获错误,否则这些错误可能会被忽视,直到发现错误的原因时为时已晚。

整个保护系统由四个主要子系统组成:

1. 陷阱系统。

2. I/O特权级别:TriCore支持三种I/O模式:User-0模式、User-1模式和Supervisor模式。User-1模式允许应用程序任务直接访问非关键系统外设。这使得嵌入式系统可以高效地实现,而不会失去在Supervisor模式下运行所有内容的常见做法所固有的安全性。(User-1模式的默认行为可能被系统控制寄存器覆盖)。

3.内存保护系统:这个保护系统可以控制一个任务可以访问的内存区域,以及允许访问的类型。

4. 时间保护系统。这个保护系统提供了防止运行时超时的保护。

1.7 Memory Management Unit

TriCore可以使用可选的内存管理单元(MMU)。当配置MMU时,内存空间有两个寻址区域;物理的和虚拟的。每个实例的物理和虚拟地址空间为4GBytes,每个4GBytes被分成16个256MByte的段。

段[8H-FH]绕过虚拟映射,直接在物理上使用。段[0H-7H]在MMU存在并使能时由MMU虚拟映射,在MMU不存在或使能时由MMU物理映射。

在访问内存之前,虚拟地址总是被转换成物理地址。根据MMU模式和虚拟地址区域的不同,这种对物理地址的转换可以是直接转换,也可以是页表项(PTE)转换。

直接翻译

如果虚拟地址位于虚拟地址空间的上半部分,则直接使用该虚拟地址作为物理地址。如果虚拟地址位于地址空间的下半部分,并且处理器工作在物理模式,则间接使用虚拟地址作为物理地址。

PTE

如果处理器工作在Virtual模式,并且虚拟地址位于地址空间的下半部分,则使用PTE对虚拟地址进行转换,即将虚拟地址的VPN (Virtual Page Number)替换为PPN (Physical Page Number),从而获得物理地址。

1.8 Core Debug Controller

核心调试控制器(CDC)旨在支持需要非侵入式调试的实时系统。CPU内核和内核片上存储器中的大多数架构状态都可以通过系统地址映射访问。调试功能是体系结构、实现和软件工具的接口。

对CDC的访问通常通过包含CPU的系统的片上调试支持(OCDS)提供.

1.9 TriCore Coprocessor Interface

TriCore实现可以选择实现协处理器接口。这样的接口允许硬件扩展到标准的TriCore指令集。

775

775

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?