- 博客(65)

- 资源 (3)

- 收藏

- 关注

原创 adb不是内部或外部命令

Windows版本:https://dl.google.com/android/repository/platform-tools-latest-windows.zip。Linux版本:https://dl.google.com/android/repository/platform-tools-latest-linux.zip。Mac版本:https://dl.google.com/android/repository/platform-tools-latest-darwin.zip。...

2022-08-16 10:54:49

1062

1062

原创 Orcad Captue原理图更改后同步更新到Allegro PCB

Cadence软件的原理图和PCB是两个软件,原理图到PCB需要创建网表,然后在PCB中放置已经建好分封装的元器件;如果对于已经画好的PCB,后期发现需要更改原理图的某个部分,原理图更改后,怎么同步更新到PCB中,而不变动原来已经布好局、布好线的的PCB呢?1、打开原理图,点击选中下打开的DSN文件,点击Tools中的Create Netlist,点击确定,创建成功后,output下输出的就是三个网表文件2、网表创建成功后,回到Allegro PCB的页面,点击File中Import Logic;如

2021-09-30 21:05:29

12722

12722

4

4

原创 笔记本与台式机文件夹、磁盘共享

目的:台式机想要直接拷贝或者编辑笔记本某个磁盘和文件夹的内容;操作步骤如下所示(以Win10操作为例):1、设置中打开网络共享中心:注意:只有两台电脑通过网线连接才有上述标志。2、进入协议版本4点击属性:3、填入IP地址,如下图所示,点击确定:4、上面设置的是笔记本的,同样的方法设置台式机的IP地址;台式机的IP地址:192.168.1.3(与笔记本IP最后一位相差1).5、设置完成后,可以共享文件了:右键磁盘或者文件夹,进入属性-共享-高级共享-打开权限;6、共享后,回到另一台台式机

2021-09-17 16:16:37

8508

8508

2

2

原创 cadence allegro打不开brd文件,出现下述错误:

cadence allegro打不开brd文件,出现下述错误:WARNING(SPMHA1-230): Database has a non-recoverable corruption. Contact Cadence Customer Support with the design file and the details of the last steps performed.解决办法:一般情况不是有软件版本错误引起的,画PCB重新database check另存为保存下就可正常打开了...

2021-09-02 17:46:06

5805

5805

原创 excel单元格做下拉列表以及改变下拉列表的字体

选中单元格后(也可以同时选择很多个单元格),点击数据验证,如下图所示,在数据验证中的“允许”中选择序列,“来源”中选择要下拉的选项,如是和否;注意中间一定要用英文的逗号;如下图所示效果如下图所示:如果想清除下拉列表中的各个选项,选择单元格后仍然点击数据验证,全部清除即可,如下图所示:如果想对下拉列表中的“是”和“否”的字体大小和颜色进行修改,怎么操作呢?如下图所示,可以在条件格式中定向选择下拉列表中某个字体样式。...

2021-08-13 19:25:02

7319

7319

原创 电脑触摸屏无法使用、失灵解决办法

以我的笔记本电脑为例,出现了触摸板无法使用的情况,解决办法:打开电脑设置,找到触摸板,如下图所示,看是否关闭如果这里打开了,仍然发现无法使用触摸屏,尝试按下电脑的F9键(或者Fn+F9),一般情况下在电脑不出现驱动程序丢失或者损坏的情况下都可以解决。...

2021-08-02 09:19:56

23483

23483

1

1

原创 硬件找工作笔试题、面试题,求职offer指导规划

硬件求职找工作笔试题、面试题;拿offer指导规划:https://www.bilibili.com/video/BV1Cb4y167TM

2021-07-21 21:56:50

230

230

原创 Allegro PCB布局布线时关闭地网络的飞线

有时我们在布局布线的时候为了查看方便,需要关闭某个网络的飞线,例如地网络,步骤如下所示:只打开网络:点击GND引脚的网络,出现如下图所示,选择No Rat,如下图所示:然后点击apply和OK...

2021-06-02 14:25:02

2256

2256

原创 Allegro PCB板框内缩一定距离时发现所选属性不是一个封闭的整体

在Allegro PCB布线的时候会有时会定义在一个板框内缩一定距离布线,正常操作步骤如下图所示:选中板框,发现提示如下图所示,不是一个闭环的整体可以发现没有正常内缩,这是由于板框不是一个封闭的整体:解决办法如下:打开颜色管理器,关闭所有,只打开板框所显示的层如下图所示按上述操作步骤后说明将其设置成了一个整体;然后,按正常内缩步骤进行操作即可...

2021-06-01 19:53:33

1351

1351

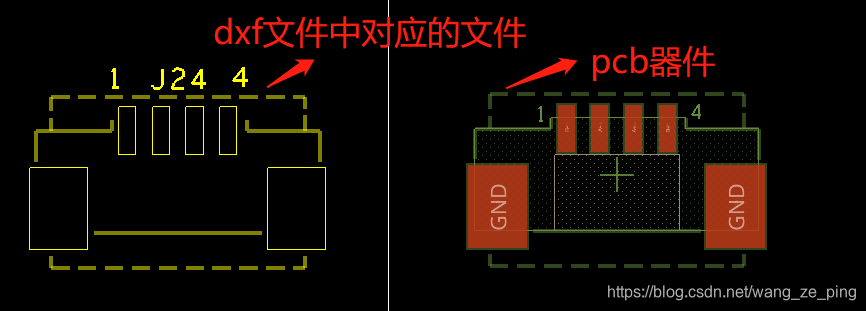

原创 Allegro pcb不规则器件与DXF文件对应位置对齐重合操作

上图中将右边的与左变的完全重合的操作:点击move命令(例如快捷键是m,按键m)鼠标

2021-06-01 17:22:58

2770

2770

原创 word中有时出现表或者图的注释与表或者图分页了

在word中有时出现上一页的注释与该注释的表或者图分开了,解决办法:将光标定位到注释,右键段落:

2021-03-05 16:56:54

1705

1705

原创 word中插入公式后,行与行的距离增加

有时需要在word中插入公式的或者公式相关的数学符号,但是插入后行与行之间的距离明显增大,如下图所示:解决办法:将光标定位到公式或者属性公式符号旁边,右键点击段落,

2021-03-05 16:53:24

1160

1160

原创 wps中的word删除空白页

在word中有时出现空白页,点击backspace或者delete键却无法删除掉该空白页,删除的还是上一页的内容。这一般由于是分页符造成的;点击下图中的显示编辑标记:找到空白页上面是否有分页符,删除掉即可...

2021-02-28 20:23:59

2079

2079

原创 Allegro PCB添加丝印信息以及对特点丝印text位号的改变

有时在PCB布局布线完成之后需要在某些位置注明正负极或者其他的信息:点击Add 中的Text,在options面板中信息如下图所示:这时并不能直接填写丝印text的相关信息,因为silkscreen的text信息是与器件symbol绑定在一起的,所以应该先点击与text相关的器件symbol,;点击之后输入想要的信息即可如下图所示:但是发现上述丝印的text较小,想改大点,点击setup中的design parameters,上图点击OK命令后,点击Edit中的change命令(或者自定义的快捷

2021-02-25 18:15:39

9903

9903

4

4

原创 Allegro PCB光绘(Gerber)文件的输出与打包

光绘层叠添加完成之后(https://blog.csdn.net/wang_ze_ping/article/details/114038167),就是Gerber文件的输出与打包上图中分别选择每一个,在上图右边方框中都填写一样的(注意如果是多层板,中间层的Plot mode选中的是Negative,其他的不变)在General Parameter中填写如下图所示:上述两步操作完成之后,如上图所示,点击创建光绘时出现了错误(可以参考这篇文章:http://blog.sina.com.cn/s/

2021-02-25 10:57:26

1372

1372

原创 Allegro PCB的光绘层叠的添加

重点:Gerber文件(光绘文件)需要的内容:1、线路层(多少层就添加多少层的线路,2层板添加2层的线路,4层板添加4层的线路等);2、阻焊(有阻焊的地方就不会盖绿油);3、钢网(贴片的时候需要钢网文件);4、丝印;5、钻孔在Allegro PCB中Gerber文件的输出首先需要添加光绘层叠一、点击Manufacturer中Artwork进入下图页面:本PCB文件是双层板,因此以双层板为例讲解光绘层叠的添加删除BOOTOM(原因手动添加自己所需要的文件,如果是多层板只留下TOP层,其他的

2021-02-24 21:51:43

4497

4497

原创 Allegro PCB放置mark点

点击Place中的Manually;打开之后勾选library,如下图所示:选择如下:放置制作好的mark点

2021-02-23 19:54:00

2290

2290

原创 Allegro PCB已经铺好铜的板子四周放置不带网络的定位孔

例如下图中边角想放置一个定位孔,可是四周已经铺好铜了,放置定位孔后就自动与地线连接起来了,怎么放置一个定位孔,又不与周围的任何网络连接起来呢?操作如下:可以放置一个圆形的禁布区域,点击下图中的箭头所指的圆形,在options面板中选择Route Keepout操作后的效果如下所示:...

2021-02-23 15:24:54

1401

1401

原创 Allegro PCB批量更改已经布局完毕后的元器件封装

PCB元器件所有元器件已经放置完毕,并且布局已经完成,但是布线的时候发现某些元器件的封装的引脚过大,需要更改symbol封装(注意不是更改pad,这个可以参考另一篇文章https://blog.csdn.net/wang_ze_ping/article/details/113568024);同时又不想更改原器件所处位置,操作方法如下:回到Orcad capture原理图编辑页面,右键原理图:在下图中的PCB封装栏填入已经重新做好的元器件封装的名字:保存后,点击同步按钮:(前提条件是原理图的layo

2021-02-22 10:04:18

3039

3039

原创 Allegro PCB对边框倒角变成圆弧处理

例如想对下述的矩形的边角变成圆弧状点击Manufacturer中的Fillet,如下图所示:在options面板中填写圆弧倒角的大小然后分别点击相邻line,效果如下所示:

2021-02-20 20:23:19

5874

5874

原创 Allegro PCB对line等对象进行换层

使用change命令,在Find面板中勾选对象,例如是line,在Options面板中的subclass中选择需要换层的对象:注意上述方法只是针对Class不变的前提下,只能改变subclass

2021-02-20 20:09:11

4437

4437

原创 Cadence制作flash焊盘时找不到

flash焊盘明明已经制作完成,但是在热风焊盘填写添加flash焊盘找不到:解决办法:打开PCB Editor 17.4,在setup中设置自己制作的flash symbol所保存的路径,如下图所示:关闭PCB Editor 17.4;重新打开制作焊盘的 软件Padstack Editor 17.4,,重新添加时就自动出现刚才的flash symbol:...

2021-02-19 19:53:45

1836

1836

原创 Route keepin rectangle already exists

在Allegro PCB布局布线的过程中有时需要在距板框边缘设置一定距离的禁布线区域;点击Edit中的Z-copy,界面如下图所示:在options面板中设置如下:上图中的Offset代表的是距版边框的距离为禁布线区域然后选中版边框,shape就自动内缩了10mil,如果出现下图中的显示:Route keepin rectangle already exists说明已经设置过了Route keepin,需要删除之前的,重新设置Route keepin一定的禁布区域...

2021-02-17 19:43:26

2598

2598

1

1

原创 Allegro PCB修改网络的名称

例如在布局布线的过程中某个地网络显示为0,如下图所示:如果想修改它的网络名称,例如修改为AGND;点击logic中的如下图所示:点击要修改的网络,重新命名Rename

2021-02-17 19:11:30

6631

6631

原创 Cadence Allegro PCB 17.4的叠层、正片和负片的设计

Allegro PCB17.4的叠层设计与之前的版本有些许不同,点击setup中的Cross-section后进入下页面:

2021-02-17 13:19:13

4577

4577

原创 Cadence 17.4 Allegro PCB批量取消所有高亮的网络

在PCB设计时,有时为了方便对一些网络进行不同颜色的高亮,如果想取消某个网络高亮,点击Dehilight后,直接点击引脚网络;如果想一下子取消所有已经高亮的网络,点击Dehilight(或者自定义的快捷键)后,在options页面点击All,如下图设置:...

2021-02-17 08:53:34

5523

5523

1

1

原创 Allegro PCB线布线已经连接,查看status状态显示没有连接

当我们某个引脚的网络已经连接上时,查看status时,发现并未连接,如下图所示:找到坐标显示的网络,如下图所示:重新连接一下知道上述的短线消失

2021-02-16 20:51:28

4342

4342

原创 Allegro PCB差分对的设置以及对差分对的驱动

差分对是指定:在PCB页面上方的面板中点击logic设置差分对,如下图所示:进入下图页面后,直接点击一对差分线的两个引脚的网络,然后点击Add上述差分线设置后并没有对其进行驱动;打开规则管理器中的All Layers,选中所有的差分对,右键创建类类名创建还没有指定差分规则,进入Physical Constraint Set中的All Layers,右键创建差分规则(例如阻抗为100欧姆,设置规则名为DIFF100,其中的线宽为6mil,差分对的间距为8mil,这些参数是通过阻抗计算工具SI9

2021-02-15 11:17:33

1910

1910

原创 Orcad Capture进行DRC检查出现 Net has two or more aliases

在进行DRC检查时,出现很多如下警告:双击警告回到原理图,出现上述警告的原因时网络名称与标号不相同(aliase本身的意思时别名),但是这并不影响原理图的绘制,解决办法,可以将接地的符号命名为GND等操作...

2021-02-14 12:41:40

6477

6477

原创 Orcad Capture进行DRC检查出现 More than one page is numbered 1

出现这样的错误是因为没有设置原理图总共多少页、第几页;双击原理图右下角的title,其中Page Count表示原理图总共有多少页,Page Number表示该原理图是第几页

2021-02-14 11:48:52

5772

5772

原创 Orcad Captue元件标号下方有一个横线

例如有时原理图的标号下方出现横线,如下图所示:这是由于画原理图的时候修改过标号,因此会出现下划线;消除办法,选中元器件,右键,设置如下图所示:

2021-02-14 10:13:23

2713

2713

原创 Orcad Capture不同页之间的电气连接以及分页符的使用

由于有时原理图有多页,且需要将不同页某些网络之间构成电气连接,需要放置Off-Page Connector,如下图所示:放置后如下图所示,注意要构成电气连接的不同页之间都要放置下面相同分页符,才会构成网络连接如果要观察哪两页构成分页符的电气连接,选中dsn文件,点击tools中的Annotate,如下图所示:如果出现下述错误,说明不同的原理图页之间存在相同的页码,双击右下角的title,修改page count和page number修改完成之后,正常情况下如下图所示:...

2021-02-14 09:42:17

16883

16883

原创 Cadence 17.4制作椭圆形钻孔封装

打开Padstack Editor 17.4,在start中选择如下所示:在drill中输入钻孔的长轴和短轴大小:在design layers中输入如下:上图中的红色框中的值参考如下:阻焊层在regular pad的基础上增加0.15mm,如下图所示...

2021-02-10 18:15:26

3446

3446

2

2

原创 贴片SMD制作PCB封装详细设计规范和步骤

以芯片AD8138为例,下图是芯片封装手册该类的引脚补偿规范如下所示:补偿前:由图一可知,图二中A = 6.2mm;T = 1.27mm;w = 0.51mm补偿后图形:补偿规范如下图所示:长度:为了计算方便,以后对这种封装都取 T1 = T2 = 0.6mm;则补偿后的焊盘长度 X = 1.27mm + 0.6mm +0.6mm = 2.47mm宽度:由于过多补偿焊盘宽度会影响焊盘间距,故取W1 = W1 = 0.1mm(如果焊盘间距本身比较小于0.5mm,可以总共补偿0.1mm,即W

2021-02-09 08:41:37

5437

5437

开关电源纹波以及噪声抑制

2015-05-21

AT指令使用示例_v0.2

2017-03-15

Altium-Designer画元件封装

2017-03-15

交大考研复试-口语

2017-03-15

空空如也

TA创建的收藏夹 TA关注的收藏夹

TA关注的人

RSS订阅

RSS订阅