一,SPI总线的构成及信号类型

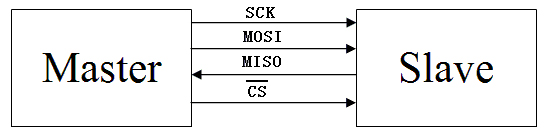

SPI总线只需四条线(如图1所示)就可以完成MCU与各种外围器件的通讯:

1)MOSI – Master数据输出,Slave数据输入

2)MISO – Master数据输入,Slave数据输出

3)SCK – 时钟信号,由Master产生

4)/CS – Slave使能信号,由Master控制。

在一个SPI时钟周期内,会完成如下操作:

1) Master通过MOSI线发送1位数据,同时Slave通过MOSI线读取这1位数据

2) Slave通过MISO线发送1位数据,同时Master通过MISO线读取这1位数据

Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first的方式依次移出Master寄存器和Slave寄存器,并且依次移入Slave寄存器和Master寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first

本文详细介绍了FPGA如何通过SPI总线与AD7606 ADC芯片进行通信,包括SPI总线的工作原理、AD7606的功能特性以及在FPGA中的SPI程序设计,涉及时钟单元、复位信号、采样周期计数器和状态机等关键环节。

本文详细介绍了FPGA如何通过SPI总线与AD7606 ADC芯片进行通信,包括SPI总线的工作原理、AD7606的功能特性以及在FPGA中的SPI程序设计,涉及时钟单元、复位信号、采样周期计数器和状态机等关键环节。

订阅专栏 解锁全文

订阅专栏 解锁全文

244

244

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?