前面写过一个74ls165并转串的程序,但实际用了2块165级联成16位的并转串,为了布线是的方便,就把并行输入的数据打乱了,现在要调整回去,可以借鉴下面的程序

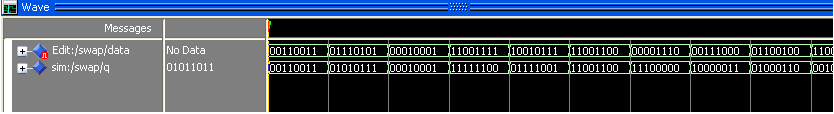

仿真结果

PS:还有些其他的问题没有像明白,慢慢想了

前面写过一个74ls165并转串的程序,但实际用了2块165级联成16位的并转串,为了布线是的方便,就把并行输入的数据打乱了,现在要调整回去,可以借鉴下面的程序

仿真结果

PS:还有些其他的问题没有像明白,慢慢想了

446

446

5238

5238

6807

6807

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?