URL: http://www.eefocus.com/spencer/blog/12-06/280562_0390e.html

PlanAhead这个软件出现在ISE工具包里已经很久了。具体是什么时候集成进去的,我也不去深究了。但是,在ISE12里,PlanAhead的功能出现了很大的变化,不再仅仅是过去的约束软件,而是加入了RTL Design(Synthesize),Netlist Design(Implement),等传统上Project Navigator中的功能。现在,在PlanAhead中即可进行全部的FPGA设计。据称,Xilinx可能在14或者以后的版本中,取消Project Navigator。那么本文就着重的说说PlanAhead的功能。

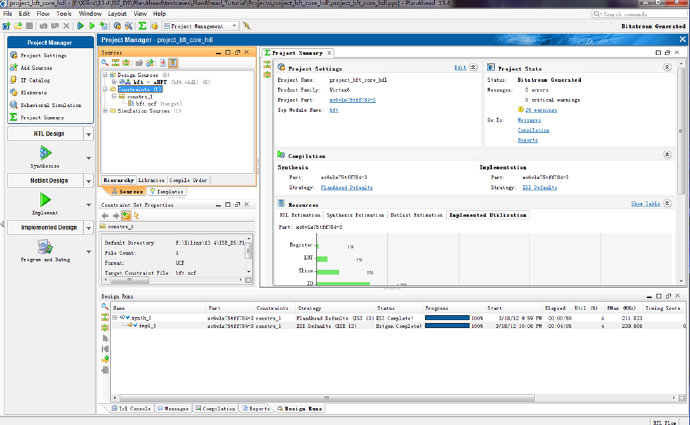

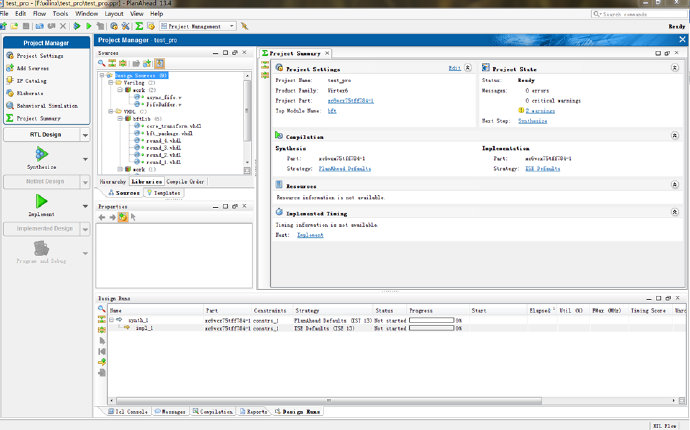

图 1 PlanAhead界面

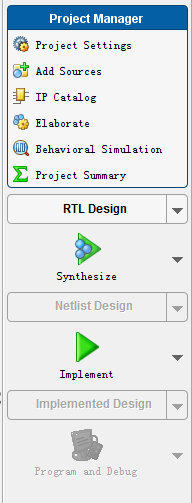

图2所示,是PlanAhead的左边工具栏。

图 2 PlanAhead左边栏

上面的Project Manager用于综合管理工程文档。Add Sources创建、管理源文件;IP Catalog创建、管理IPcore的工程设定。Elaborate显示RTL图,并可以实现资源和功率的估计等等(在Synthesize之前,提高速度)。

RTL Design与上面的Elaborate相同,都是打开RTL Design的功能。

Synthesize是运行Xilinx 的 XST Synthesis,综合工程。

Netlist Design用来配置已经综合过的工程,包括显示综合过的RTL图,估计资源占用,配置约束,时序仿真等等。

Implement执行ISE Implementation。

Implemented Design观察时序和布局结果,并可以优化约束。

Program and Debug按钮,用来生成烧写文件,启动ChipScope,iMPACT。

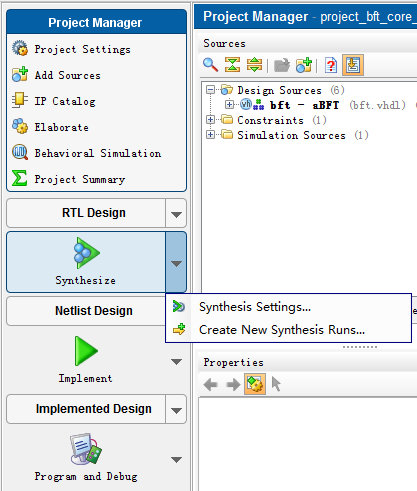

我们再进一步展开几个执行按钮的下拉菜单。如图3所示。

图 3 Synthesize 的下拉菜单

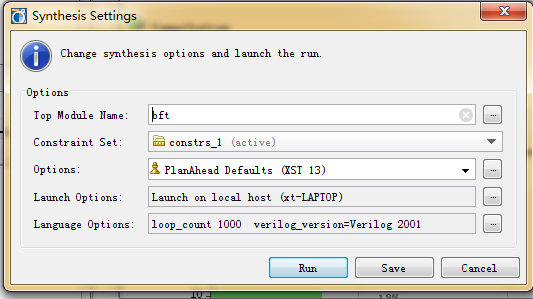

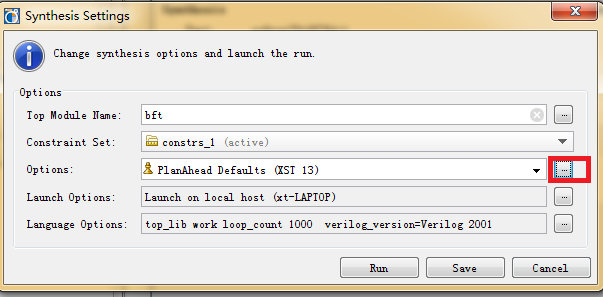

进入到Synthesis Setting,得到图4。

图 4 Synthesis Setting 界面

这里面可以选择使用的约束集合(在add sources里添加约束集合);在options里应用不同的综合选项综合。

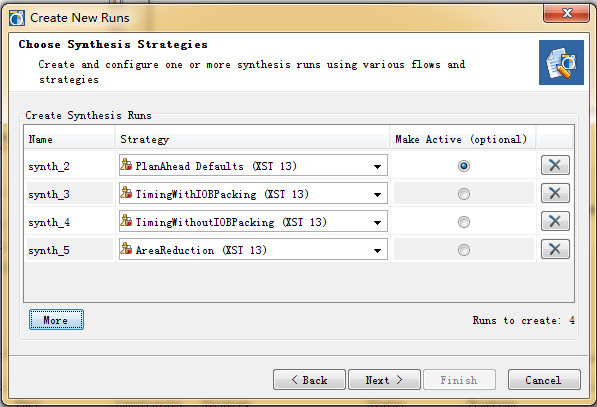

图 5 Create Multiple Runs界面

这里面建立的多个synthesis可以同步运行,充分利用多核cpu的优势。而这些多个synthesis,可以是有不同的device,或者不同的Constraint sets。

下面通过一个例子说明PlanAhead如何创建工程。

图6所示是PlanAhead的启动界面。

图 6 PlanAhead界面

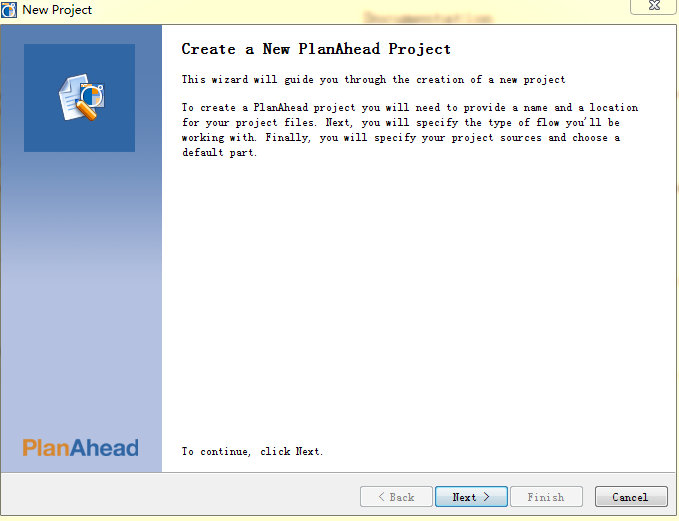

选择Create New Project,进入新建工程界面,如图7所示。

图 7 New Project

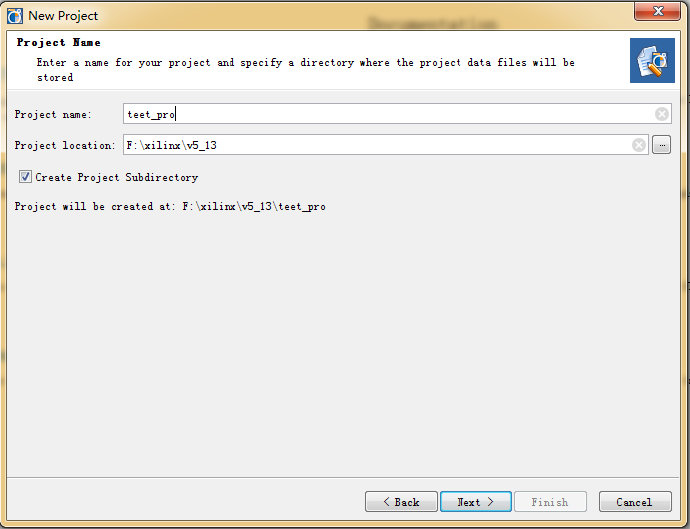

下面是选择工程名和位置,如图8。

图 8 New Project

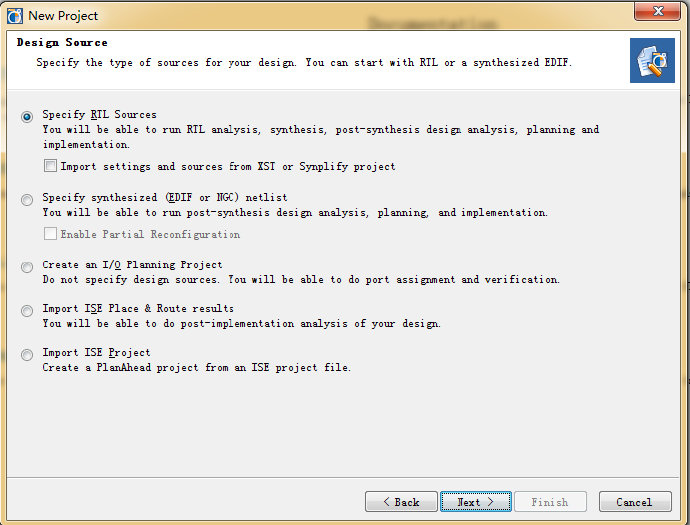

下面是选择Design Source,如图9。

图 9 Design Source

这里我们看到5个选项。这5个选项对应着不同的设计层次。

第一个Specify RTL Sources,是导入RTL级的设计源文件,包括Verilog、VHDL代码、库,还有Xilinx IPCORE等等。是最开始的设计文件。

第二个Specify Synthesized(Edif or NGC)netlist,是导入已经综合过的网表文件,做分析、约束和布局布线。

第三个Create an IO Planning Project,这个选项就是产生一个管脚约束文件,不做其他的事情。即是老版本的PA做的事情。

第四个Import ISE Place& Route Results,导入已经布局布线后的工程,作分析和优化布局。

第五个Import ISE Project,直接导入ISE的工程。

我们现在选择第一个,直接设计RTL文件。

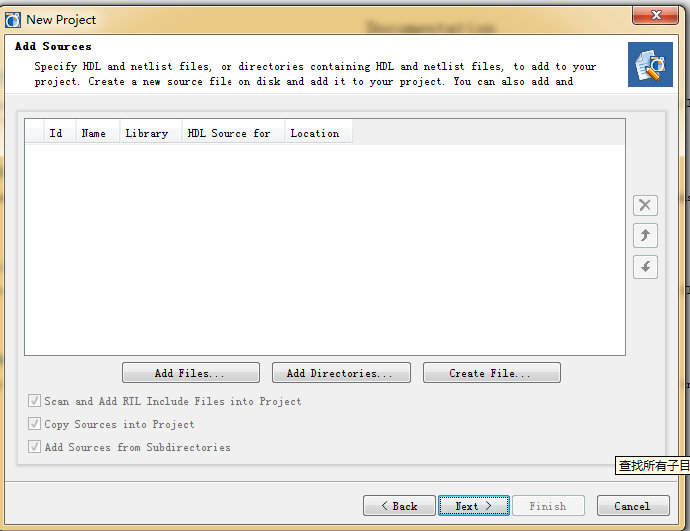

图10所示的是导入源文件的界面。

图 10 Add Sources

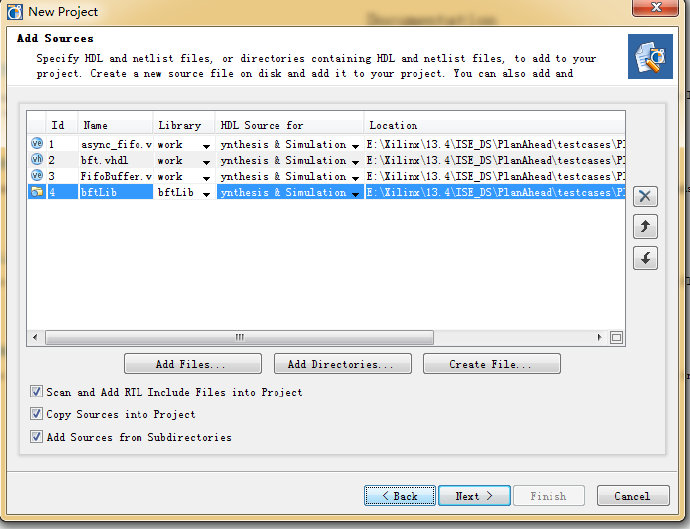

这里我们直接导入PA的一个示例工程的源代码,位置是ISE_DS\PlanAhead\testcases\PlanAhead_Tutorial\Projects\project_bft_core_hdl\project_bft_core_hdl.srcs\sources_1\imports,里面hdl下面的文件作为文件导入进work lib,bftLib直接作为目录导入,修改library为bftLib。结果如图11所示。

图 11 Added Sources

后面的添加IPcore直接略过,下面是添加约束文件。约束文件的位置是ISE_DS\PlanAhead\testcases\PlanAhead_Tutorial\Projects\project_bft_core_hdl\project_bft_core_hdl.srcs\constrs_1\imports\Sources\bft.ucf。如图12所示。

图 12 Add Constraints

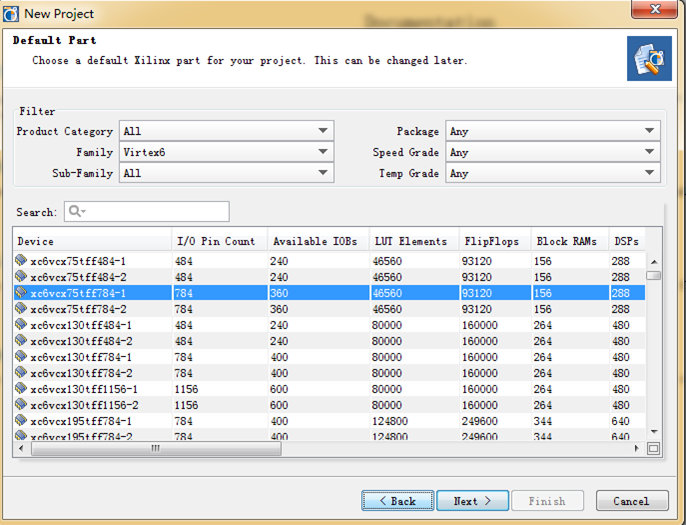

然后是选择器件,我们选择Vertix-6 xc6vcx75tff784-1器件,如图13。

图 13 Device

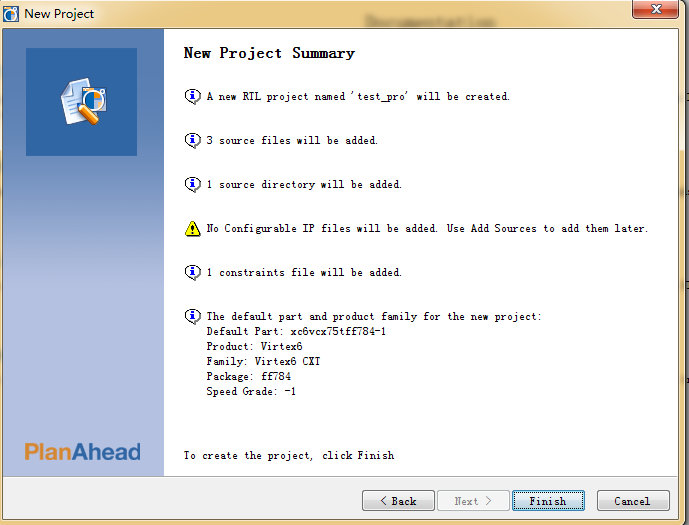

至此,工程建立完毕,显示Project Summary,如图14。

图 14 Project Summary

PlanAhead的界面如图15。

图 15 PlanAhead

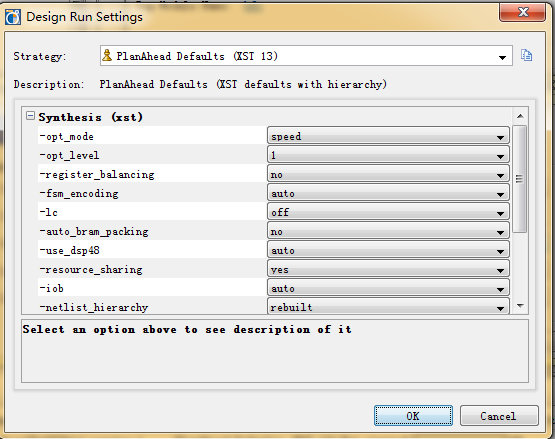

下面开始综合工程,在Synthesize右边的下拉菜单中,选择Synthesize setting,图16。选择options右边的按钮,进入Design Run Setting,图17。

图 16 Synthesize setting

图 17 Design Run Settings

这里面可以配置修改XST的综合选项,还可以使用不同的综合策略来进行综合,我们这里面就不更改设置了,用它默认的配置就可以。之后在Synthesize setting中点击RUN,执行综合。

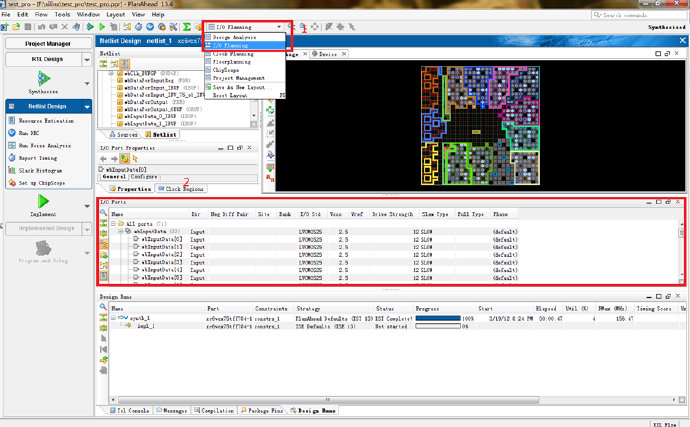

综合完成之后,在Synthesize Completed对话框中选择Open Netlist Design,打开Netlist Design界面。

在上面的下来菜单中选择I/O Planning,打开I/O配置页面,在下面的I/O Ports中,分配管脚。如图18所示。

图 18 I/O Planning

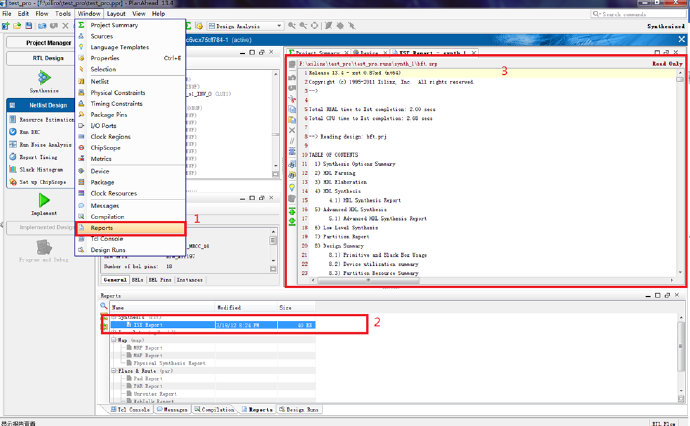

打开菜单栏Windows ->Report,选择 XST Report,可以查看综合报告,如图19。

图 19 XST Report

点击左侧的Implement,执行布局布线操作。完成之后打开Implemented Design,查看结果。

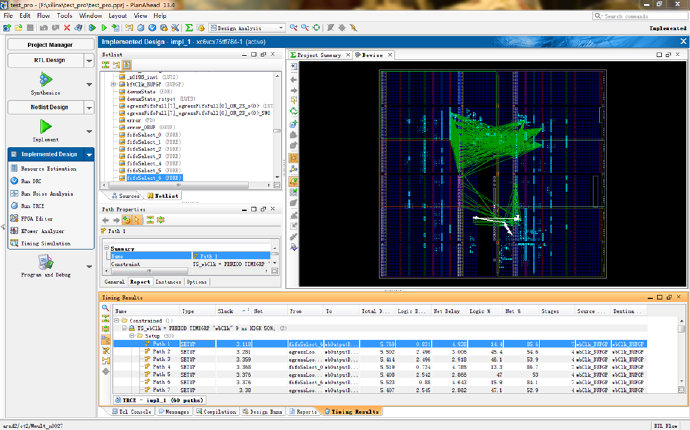

在下面选择Timing Results,可以看到时序分析的结果。如图20。

图 20 Timing Results

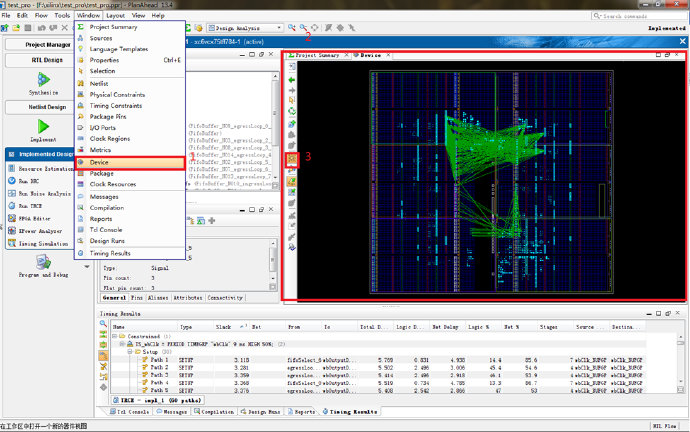

点击Windows -> Device,在Device View的窗口下点击Show/Hide I/O Nets按钮。可以查看器件间的逻辑连接情况。如图21所示。

图 21 I/O Nets

在下面的Timing Results中点击一条路径,可以在Device框中查看到对应的路径,图22。右击path,选择Path Properties,可以查看这条路径经过的元件,图23

图 22 Timing Results

图 23 Path Properties

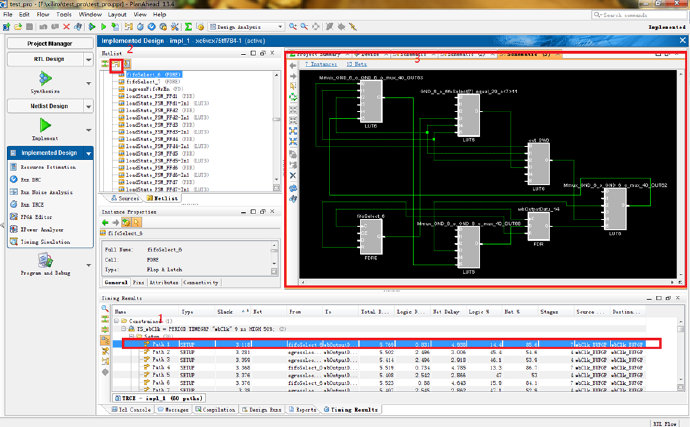

在Timing Result对话框下,点击原理图按钮,可以看到这条路径的原理图,图24。

图 24

6201

6201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?