1.MOS管

MOS管的开关等效电路

2.CMOS

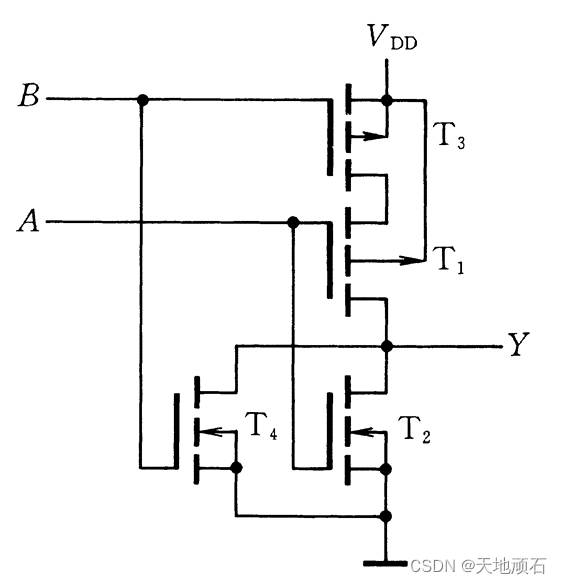

CMOS 反相器(Inverter/非门)是CMOS电路的基本结构形式.

T1是P沟道增强型MOS管,T2是N沟道增强型MOS管.

CMOS 反相器具有较大的噪声容限(输入信号的电平波动范围)、极高的截止内阻、极小的静态电流/功耗以及对噪声和干扰不敏感等优点.

CMOS与非门

CMOS或非门

缺点:

1)输出电阻R受输人端状态的影响,输入状态的不同可以使输出电阻相差4倍之多;

2)输出的高、低电平受输人端数目的影响;

改善:

在输入端、输出端各增设一级反相器,称为缓冲器。

或非门+缓冲器=>与非门

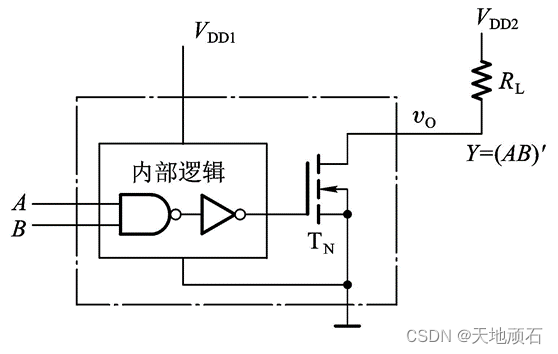

将输出级电路结构改为一个漏极开路输出的MOS管,构成漏极开路输出(Open-Drain Output)门电路,简称OD门。

可将输出并联,实现电平变换、吸收大负载电流以及实现线与连接

利用P沟道MOS 管和N 沟道MOS 管的互补性可以接成如图所示的CMOS 传输门.

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,因总是接在集成电路的输出端, 又称为输出缓冲器( Output Buffer)。

其三态输出受到使能输出端的控制,

当E=1,选通,其输入直接送到输出;

若E=0,缓冲器被阻止,无论输入什么值,输出的总是高阻态,用Z表示。高阻态能使电流降到足够低,与所连的电路断开。

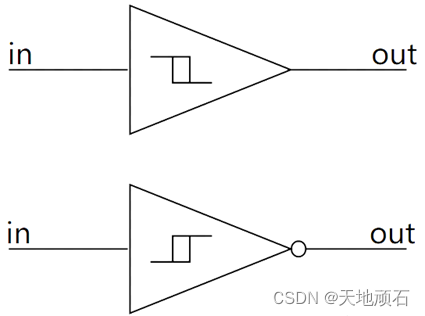

3.施密特触发电路

施密特触发电路(Schmitt Trigger)是脉冲波形变换中经常使用的一种电路, 简称为施密特电路。

1)用于波形变换

2)用于脉冲整形

4.ESD

1 ESD保护原理

ESD保护电路的目的是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁, I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD 低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地箝位保护电路电压。而在这两部分正常工作时,不影响电路的正常工作。

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。由于MOS管与CMOS工艺兼容性好,因此常采用MOS管构造保护电路。

5.CMOS 常用电路

5.1 GND

ESD-NMOS:GGNMOS(Gate Ground NMOS)

不同于常规NMOS,调整Drain与P-sub的掺杂浓度与拓扑结构,栅极接地,在正常工作的情况下GGNMOS处于高阻态,并联在PAD与GND轨间,不会影响电路的正常工作状态。当ESD电流从PAD进入IC后,使整个回路Breakdown Voltage位于ESD Design Window内。

5.2 AVDD

基于RC的ESD检测电路组成的电源ESD钳位电路

5.3 I2C

I2C总线是双向二线制同步串行总线。I2C的端口用的是线与逻辑,采用open drain.

5.4 XSHUTDOWN

复位电路上反相器串联,提高引脚高阻抗特性,使信号隔离。

6.存储电路

寄存器是存储一组数据的电路,结构为一组具有公共时钟信号输入端的触发器

1)用于寄存一组二值代码,N位寄存器由N个触发器组成,可存放一组N位二值代码。

2)只要求其中每个触发器可置1,置0。

存储大量数据的电路,基本结构由存储矩阵和读/写控制电路组成。

从存/取功能分:

RAM、ROM、EEPROM、FLASH

1213

1213

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?