1、简介

每当违背建立和保持时间时,亚稳态就会出现。在以下的情况下,可能违背时序要求:

- 输入信号是异步信号

- 时钟偏移超过容限值

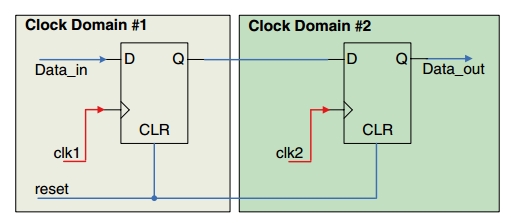

- 信号在两个不同频率或者同频不同相的时钟域下工作

- 组合延时使触发器的输入信号在亚稳态窗口内发生变化

亚稳态会引起过多的传输延时和系统故障。虽然亚稳态不能根除,但是可以减小亚稳态发生的概率。避免亚稳态发生常见方法就是使用同步器。

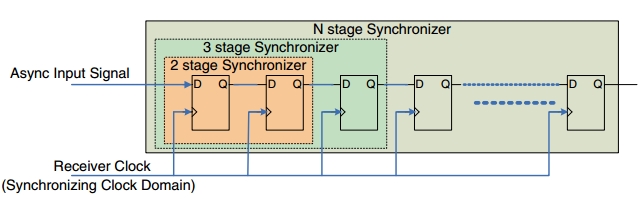

2、使用多级同步器

最常见的方法就是在跨时钟域内的信号后加上同步触发器。该方法是用一个时间周期(不包括第二级触发器的建立时间)来解决第一级同步触发器亚稳态的问题。但是这种方法增加了观察同步逻辑输入的延时。

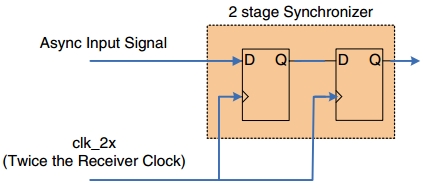

3、使用倍频时钟同步器

多级同步器的局限就是系统需要花费较长的时间去响应异步输入信号。解决办法就是使用倍频时钟作为两个同步触发器的输入时钟。

这两种方法都不能保证同步器阻止亚稳态传播下去,但是可以减小亚稳态发生的概率。

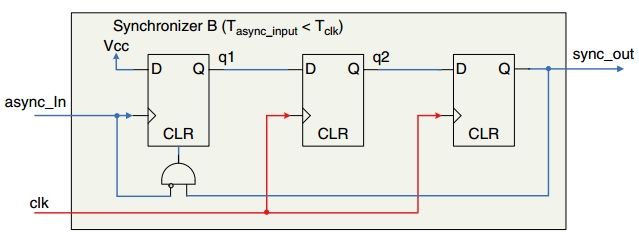

同步器有以下两种类型:

4、建议

在两个异步系统交界的地方亚稳态是不可避免的。但以下建议可以明显减小亚稳态发生的概率:

- 采用同步器

- 采样相应更快的触发器(亚稳态窗口小)

- 降低采样速率

- 避免使用dVdt 低的输入信号

参考资料

1 The Art of Hardware Architecture

2 Understanding Metastability in FPGAs

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?