对于偶次项n分频还是比较容易的如果。如果n是2的整数次幂,即n=2^m,可定义一个[m-1:0]的寄存器counter,对clk计数,分频输出取最高位assign div=counter[m-1]即可。如果不是2的整数次幂,2^(m-1)<n<2^m,也是定义一个[m-1:0]的寄存器counter,计数到n/2-1时,div反转即可。

对于奇数的分频可用以下的方法:

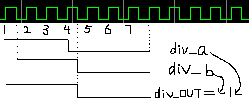

声明两个寄存器cnta和cntb,cnta在clk上升沿div时进行计数,cntb在clk下降沿是进行计数,div_a和div_b在cnta和cntb小于4时为高电平,然后两者或即可得到占空比为50%的七分频电路。

下面是verilog代码:

1 module fenping(clk,rst_n,div_a,div_b,div_out); 2 input clk; 3 input rst_n;4 output div_out; 5 output div_a,div_b; 6 reg[2:0] cnta; 7 always@(posedge clk or negedge rst_n) 8 if(!rst_n) 9 cnta<=0; 10 else if (cnta==3'b110) 11 cnta<=0; 12 else 13 cnta=cnta+1'b1; 14 15 16 reg div_a; 17 always@(posedge clk or negedge rst_n) 18 if(!rst_n) 19 div_a<=0; 20

本文介绍了如何设计一个占空比为50%的七分频电路。通过声明两个寄存器cnta和cntb,在clk的上升沿和下降沿分别计数,当cnta和cntb小于4时,输出高电平,通过或运算得到所需的占空比。同时,指出了原代码中阻塞赋值的问题,并提供了修正后的Verilog代码。

本文介绍了如何设计一个占空比为50%的七分频电路。通过声明两个寄存器cnta和cntb,在clk的上升沿和下降沿分别计数,当cnta和cntb小于4时,输出高电平,通过或运算得到所需的占空比。同时,指出了原代码中阻塞赋值的问题,并提供了修正后的Verilog代码。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

981

981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?