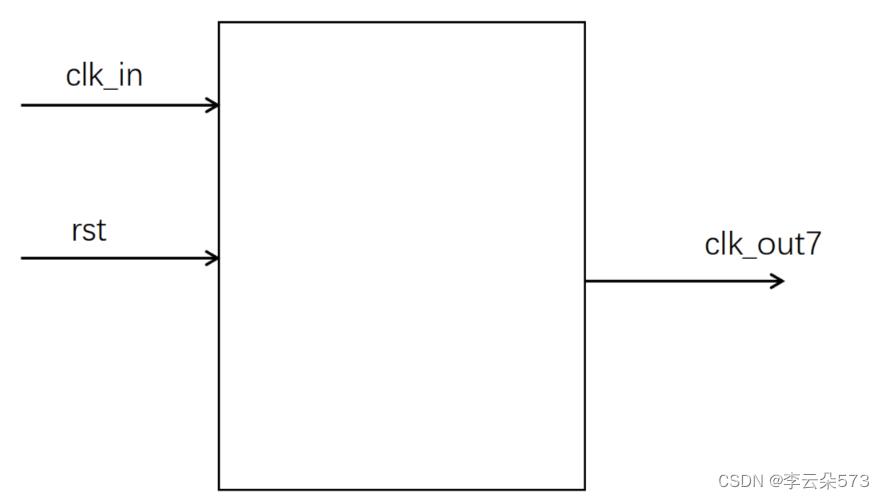

题目

设计一个同时输出7分频的时钟分频器,占空比要求为50%

注意rst为低电平复位

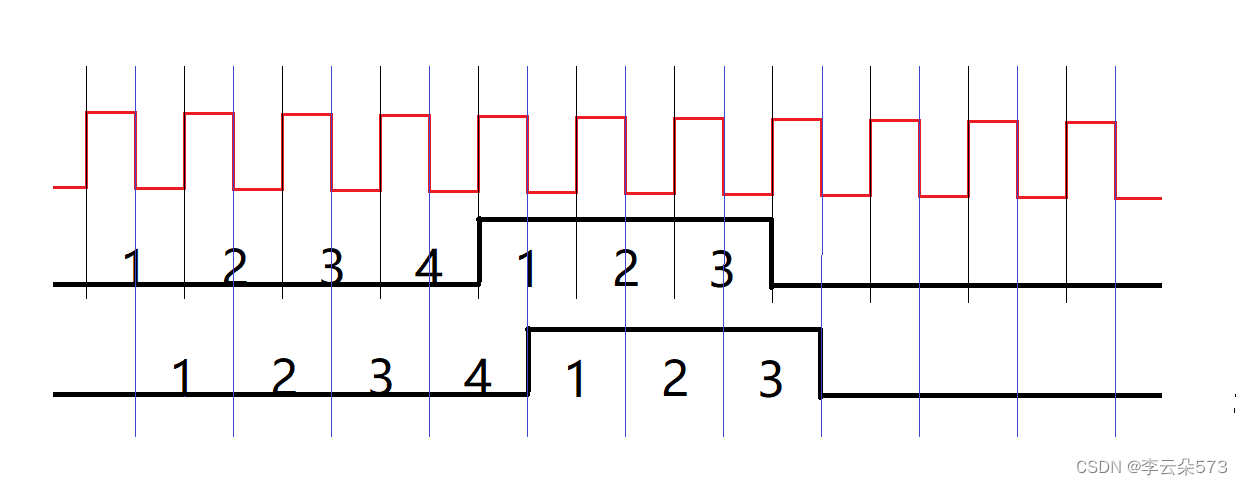

思路

上升沿下降沿分别操纵计数器进行计数产生分频时钟,然后将时钟相或。

rtl

//占空比50%的奇数7分频

module odd_pll(

input wire clk,

input wire rst,

output wire clk_o

);

reg [2:0] pos_cnt;

reg [2:0] neg_cnt;

always@(posedge clk or negedge rst)

if(!rst)

pos_cnt <= 1'b0;

else begin

if(pos_cnt == 3'd6)

pos_cnt <= 3'd0;

else

pos_cnt <= pos_cnt + 1'b1;

end

always@(negedge clk or negedge rst)

if(!rst)

neg_cnt <= 1'b0;

else begin

if(neg_cnt == 3'd6)

neg_cnt <= 3'd0;

else

neg_cnt <= neg_cnt + 1'b1;

end

reg pos_clk;

reg neg_clk;

always@(posedge clk or negedge rst)

if(!rst)

pos_clk <= 1'b0;

else begin

if(pos_cnt >= 3'd4)

pos_clk <= 1'b1;

else

pos_clk <= 1'b0;

end

always@(negedge clk or negedge rst)

if(!rst)

neg_clk <= 1'b0;

else begin

if(neg_cnt >= 3'd4)

neg_clk <= 1'b1;

else

neg_clk <= 1'b0;

end

assign clk_o = neg_clk || pos_clk;

endmodule

module tb;

reg clk;

reg rst;

odd_pll inst1(

.clk(clk),

.rst(rst),

.clk_o()

);

initial begin clk = 1'b0; forever begin #10; clk = ~clk; end end

initial begin rst = 1'b0; #25; rst = 1'b1; end

initial begin #5000; $stop; end

endmodule

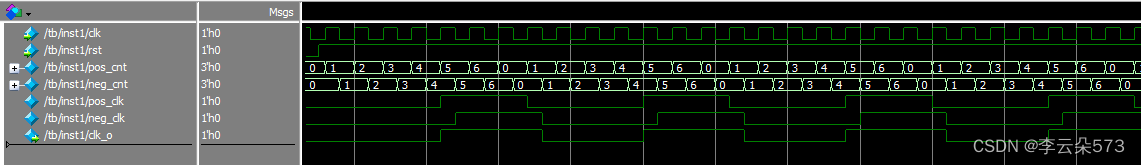

结果波形

981

981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?